го блока управления, второй БХОД двенадцатого элемента И общего бло-i ка управления соединен с первым входом четырнадцатого элемента И общего блока управления и выходом конца формирователя блока поразрядного кодирования, выход восьмого элемента И общего блока управления подключен к первым входам пятнадцатого элемента И и четвертого элемента ИЛИ обще™ го блока управленияJ второй вход которого соединен с выходом двенадцатого элемента И и первым входом шестнадцатого элемента И общего блока управления, а выход подключен к первому входу пятого элемента ИЛИ общего блока управления и управляющему входу генератора функций, второй вход пятого элемента ИЛИ общего блока управления соединен с выходом элемента ИЛИ-НЕ и первым вхолом семнадцатого элемента И общего блока управления, а выход подключен к второму входу пятого элемента И общего блока управления, выход которого соединен с вторыми входами пятнадцатого, шестнадцатого и семнадцатого элементов И и счетным входом триггера общего блока управления, первьй и второй входы первого элемента ИСКЛЮЧАЮЦЕЕ ШИ общего блока управления подключены соответственно к выходу старшего разряда блока поразрядного кодирования и к выходу знакового разряда сумматора, а вы-ход соединен с вторыми входами шее- того и седьмого элементов И общего блока управления, третьи входы которых подключены к выходу элемента ИЛИ, второй вход десятого элемента И общего блока управления соединен со знаковым разрядом первой группы входов преобразователя коорди-/ нат и первьм информационнььм входом коммутатора5 второй вход одиннадцатого элемента И общего блока управления подключен к знаковому разряду второй группы входов преобразователя координат, выходы десятого и одиннадцатого элементов И общего блока управления соединены соответственно с первыми входами второго и третьего элементов ИСКПЮЧАКЩЕЕ ИЛИ общего блока управления, вторые входы которых соединены соответственно с выхоами знаковых разрядов выходов синуса и косинуса генератора функций, выход второго элемента ИСКЛЮЧАЩЕЕ

ИЛИ общего блока управления подключен к второму входу тринадцатого элемента И общего блока управления, выход которого соединен с входом управления вьщачей первого преобразователя кода, выход третьего элемента ИСКЛЮЧАЮЩЕЕ РШИ общего блока управления соединен с первым входом четвертого элемента ИСКЛЮЧАЩЕЕ ИЛИ общего блока управления, второй вход которого подключен к выходу девятого элемента И общего блока управления, а выход соединен с вторым входом второго элемента ИЛИ общего блока управления, выход которого подключен к второму входу четырнадцатого элемента И общего блока управления, выход которого соединен с входом управлени выдачей второго преобразователя кода выход первого элемента ИЛИ общего блока управления подключен к входу установки режима первого преобразователя кода и к второму входу третьего элемента МИ общего блока управления выход которого соединен с входом установки режима второго преобразователя кода, выходы четвертого, пятнадцатого, шестнадцатого и семнадцатого элементов И общего блока управления являются группой сигнальных выходов преобразователя координат, выходы второго третьего, шестого и седьмого элементов И общего блока управления подключены соответственно к входам записи, установки, уменьшения и уве.личения блока поразрядного кодирования, кодовьй выход которого соединен с входом аргумента генератора функци и является первьм кодовым выходом преобразователя координат, выход элемента ИСКЛЮЧАЩЕЕ I-fflH подключен к второ1 у информационному входу коммутатора, третий и четвертьш информационные входы ком.1утатора соединены со старшими разрядами третьей группы входов преобразователя координат, первый и второй информационные выходы коммутатора и младшие разряды третьей труппы входов устройства подключены к кодовым входам блQкa поразрядного кодирования, первьй и второй управляющие входы дешифратора являются входами задания режима работы преобразователя координат, информационные входы первого и второго преобразователей кода соединены соответственно с выходами первого и второго умножителей, кодовые выходы первого

и второго преобразователей кода подключены соответственно к первым и вторым информационным входам сумматора и являются соответственно вторым и третьим информационными выходами преобразователя координат, выход сумматора соединен с кодовым входом элемента ИЛИ и является четвертым информационным выходом преобразователя координат, причем каждьй из преобразователей кода содержит сумматор группу элементов ИСКЛЮЧАЮЩЕЕ ШШ, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первьм вход которого подключен к первому входу элемента И преобразователя кода и является входом управления вьщачей преобразователя кода, вход установки режима преобразователя кода соединен с вторым входом элемента И преобразователя кода, выход- которого подключен к входу переноса сумматора и к первым входам группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ преобразователя кода, вторые входы которой соединены с информационным входом преобразователя кода, а выходы подключены к первым информационным входам сумматора преобразователя кода, вторые информационные входы которого соединены с шиной Земля преобразователя координат, вькод переноса сумматора преобразователя кода подключен к второму входу элемента ИСКПЮЧАЩЕЕ ИЛИ преобразователя кода, выход которого и выход сумматора подключены к кодовому выходу преобразователя кода, причем блок поразрядного кодирования содержит сдвиговьй регистр, регистр аргумента, дешифратор и элемент ИЛИ,

первый вход которого подключен к входу записи младших разрядов регистра аргумента и входу записи блока поразрядного кодирования, второй вход элемента ИЛИ блока поразрядного кодирования соединен с входом начальной установки блока поразрядного кодирования, а выход подключен к входу записи старших разрядов регистра аргумента и входом записи сдвигового регистра, вход сдвига которого соединен с тактовым входом блока поразрядного кодирования, информационньй вход сдвигового регистра подключен к шине 100...О преобразователя координат, а п входов сдвигового регистра ( младший разряд, п+1 - старший разряд соединены с информационными входами дешифратора блока поразрядного кодирования, первый и второй входы стробов подключены соответственно к входам уменьшения и увеличения блока поразрядного кодирования, а выходы - соответствующим образом к входам установки в 1 и О младших разрядов регистра аргумента блока поразрядного кодирования, выходы которого соединены с кодовым выходом блока поразрядного кодирования, информационные входы регистра аргумента подключены к кодовым.входам блока поразрядного кодирования, младший и старший разряды сдвигового регистра соединены соответственно с выходами начала и конца формирования блока поразрядного кодирования, выход старш его разряда которого подключен к выходу старшего разряда регистра аргумента блока поразрядного кодирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

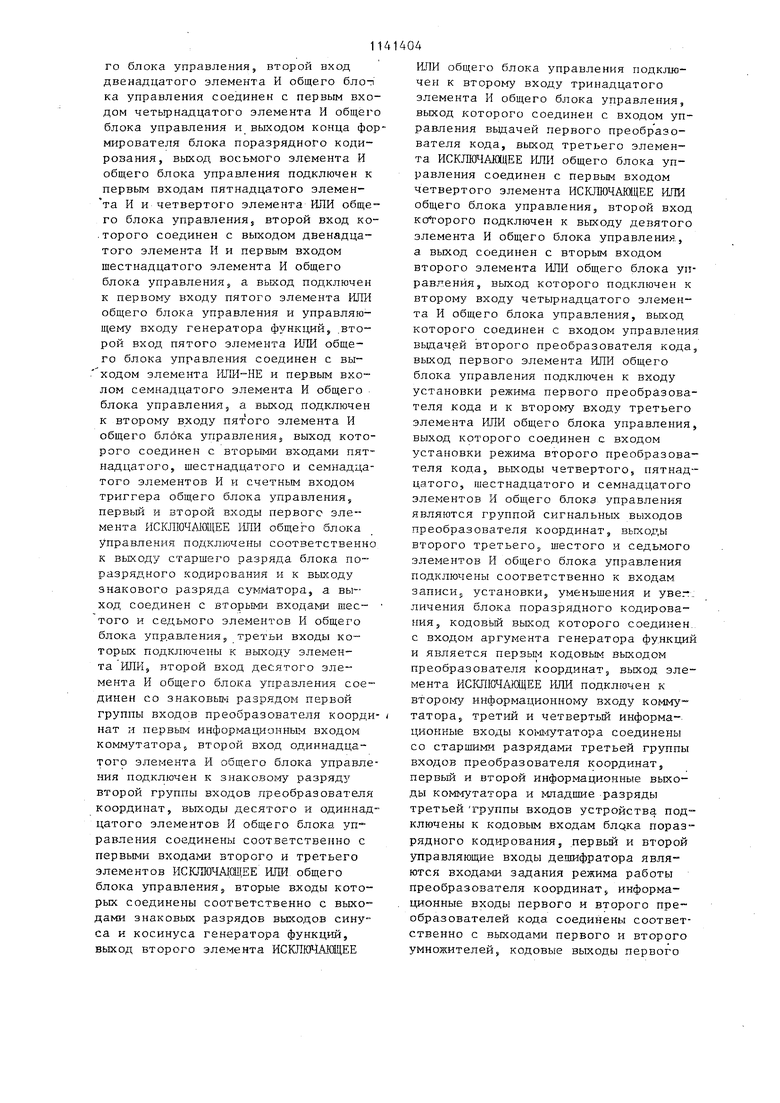

ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ, содержащий первьп и второй умножители, первьй элемент НСКПЮЧАЩЕЕ HJDi, блок поразрядного кодирования, генератор функций и общий блок управления, причем входы знаковых разрядов первой и второй групп входов преобразователя координат соединены с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, выходы синуса и косинуса генератора функций подключены соответственно к первым входам первого и второго умножителей, вторые входы которьсх являются соответственно первой и второй группами информахщонных входов преобразователя координат, отличающийся тем, что, с целью расширения функциональных возможностей за счет вьтолнения операции преобразования прямоугольных координат при повороте осей, в преобразователь координат дополнительно введены кoм yтaтop, дешифратор, первьй и второй преобразователи кода, сумматор и элемент ИШ1, общий блок управления содержит семнадцать элементов И, пять элементов HJDI, элемент {-ШИ-НЕ, четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер, вход запуска преобразователя координат соединен с первыми входами первого, второго, третьего элементов И и входом установки в 1 три1- гера общего блока управления, выход которого, подключен к втором входу первого элементаИ общего блока упpaвJteния, третий вход которого соединен с входом тактовых иьтульсов преобразователя координат, а выход подключен к первым входам четвертого пятого,шестого и седьмого элементов И о бщего блока управления и к тактовому входу блока поразрядно.го кодирования, второй вход четвертого элемента И об(Л щего блока управления соединен с первыми входами восьмого, девятого, десятого и одиннадцатого элементов И, элемента 1ШИ-НЕ, первого элемента ИЛИ общего блока управления и с первым выходом деишфратора, третий вход чет;вертого элемента И общего блока уп- 4 .равления подключен к вторым входам восьмого и девятого элементов И общего блока управления и к выходу О k( признака начала формирования блока поразрядного кодирования, второй вход второго элемента И общего блока управления соединен с вторыми входами третьего элемента И и элемен- та ИЛИ-ПЕ, первыми входами двенадца- того и тринадцатого элементов И, второго и третьего элементов 1ШИ общего блока управления, вторым выходом дешифратора и управлякнцим входом коммутатора, третий информационный выход дешифратора подключен к второму входу первого элемента ИЛИ обще

1

Изобретение относится к вычислительной технике и предназначено для вьшолнения по кодам входных коорди-;; нат измеряемой величины следующих трех операций: преобразование прямоугольных координат при повороте осей преобразование прямоугольных координат в полярные координаты; преобразование полярных координат в прямоуголь ные .координаты.

Известны цифровые преобразователи координат C1J и 2}

Основными недостатками этих преобразователей координат являются низкое быстродействие и ограниченность функциональньк возможностей, обусловленные способом обработки информации и недостаточно полным использованием функциональных возможностей отдельных узлов этих устройст 31 Наиболее близким по технической сущности к иэov1peтeнию является цифровой преобразователь координат, содержащий первый и второй умножители, элемент ИСКПЮЧАЩЕЕ ИЛИ, блок поразрядного кодирования, генератор функций, первый блок управления, первый, второй и третий кодовые входы, управ ляющие входы, тактовьш вход и вход запуска, причем первьш блок управления имеет девять входов, выходы импульсов съема результатов операций, управляющий выход, соединенньш с управляющим входом генератора функций, и синхронизирующие выходы, подключен ные к управляющим входам блока пораз рядного кодирования 5 первьш и второй управляющие выходы и выход второго старшего разряда которого соединены .соответственно с первыми тремя входами первого блока управления, четвертый и пятьм входы которого подклю чены соответственнц к входу запуска и тактовому входу, входы знаковых разрядов второго и третьего кодовых входов - к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первьй и второй кодовые выходы генератора функций - с входами первых сомножителей первого и вто рого умножителей соответственно t lОсновным недостатком известного преобразователя является ограниченность функциональных возможностей (он может выполнять только вторую и третью операции преобразования координат), обусловленная недостаточно полным использованием функциональных возможностей блока поразрядного коди рования и генератора функций Цель изобретения - расширение фун кциональных возможностей за счет выполнения операции преобразования пря моугольных координат лри повороте осей. Поставленная цель достигается теМ что в цифровой преобразователь координат, содержащий первый и второй ум ножители, .элемент ИСКПЮЧАЩЕЕ КИИ, блок поразрядного кодирования, генератор функций и общий блок управления, причем входы знаковых разрядов первой и второй групп входов устройства соединены с первым и вторым вхо 4 дани первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, выходы синуса и косинуса ге})ератора функций подключены соответственно к первым входам первого и второго умножителей, вторые входы которых являются соответственно первой и второй группами информационных входов устройства, дополнительно введены коммутатор, дешифратор, первый и второй преобразователи коДа, сумматор и элемент ИЛИ, а общий блок управления содержит семнадцать элементов И, пять элементов ИЛИ, элемент ИЛИ-НЕ, четыре элемента ИСКЛЮЧАЩЕЕ ИЛИ и триггер, вход запуска устройства соединен с первыми входами первого, второго и третьего элементов И и входом установки в 1 триггера общего блока управления, выход которого подключен к второму входу первого элемента И общего блока управления, третьим входом соединенного с входом тактовых импульсов устройства, а выходом подключенного к первым входам четвертого, пятого, шестого и седьмого элементов И общего блока управления и к тактовому входу блока поразрядного кодирования, второй вход четвертого элемента И общего блока управления соединен с первыми входами восьмого, девятого, десятого и одиннадцатого элементов И, элемента ИЛИ-НЕ,первого элемента ИЛИ общего блока управления и с первым выходом дешифратора, третий вход четвертого элемента И общего блока управления подключен к вторым входам восьмого и девятого элементов И общего блока управления;и к выходу признака начала формирования блока поразрядного кодирования, второй вход второго элемента И .общего блока управления соединен с вторыми входами третьего элемента И и элемента ИЛИ-НЕ, первыми входами двенадцатого и тринадцатого элементов И, втррого и третьего элементов ИЛИ общего блока управления, вторым выходом дешифратора и управляющим входом коммутатора, третий информадионньй выход дешифратора подключен к второму входу первого элемента Ш1И общего блока управления, второй вход двенадцатого элемента И блока управления соединен с первым входом четырнадцатого элемента И общего блока управления и выходом конца формнрования блока поразрядного кодирования, выход восьмого элемента И общего блока управления подключен к первым входам пятнадцатого элемента Ни четвертого элемента ШШ общего блока управления, - второй вход которого соединен с выходом двенадцатого элемента И и первым входом шестнадцатого элемента И общего блока управления, а выход подключен к перйому ду пятого элемента ИПИ общего блока управления и управляющему входу генератора функций, второй вход пятого элемента ИЛИ общего блока управле ния соединен с выходом элемента ИЛИНЕ и первым входом семнадцатого элемента И общего блока управления, а выход подключен к второму входу пятого элемента И общего блока управления, выход которого соединен с I . вторыми входами пятнадцатого, шестнадцатого и семнадцатого элементов И и счетным входом триггера общего блока управления, первьш и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ общего блока управления подключены соответственно к выходу старшего разряда блока поразрядного кодирования и к выходу знакового разряда сумматора, а выход соединен с вторыми входами шестого и седьмого элементов И общего блока управления, третьи входы которых подключены к выходу элемента ИЛИ, второй вход десятого элемента И общего блока уп равления соединен со знаковым разря дом первой группы входов устройства и первым информационным входом .коммутатора, второй вход одиннадцатого элемента И общего блока управления подключен к знаковому разряду второй группы входов устройства, выходы десятого и одиннадцатого элементов И общего блока управления соеди нены соответственно с первыми входа ми второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ общего блока управления, вторые входы которых соединены соответственно с выходами знаковых разрядов выходов синуса и косинуса генератора функций, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ общего бло ка управления подключен к второму входу тринадцатого элемента И общего блока управления, выход которого соединен с входом управления вьщаче первого преобразователя кода, выход третьего элемента ИСЮ1ЮЧАШ.ЕЕ ИПИ 114 4 общего блока управления соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ общего блока управления, второй вход которого подключен к выходу девятого элемента И. общего блока управления, а выход соединен с вторым входом второго элемента ИЛИ общего блока управления, выход которого подключен к второму входу четырнадцатого элемента И об- щего блока управления, выход которого соединен с входом управления выдачей второго преобразователя кода, выход первого элемента ИЛИ общего блока управления подключен к входу установки режима первого преобразователя кода и к второму входу третьего элемента ИЛИ общего блока управления, выход которого соединен с входом установки режима второго преобразователя кода, выходы четвертогопятнадцатого, шестнадцатого и семнадцатого элементов И общего блока управления являются группой сигнальных выходов устройства, выходы второго, третьего, шестого и седьмого элемен-i тов И общего блока управления подключены соответственно к входам записи, установки, уменьшения и увеличения кода блока поразрядного кодирования кодовый выход которого соединен с входом аргумента генератора функций и является первым кодовым выходом устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму информационному входу коммутатора, третий и четвертый информационные входы коммутатора соединены со старшими разрядами третьей группы входов устройства, первьй и второй информационные выходы коммутатора и младшие разряды третьей группы входов устройства подключены к кодовым входам блока поразрядного кодирования, первьш и второй управляющие входы дешифратора являются входами задания режима работы устройства, информационные входы первого и второго преобразователей кода соединены соответственно с выходами первого и второго умножителей, кодовые выходы первого и втюрого преобразователей кода подключены соответственно к первым и вторым информационным входам сумматора и являются соответственно вторым и третьим информационными выходами устройства, выход сумматора соединен с кодовым входом элемента ШШ и яв ляется четвертым и 1формационным выходом устройства, причем каждый из преобразователей кода содержит сумматор, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И и элемент ИСКЛЮЧАЩЕЕ ИЛИ, первый вход которого пол ключей к первому входу элементов И преобразователя кода и является входом управления вьщачей преобразователя кода, вход установки режима преобразователя кода соединен с вторым входом элемента И преобразователя кода, выход которого подключен к входу переноса сумматора и к первым входам группы элементов ИСКПЮЧАКЩЕЕ ИЛИ преобразователя кода, вторые входы которой соединены с информационным входом преобразователя кода, а выходы подключены к первым информа,-. дионным входам сумматора преобразователя кода, вторые информационные входы которого соединены с шиной Земля устройства, выход переноса сумматора, преобразователя кода подключен к второму входу элемента ИСКЛЮЧАЩЕЕ РШИ преобразователя кода, выход которого и выход сумматора под ключены к кодовому выходу преобразователя кода, причем блок поразрядного кодирования содержит сдвиговьш регистр, регистр аргумента, дешифратор и элемент ИЛИ, первый вход которого подключен к входу записи младших разрядов регистра аргумента и входу записи блока поразрядного ко- дирования, второй вход элемента ИЛИ блока поразрядного кодирования соеди нен с входом установки блока поразрядного кодирования, а выход подключен к входу записи двух стариих раз рядов регистра аргумента и входу записи сдвигового регистра, вход сдви га которого соединен с тактовым вхо дом блока поразрядного кодированияs информационный вход сдвигового регистра подключен к шине 100...О устройства, а п выходов сдвигового регистра ( - младший разряд, п+1 старший разряд) соединены с информа ционными входами дешифратора блока поразрядного кодирования, первьй и второй входы стробов подключены со ответственно к входам уменьшения и увеличения блока поразрядного кодир вания, а выходы - соответствующим об-55 жит

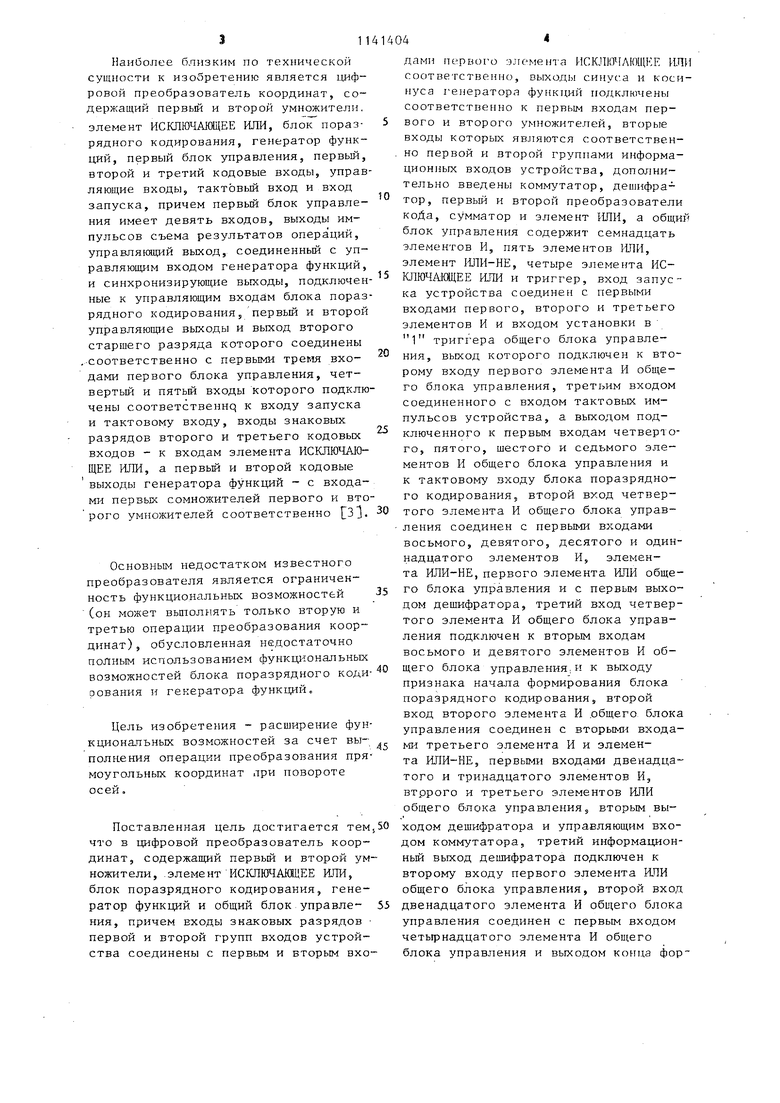

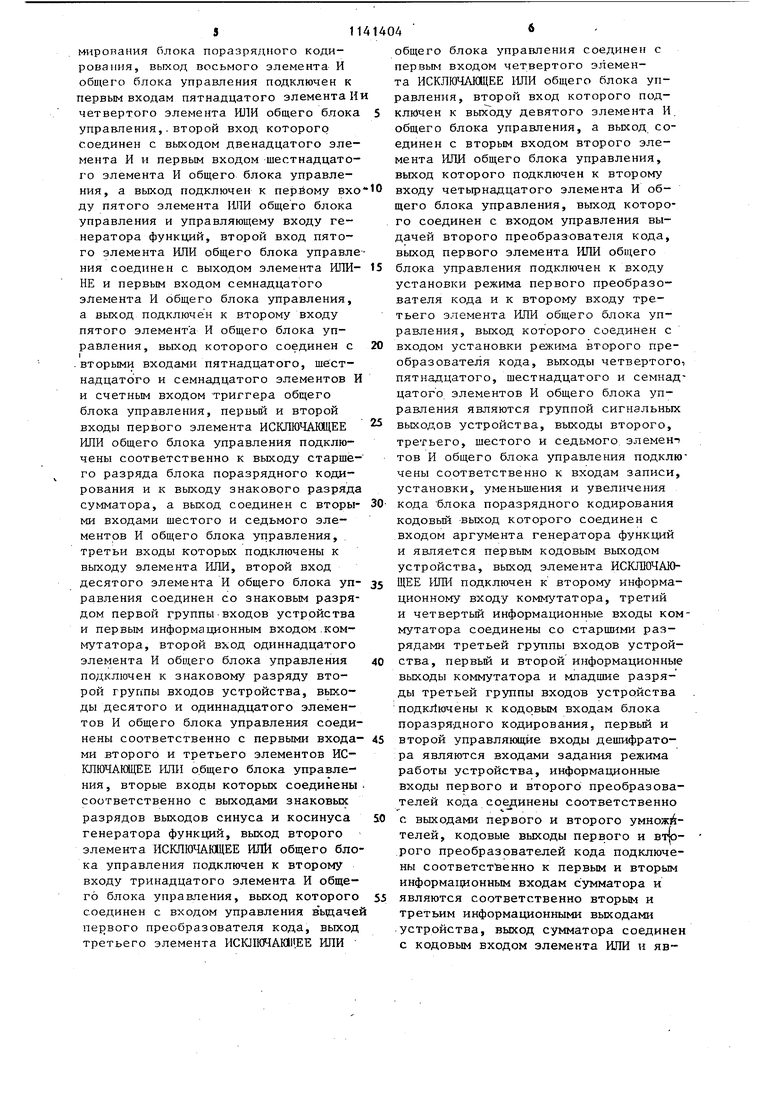

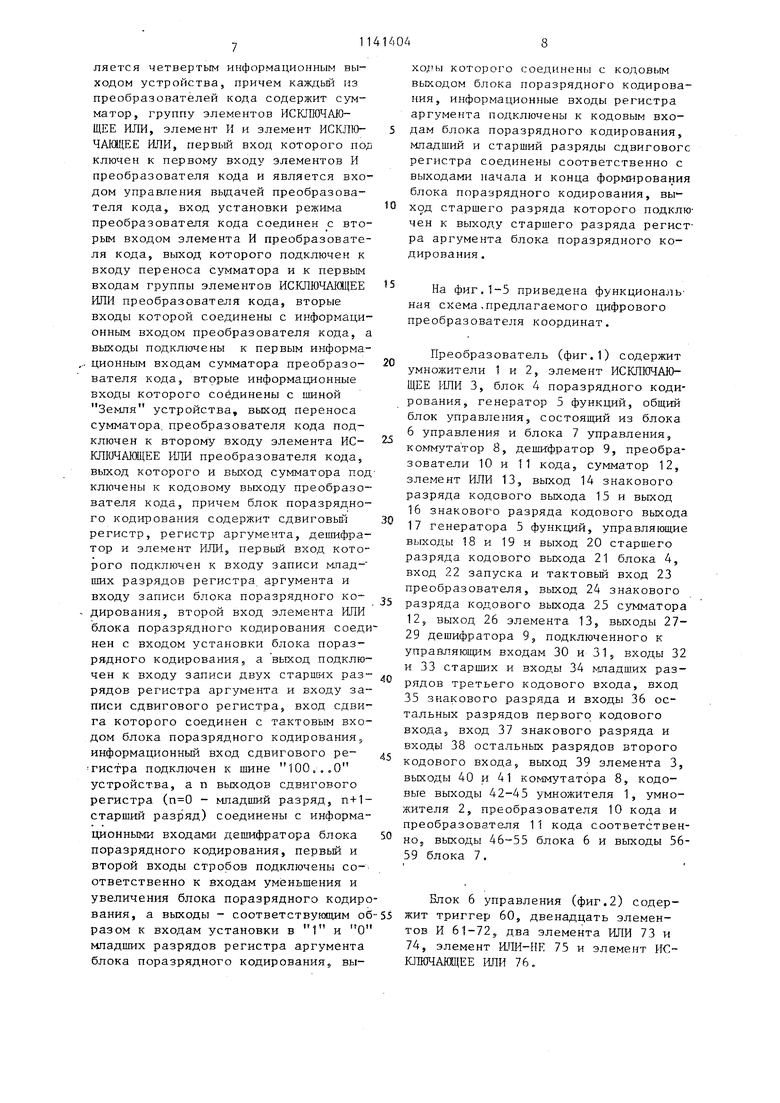

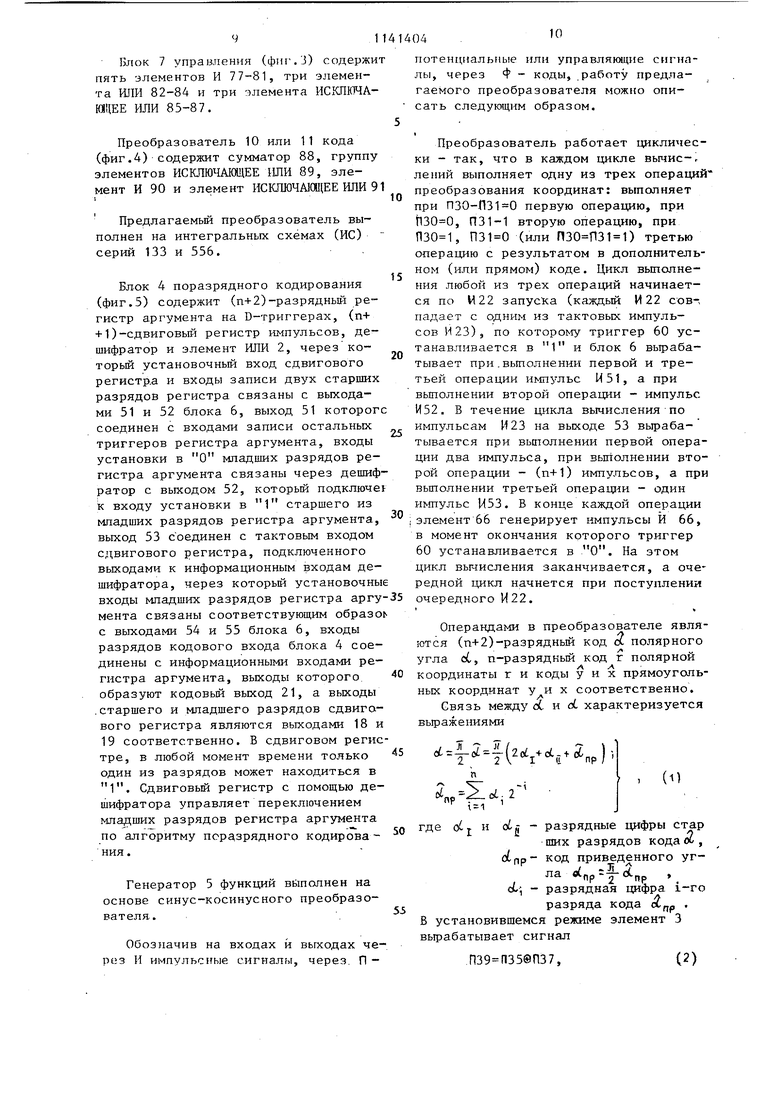

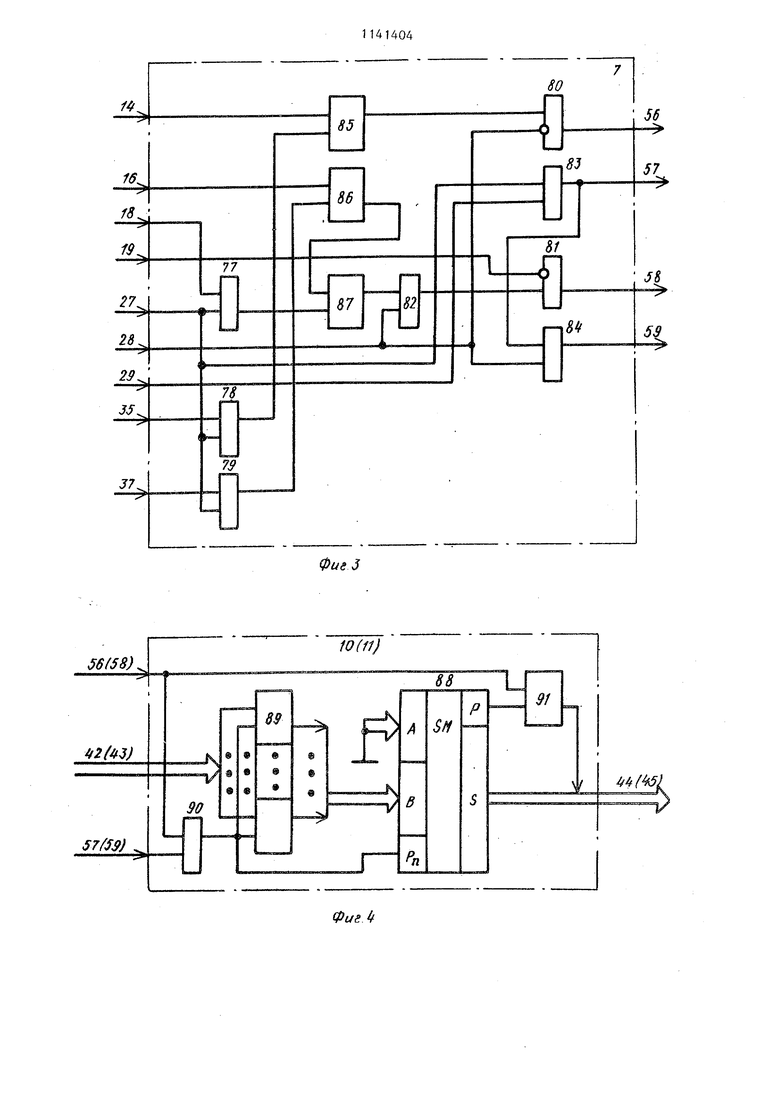

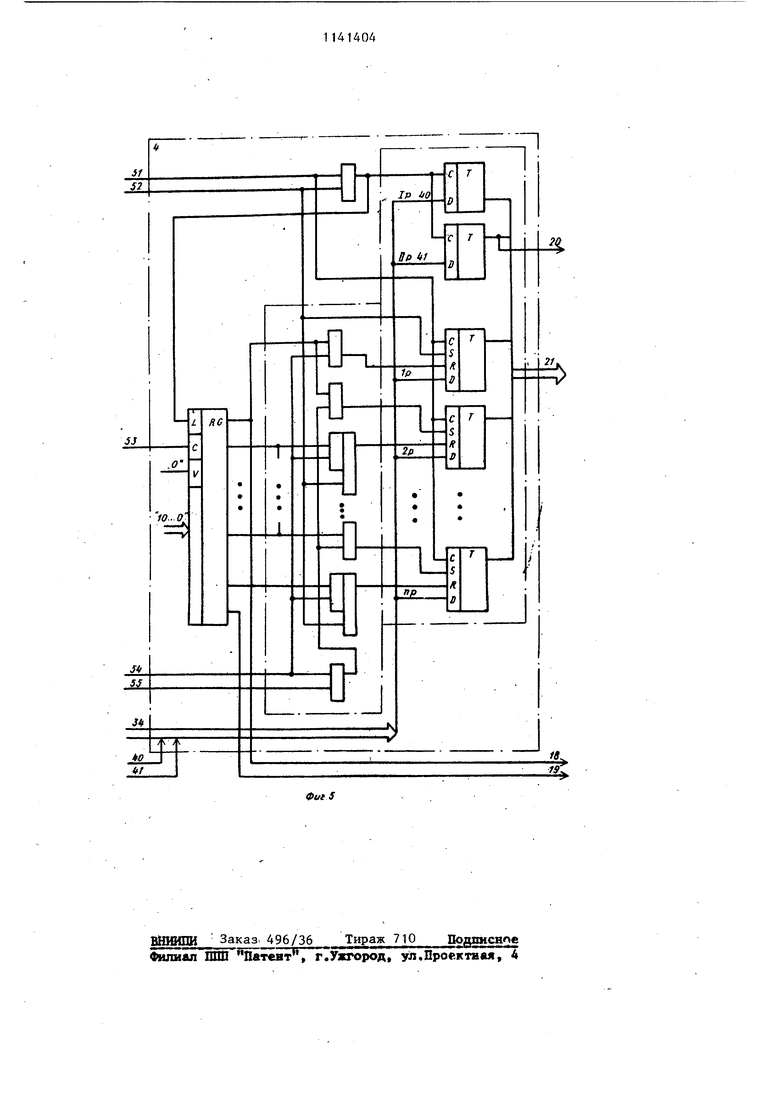

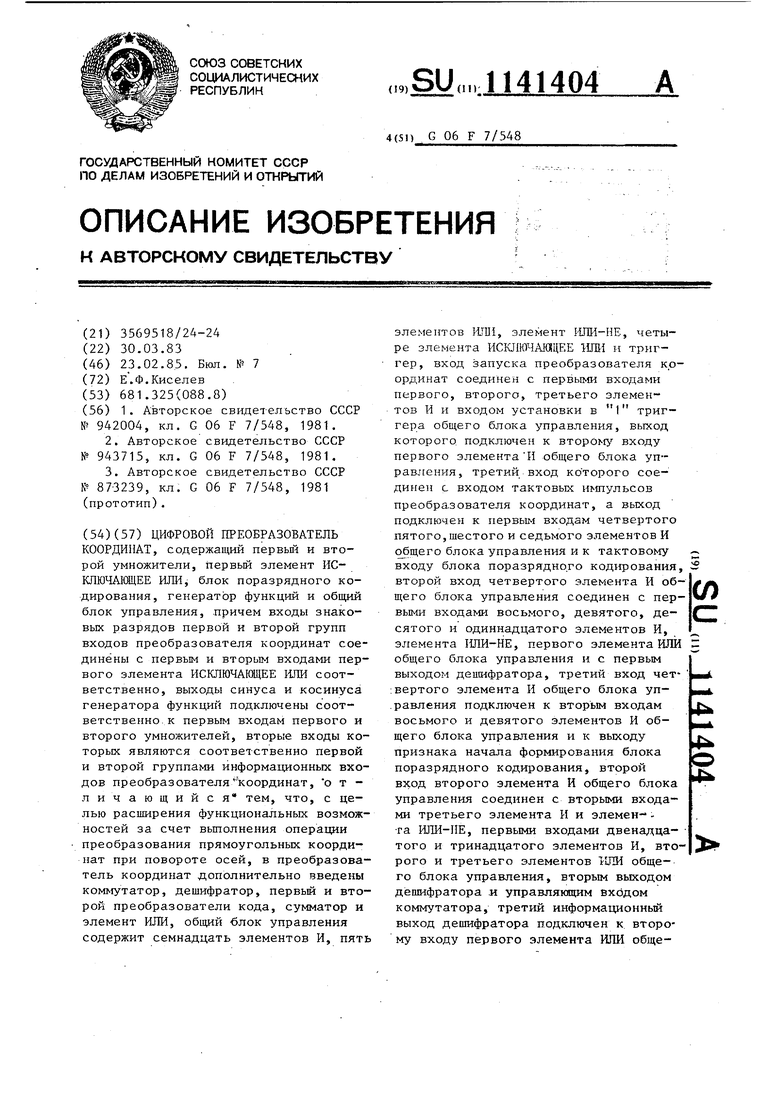

разом к входам установки в 1 и О младших разрядов регистра аргумента блока поразрядного кодирования, вытов И 61-72, два элемента ИЛИ 73 и 74, элемент ИЛИ-НЕ 75 и элемент И€ ЮтаЧАЩЕЕ ИЛИ 76. хо;ы которого соединен(Л с кодовым выходом блока поразрядного кодирования, информационные входы регистра аргумента подключены к кодовым входам блока поразрядного кодирования, младший и старший разряды сдвигового регистра соединены соответственно с выходами начала и конца формирования блока поразрядного кодирования, выход старшего разряда которого подключен к выходу старшего разряда регистра аргумента блока поразрядного кодирования , На фиг.1-5 приведена функциональная схема.предлагаемого цифрового преобразователя координат. Преобразователь (фиг.1) содержит умножители 1 и 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, блок 4 поразрядного кодирования, генератор 5 функций, обш;ий блок управления, состоящий из блока 6 управления и блока 7 управления, коммутатор 8, дешифратор 9, преобразователи 10 и 11 кода, сумматор 12, элемент ИЛИ 13, выход 14 знакового разряда кодового выхода 15 и выход 16знакового разряда кодового выхода 17генератора 5 функций, управляющие выходы 18 и 19 и выход 20 старшего разряда кодового выхода 21 блока 4, вход 22 запуска и тактовьй вход 23 преобразователя, выход 24 знакового разряда кодового выхода 25 сумматора 12, выход 26 элемента 13, выходы 2729 дешифратора 9, подключенного к управляющим входам 30 и 31, входы 32 и 33 старших и входы 34 младших разрядов третьего кодового входа, вход 35 знакового разряда и входы 36 остальных разрядов первого кодового входа, вход 37 знакового разряда и входы 38 остальных разрядов второго кодового входа, выход 39 элемента 3, вькоды 40 и 41 коммутатора 8, кодовые выходы 42-45 умножителя 1, умножителя 2, преобразователя 10 кода и преобразователя 11 кода соответственно, выходы 46-55 блока 6 и выходы 5659 блока 7. Блок 6 управления (фиг.2) содертриггер 60, двенадцать элеменБлок 7 управления (фиг-.З) содержит пять элементов И 77-81, три элемента ИЛИ 82-84 и три элемента ИСКПКТЧАЩЕЕ ИЛИ 85-87. Преобразователь 10 или 11 кода (фиг.4) содержит сумматор 88, группу элементов ИСКЛЮЧАВДЕЕ ИЛИ 89, элемент И 90 и элемент ИСКгаоЧАЮи(ЕЕ ИЛИ 9 Предлагаемьй преобразователь выполнен на интегральных схемах (ИС) серий 133 и 556. Блок 4 поразрядного кодирования (фиг.5) содержит (п+2)-разрядньй регистр аргумента на D-триггерах, (п+ +1)-сдвиговый регистр импульсов, дешифратор и элемент ИЛИ 2, через которьй установочный вход сдвигового регистр.а и входы записи двух старших разрядов регистра связаны с выходами 51 и 52 блока 6, выход 51 которог соединен с входами записи остальных триггеров регистра аргумента, входы установки в О младших разрядов регистра аргумента связаны через дешиф ратор с выходом 52, который подключе к входу установки в 1 старшего из мпадших разрядов регистра аргумента, выход 53 соединен с тактовым входом сдвигового регистра, подключенного выходами к информационным входам дешифратора, через которьй установочны входы мпадших разрядов регистра аргу мента связаны соответствуюш,им образо с выходами 54 и 55 блока 6, входы разрядов кодового входа блока 4 соединены с информационными входами регистра аргумента, выходы которого образуют кодовьй выход 21, а выходы .старшего и младшего разрядов сдвигового регистра являются выходами 18 и 19 соответственно. В сдвиговом регис тре, в любой момент времени только один из разрядов может находиться в 1. Сдвиговьй регистр с помощью дешифратора управляет переключением младших разрядов регистра аргумента по алгоритму поразрядного кодирсГвания. Генератор 5 функций вВтолнен на основе синус-косинусного преобразователя. Обозначив на входах и выходах че рез И импульс 1ые сигналы, через. П потенциальные или управлякнцие сигналы, через Ф - коды, работу предлагаемого преобразователя можно описать следующим образом. Преобразователь работает циклически - так, что в каждом цикле вычис-f лений выполняет одну из трех операциипреобразования координат: выполняет при П30-П31 0 первую операцию, при , П31-1 вторую операцию, при , (или ) третью операцию с результатом в дополнительном (или прямом) коде. Цикл вьтолнения любой из трех операций начинается по И 22 запуска (каждый И 22 совпадает с одним из тактовых импульсов И 23), по кoтopo гy триггер 60 устанавливается в 1 и блок 6 вьфаба- тывает при.выполнении первой и третьей операции импзльс И 51, а при вьшолнении второй операции - импульс И52. В течение цикла вычисления по импульсам И 23 на выходе 53 вырабатывается при выполнении первой операции два импульса, при выполнении второй операции - (п+1) импульсов, а при выполнении третьей операции - один импульс И53, В конце каждой операции элемент 66 генерирует импульсы И 66, в момент окончания которого триггер 60 устанавливается в О, На этом цикл вьг 1исления заканчивается, а очередной цикл начнется при поступлении очередного И 22. Операндами в преобразователе являются (п+2)-разрядньй код оС полярного угла оС, п-разрядньй код г полярной координаты г и коды у и х прямоугольных координат у и X соответственно. Связь между оС и ot характеризуется выражениями об42-|К .)-. np-ff i,2 oLf - разрядные цифры стар где с/.; Епих разрядов кода ot , код приведенного угла e(, np-2 Пр сС; - разрядная цифра 1-го разряда кода . В установившемся режиме элемент 3 вырабатывает сигнал П39 П35®П37, коммутатор 8 - сигналы П40 П28-П32УП28-П35 П41 П28ПЗЗ П28-П39 ) блок 7 - сигналы П56(П14@П27-П35) П2 П57 П27УП29 (П16®П27-П3 vn28 , n59 n57vn28 умножители 1 и 2 - коды Ф43 Ф17Ф38 J , ..сумматор 1 2 - код Ф25 ф44+с{ 45 , элемент 13 - сигнал 0при 1приф25 0, а генератор 5 функций Ь„УП50 а о bovn50-ao и коды ф15 1П50 t УПЗО а I Sv П5б а где X - оператор умноже b-cSs 1Ф21; Ф21-(п+2)-разрядньш а иЬ - разрядные ц

разрядов кодов а и Ь.

Преобразователь 10 (и.ли 11) кода по коду Ф42 (или Ф43) и сигналам П56 и П57 (или П58 и П59) формирует при (и.пи при ) прямой, а при (или при ) - дополнительньш код Ф 44 (или Ф45)э знаковый разряд которого определяется сигналом П56 (или П58), Причем /Ф44/ Ф42, а /Ф45/ Ф43.

Перед началом каждого цикла вычислений триггер 60 находится в О, а содержимое блока 4 определяется предьдущим циклом вычислений.

С учетом из юженного рассмотрим, как в преобразователе осуществляется цикл вьшолнения каждой из трех операций преобразования координат.

триггер 60 устанавливается в О,что означает конец цикла вычислений.

Следует заметить, что первая операция выполняется и для отрицательных углов

-2Л : Ч 0.

(13)

На предлагаемьй преобразователь при вьшолиеиии первой операции в случае (13) необходимо подавать код й согласно (1).

В течение каждого цикла выполнения второй операции на преобразователь поступает управляющий кодПЗО П31 01, прямой код у, опредепяемьй сигналом (5 и кодом и прямой код X, определяемый сигналом и кодом ,. В течение каждого цикла выполнения первой операции на ЦПК поступает управляющий код ПЗОП31 00, код сх , определяемый сигналами П32 cij, П и кодом Ф34 Лпр , прямой код у (т.е. , I У Ф36) и прямой код и (т.е. , ). Цикл вычислений начинается по И 22, по которому блок 6 генерирует И 51. После окончания И 51 в регистр блока 4заносится код о(. Ф21, а сдвиговьй регистр блока 4 устанавливается в состояние 10,...О первого такта кодирования (П18-1), и начинается первый такт выполнения первой операции. Сумматор 12 вырабатывает в течение первого такта дополнительный код 25 y cosd+(-x sind) , (11) а в течение второго такта - дополнительньй код х Ф25 51па +ххсоз cf-, где у и х - координаты точки (у, х) относительно новой прямоугольной системы координат с тем же началом, расположенной относительно системы таким o6pa3OMj что угол хОх между осью Охи ос,ью Ох равен Ы и отсчитьшается в положительном направлении. Блок 6 в конце первого такта вырабатывает импульс И 46, а в конце второго такта - импульсы И47 и И66. По И46 и И 47 осуществляется съем с преобразователей (11) и (12) кодов соответственнОо После окончания И 66 llo и;2 блок 6 сначала генерирует ,а чатем (п + 1) импульсов от И 53 по И23. После, окончания И52 сдвиговый регистр блока 4 устанавливается в состояние 10... О, а Ф 21 oi j-oi,-,10.. .О, где aoij-n4l y @ Первые п тактов второй операции являются тактами поразрядного кодиро вания для нахождения, с помощью импульсов И 54 и И55 (при () вырабатывается или импульс И54 уменьшения кода Ф21, либо импульс И 55 увеличения кода Ф21), кода о Ф21, такого, для которого наиболее точно выполняется приближенное равен ство Ф44+ф45(у,(-|,(п+1)-такте второй операции ( П19 1) находится код г г Ф25 ф44+Ф45 у.з1пЫ.+ ot (15) и вырабатываются импульсы И48 и И66. По И 48 производится съем кодов полярных координат и , после окончания И 66 триггер 60 устанавливается в О, что означает коне цикла вычислений. i В течение каждого цикла вьтолнения третьей операции -на преобразователь поступает управляющий код ПЗО (или ПЗО.П31 11), код г Ф36 Ф38 и код (J , определяемьм сигналами П32 oCj. П (5И кодом Ф34 2„р. По И 22 блок 6 сначала генерирует И51, а затем импульсы И49 и И66. Пос ле окончания И51 сдвиговьй резистр блока 4 устанавливается в состояние 10...О, .j..... Третья операция выполняется за один такт, в течение которого преобразователи 10 и 11 кода вырабатывают при ПЗО дополнительные, а при ПЗО - прямые коды координат, т.е.. ф44 х г-cos оС -sin Ы По И49 производится съем кодов прямоугольных координат и у Ф45, а после окончания И 66 триггер 60.устанавливается в О, что .означает конец цикла вычислений. Из указанного следует, что длительности циклоё вьтолнения первой, второй и третьей операции составляют 11, Т2, ТЗ соответственио: T2(n+1)t; гДе t - период частоты следования тактовых импульсов И 23, выбираемь1й из соотношения t / ts + +Vtl2- tl5 20) где tj,t,t,t,j и - длительность установления сигналов в генераторе 5 функций, умножителе 1,формирователе 10, сумматоре 12 и элементе 13 соответственно. Известный преобразователь реализует первую операцию за. время T1j,(n+3)n/2. Сравнивая (21) и (17) для получаем TUo ,г ТТ Реализация известного и предлагаемого преобразователей для на ИС серий 133 и 556 показывает, что объем оборудования предлагаемого преобразователя примерно в два раза меньше объема оборудования известного. Технико-экономическая эффективность изобретения заключается в том, что при примерно равных объемах оборудования предлагаемого и известного преобразователей последний имеет более широкие функциональные возможноети: позволяет выполнять операцию преобразования прямоугольных координат при повороте осей и вьщавать результат операции преобразования полярных координат в прямоугольные координаты как в дополнительном, так и прямом коде.

ФиеЗ

Фиё it

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-02-23—Публикация

1983-03-30—Подача