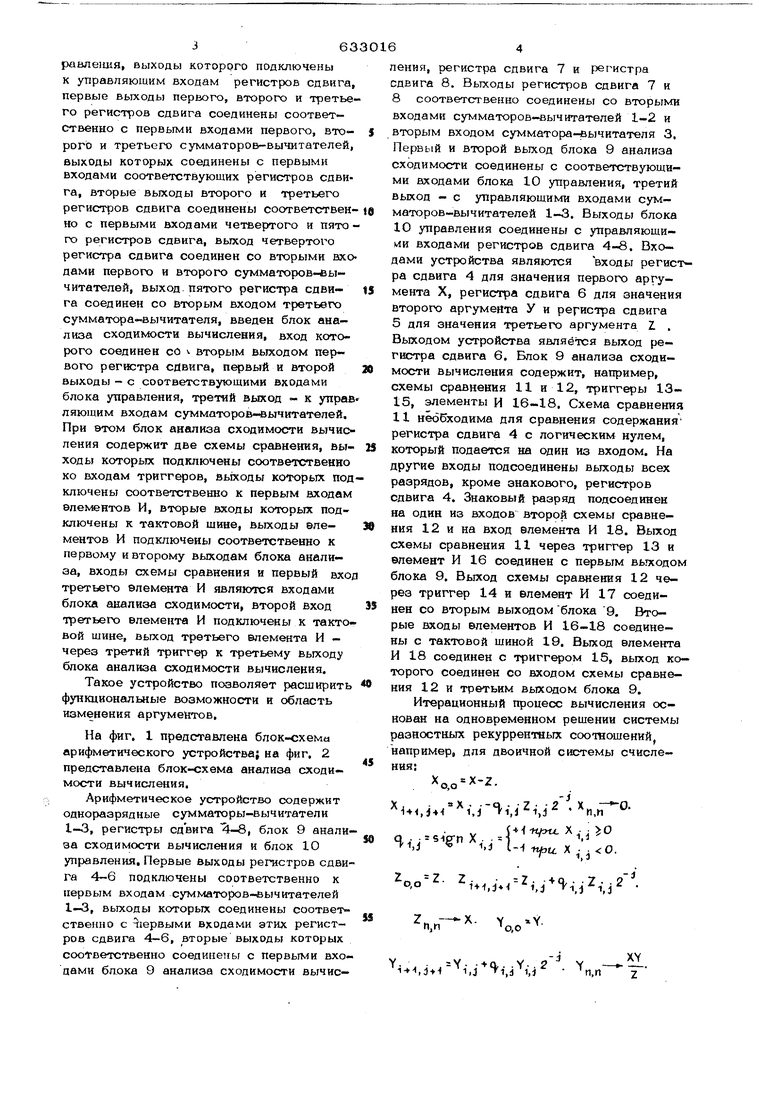

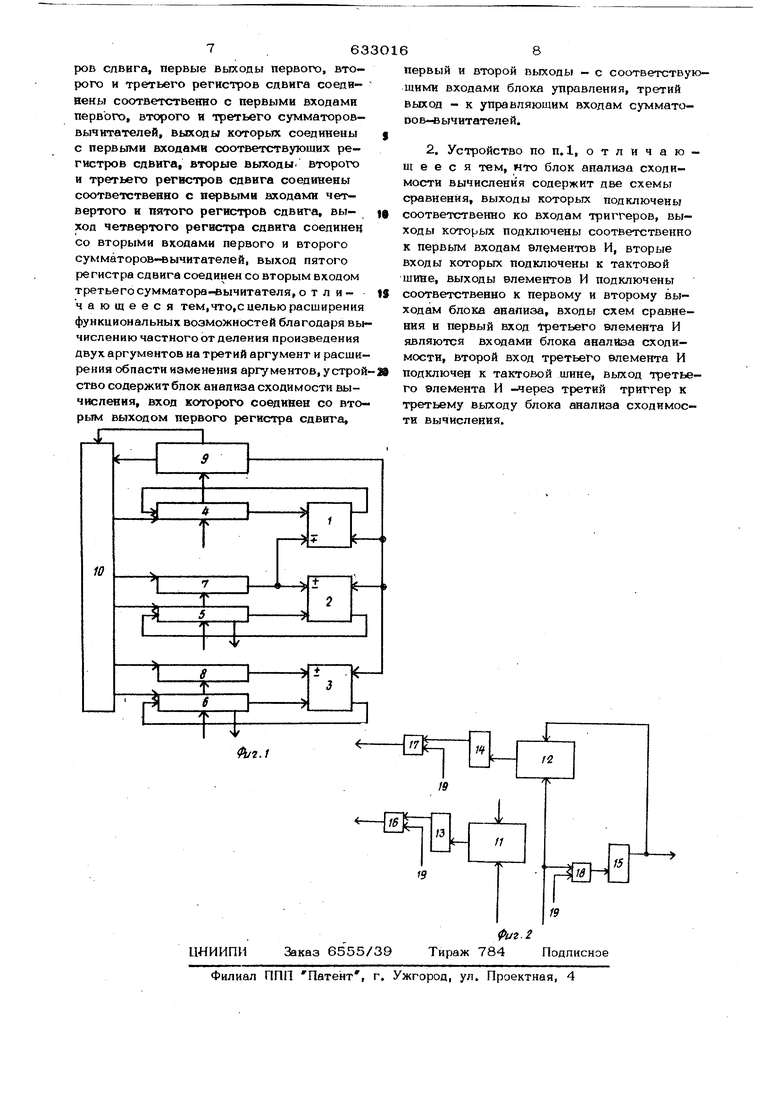

раале1шя, выходы которого подключены к управляющим входам регистров сдвига, первые выходы первого, второго и третье го регистров сдвига соединены соответственно с первыми входами первого, второго и третьего сумматоров-вычитателей, выходы которых соединены с первыми входами соответствующих регистров сдвига, вторые выходы второго и третьего регистров сдвига соединены соответствен но с первыми входами четвертого и пято го регистров сдвига, выход четвертого регистра сдвига соединен со вторыми вхо дами первого и второго сумматоров- ы- читателей, выход пятого регистра сдвига соединен со вторым входом третьего сумматора-вычитателя, введен блок анализа сходимости вычисления, вход которого соединен со вторым выходом первого регистра сдвига, первый и второй выходы - с соответствующими входами блока управления, третий выход - к управ ляющим входам сумматоров-Фычитателей. При этом блок анализа сходимости вычисления содержит две схемы сравнения, выходы которьгх подключены соответственно ко входам триггеров, вь1ходы которых под ключены соответственно к первым входам Элементов И, вторые входы которьгх подключены к тактовой шине, выходы элементов И подключены соответственно к первому и второму выходам блока анализа, входы схемы сравнения и первый вхо третьего элемента И являются входами блока анализа сходимости, второй вход третьего элемента И подключены к такто вой шине, выход третьего элемента И - через третий триггер к третьему выходу блока анализа сходимости вычисления. Такое устройство позволяет расширить функциональные возможности и область изменения аргументов. На фиг, 1 представлена блок-схема арифметического устройства} на фиг, 2 представлена блок-схема анализа сходимости вычисления. Арифметическое устройство содержит одноразрядные сумматоры-вычитатели 1-3, регистры сдвига t-8, блок 9 анали за сходимости вычисления и блок 10 управления. Первые выходы регистров сдви га 4-6 подключены соответственно к первым входам сумматоров-вычитателей 1-, выходы которых соединены соответственно с 11ервыми входами этих регистров сдвига 4-6, вторые выходы которых соответственно соедиЕ1е 1ы с первьгми вхо дами блока 9 анализа сходимости вычис- ения, регистра сдвига 7 и регистра двига 8. Выходы регистров сдвига 7 и 8 соответственно соединены со вторыми входами сумматоров-вычитателей 1-2 и вторым входом сумматора-вычитателя 3, Первый и второй выход блока 9 анализа сходимости соединены с соответствующими входами блока 10 управления, третий выход - с управляющими входами сум- маторов-вычитателей 1-3, Выходы блока 10управления соединены с управляющими входами регистров сдвига 4-й, Входами устройства являются входы регистра сдвига 4 для значения первого аргумента X, регистра сдвига 6 для значения второго аргумента У и регистра сдвига 5 для значения третьего аргумента Z . Выходом устройства является выход регистра сдвига 6, Блок 9 анализа сходимости вычисления содержит, например, схемы сравнения 11 и 12, триггеры 1315, элементы И 16-18, Схема сравнения 11н ёобходима для сравнения содержания регистра сдвига 4 с логическим нулем, который подается на один из входом. На другие входы подсоединены выходы всех разрядов, кроме знакового, регистров сдвига 4, Знаковый разряд подсоединен на один из входов второй схемы сравнения 12 и на вход элемента И 18, Выход схемы сравнения 11 через триггер 13 и элемент И 16 соединен с первым вьтходом блока 9, Выход схемы сравнения 12 через триггер 14 и влемент И 17 соединен со вторым выходом блока 9, Вторые входы элементов И 16-18 соединены с тактовой шиной 19, Выход элемента И 18 соединен с триггером 15, выход которого соединен со входом схемы сравнения 12 и третьим выходом блока 9, Итерационный процесс вычисления основан на одновременном решении системы разностных рекуррентных соотношений, например, для двоичной системы счисления:0,0 -2. ,j2x„ -О. ,. х.. S-i.j , (,1с X -,0. 2о.. i+i,,j Sij-2 -j2 V-Y. .-va Y. Y . N-H,;)+-f ,J ri,jl,i In.nZ

где i -показатель порядкового номера итерации, j 0,1, ...

...ц-показатель веса ите|: ации,

П -число разрядов.

Вычисления в арифметическом устройстае осуществляются следующим образом.

Первоначально в регистр сдвига 4 заносится значение аргумента X, в регистр сдвига 5 - еначение аргумента Z ив регистр сдвига 6 - значение аргумента У

8начальной итерации тактовые импульсы с выхода блока Ю управления начинают поступать только в регистры сдвига 4 и 7, содержание которых алгебраически суммируется в сумматоре-вычитателе 1. Резулыгат начальной итерации записывается в освобождающиеся при сдвиге старшие разряды регистры сдвига 4. В конце начальной итерации в этом регистре содержится значение X - Z .

В любой l,j -ой итерации с выходов блока 10 управления выдаются последовательности (серии,) тактовых импульсов для сдвига содержания регистров сдвига 7 и 8 на j разрядов вправо от запятой и продвижения содержаний регистров сдвига 4-S на соответствующие входы сумматоров-«ычитателей 1-3, Резульлгаты каждой итерации записываются с выходов сумматоров-вычитателей 1-3 младшими разрядами вперед а освобождающиеся при сдвиге старшие разряды регистров сдвига 4-6 соответственно и продвигаются в сторону младших разрядов к началу этих регистров, В конце каждой итерации по сигналу с тактовой шины 19 в блоке

9анализа сходимости вычислений гю знак содержания регистра сдвига 4 формируется очередная цифра оператора J , ; . путе

установки триггера 15 в соответсп tiyrouiee положение. При значении - ; -1 тор-вычитатель 1 работает в режиме слижения,сумматоры-вычитатели 2-3 в режиме вычитания. При О, - +l режим их twботы заменяется на обратный. При иеромене значения очередной цифры(- j to схемы сравнения 12 через триггер 14 и епемен И 17 со второго выхода блока 9 на блок 10 управления выдается сигнал перехода от j -и величины к следующей величине сдвига на J 1 разрядов, т,е, вое итерации увеличивается на единицу. При нулевом содерх ании регистра сдвига 4 с выхода схемы сравнения 11 через триггер 13 и элемент Н 16 с первого выхо- да блока 9 на вход блока 10 выдается сигнал останова, т,к, процесс вычисления закончен и тактовые импульсы на следующей итерации не выдаются. При втом содержание регистра сдвига 6 равно значению частного от деления произведения двух аргументов на третий.

Максимальное время вычисления в тактах равно п( n-nn) + fn где тчисло дополнительных разрядов для компенсации погрешности усечения чисел при сдвиге, и растет с уменыиением аргумента Z , Однако благодаря асинхронному режиму работы для болыиинства оначоний аргументов время вычисления меныле максимального значения, что значительно меньше времени вычисления при помощи отдельных операций умножения и деления при сравнимых затратах оборудования.

В таблице приведен пример вычисления в арифметическом устройстве для значений аргументов X 0,5, У 0,25 и Z 0,125.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для возведения в степень | 1975 |

|

SU616628A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU586458A1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

Для втнх значений ар тлентов время вычисления равно 2( h + m ) тактов или 30 тактов для 12-раарядных чисел.

Сравнительные испытания данного арифметического устройства с известным устройством показали, что данное устройство обладает расширенными функцнональными возможностями, не накладыва-

ет ограничения на пределы изменения аргументов и обеспечивает высокое быстродействие при умеренных аппаратурных затратах.

Формула изобретения

.Арифметическое устройство, содержащее блок управления, выходы которого подключены к упраешяюшим входам регистр

ров слвига, первые выходы первого, второго и третьего регистров сдвига соединены соответственно с первыми входами первого, второго и третьего сумматороввычитателей, выходы которых соединены с первыми входами соответствующих регистров сдвига, вторые выходы второго и третьего регистров сдвига соединены соответственно с первыми яходами четвертого и пятого регистров сдвига, выход четвертого регистра сдвига соединен со вторыми входами первого и второго сумматоров-вычитателей, выход пятого регистра сдвига соединен со вторым входом третьегосумматоранзычитателя,о т л ичающееся тем,что.с целью расширения функциональных возможностей благодаря вычислению частного от деления произведения двух аргументов на третий аргумент и расширения области изменения аргументов, устройство содержит блок анализа сходимости вычисления, вход которого соединен со вторым выходом первого регистра сдвига.

первый и второй выходы - с соответствующими входами блока управления, третий выход - к управляющим входам сумматоDOB-вычитателей.

соответственно ко входам триггеров, выходы которых подключены соответственно к первым входам элементов И, вторые входы которых подключены к тактовой шине, выходы элементов И подключены

соответственно к первому и второму выходам блока анализа, входы схем сравнения и первый вход Третьего элемента И являются входами блока анализа сходимости, второй вход третьего элемента И

подключен к тактовой шине, выход третьего элемента И третий триггер к третьему выходу блока анализа сходимости вычисления.

Авторы

Даты

1978-11-15—Публикация

1975-12-15—Подача