1

(61) 1322269

(21)4492754/26

(22)10.10.88

(46) 30.01.91. Бюл. V 4

(71)Таганрогский радиотехнический институт им. В.Д.Калмыкова

(72)Р.В.Коробков и В.К.Золотопский

(53)681.325(088.8)

(56)Авторское свидетельство СССР

№ 1322269, кл. G 06 F 7/544, 1986.

(54)УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ ИЗ СУММЫ КВАДРАТОВ ТРЕХ ЧИСЕЛ

(57)Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин. Пелью изобретения является расширение функциональных возможностей устройства за счет контроля правильности вычислений. Поставленная цель достигается тем, что в устройство для извлечения корня из суммы квадратов трех чисел, содержащее пять регистров 4-8, четыре группы 9-12 элементов И, три сумматора 13, 14, 15, триггер 17, элемент НЕ 16, введены пять блоков 23-26, 40 формирования вычета, квадратор 39,три умножителя 30-32 вычета на два, четыре сумматора 33, 34, 35, 43, три множителя 36, 37, 38 вычетов, два блока 41 и 42 вычисления дополнения вычета, схема 44 сравнения с нулем, квадратор 39. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1987 |

|

SU1501050A1 |

| Устройство для контроля делителя по модулю | 1988 |

|

SU1566352A1 |

| Устройство для сложения и вычитания с самоконтролем | 1988 |

|

SU1642469A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

О5

4Ь

4 4 4ь

1Ч

Изобретение относится к вычислительной технике.

Цель изобретения - расширение функциональных возможностей за счет контроля прапнльности вычислений.

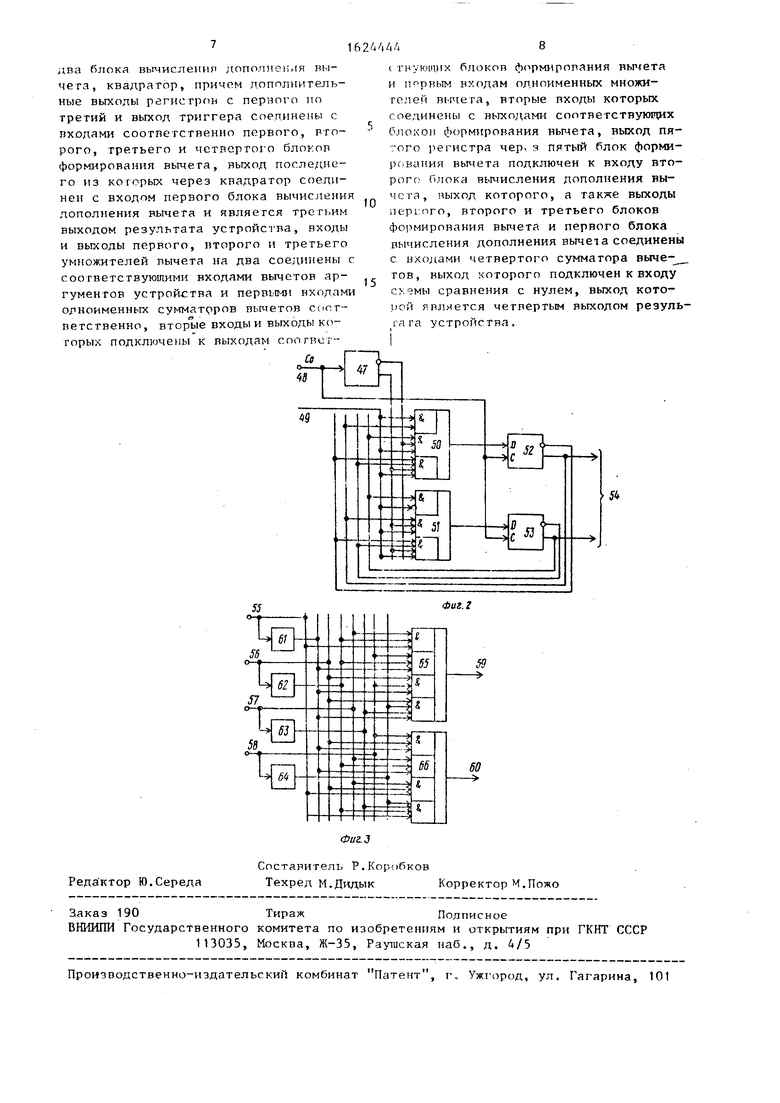

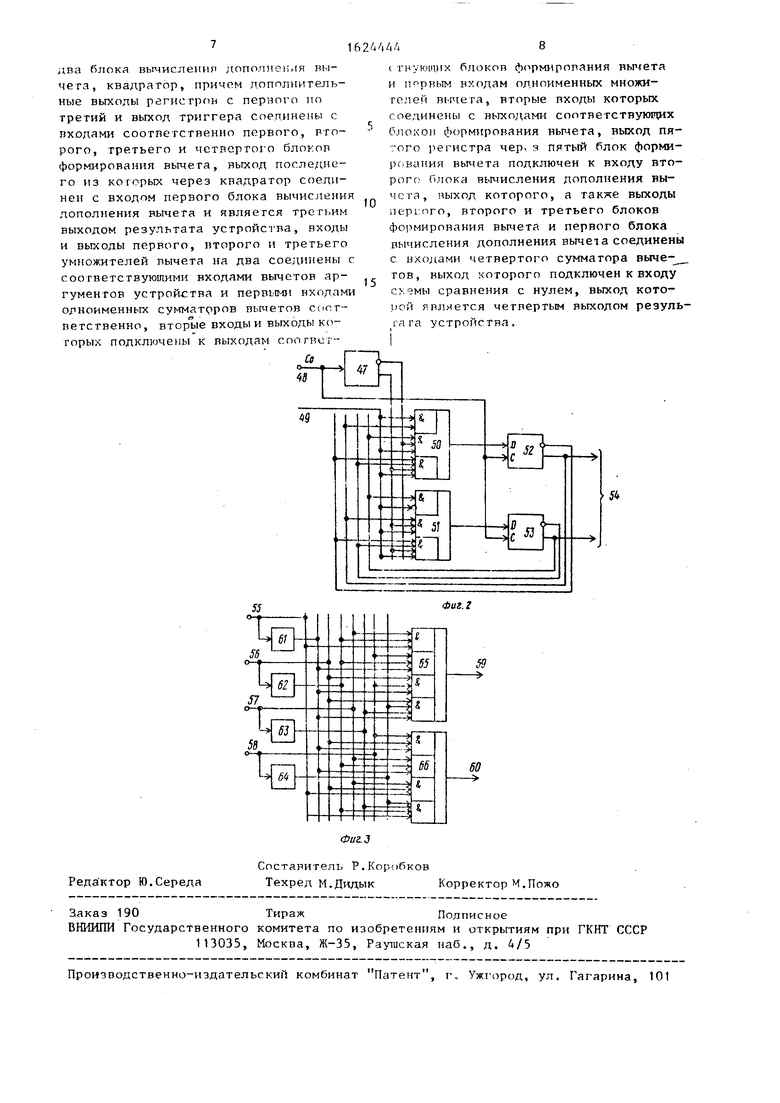

На фиг . 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - вариант блока формирования вычета и

регистре 7 длиной п-1 разряд формируются старшие п-1 разряды функции d В регистре 8 формируется значение остатка Oi. R группах -элементов И 9- 11, соединенных с выходами регистров 4-6, формируются частичные квадраты аргументов a,b,c. R группе -элементов И 12 формируется частичный квадрат

схема ячейки, на которых он может быть результата d , а в сумматорах 13 и

14 - частичные, квадраты аргументов а,Ь,с складываются. Полученная сумма в сумматоре 15 складывается с час тичным квадратом функции. Знаковый j разряд сумматора 15 инвертируется

реализован.

Устройство содержит входы 1-3 аргумента устройства, регистры 4-8, группы элементол И 9-12, сумматоры 13-15, -элемент HF. 16, триггер 17, вход 18 запуска, вход 19 логического нуля, синхровход 20 устройства, первый и второй выходы 21 и 22 результата устройства, г первого по четвертый

14 - частичные, квадраты аргументов а,Ь,с складываются. Полученная сумма в сумматоре 15 складывается с частичным квадратом функции. Знаковый j разряд сумматора 15 инвертируется

элементом НЕ 16 и поступает на 1)-вход триггера 17. Синхронизирующий сигнал С1 с входа 18 поступает на входы управления СДРИГом pei петров 4-7, вход

25

блоки 23-26 формирования вычета, входы о управления записью в регистр 8 и вход 27-29 вычетов аргументов устройства, умножители 30-32 вычета на два, сумматоры 33-35 вычетов, множители 36- 38 вычетов, квадратор 39, пятый блок 40 формирования вычета, первый 41 и второй 42 блоки вычисления дополнения вычета, сумматор 43 вычетов, схема 44 сравнения с нулем, третий 45 и четвертый 46 выходы результата устройства, триггер 47 (фиг.2), входы 48 и 49 бло-эд ка формирования вычета, элементы И-ИЛИ 50-51, триггеры 52 и 53, выход 54 блока, входы 55-58 ячейки (фиг.З), выходы 59 и 60, элементы НЕ 61-64, элементы И-ИЛИ 65 и 66.

В предлагаемом устройстве реализу- е гея операция

35

сброса в состояние 1 триггера 17. На вход 19 поступает ьонсгаша 0, па вход 20 поступает синхронизирующая серия С, управляющая -записью в триггер 17 кода с р-входа. С выходов 21 и 2 считывается искомое значение «.1. Разряды аргументов а,Ь,с, выталкиваемые ; з регистров 4-6, поступают на входы блоков 23-25 сформирования вычетов, формирующих значение Выч.а, Выч.Ь , Выч . соответственно. Единичный рьгхо ipnrrcpa 17 соединен с. входом блока 6 формирования вычета, формирующего значение Выч . Z; . Вычеты аргументов a,h,c поступают на входы устройства 27-Г9 и удваиваип ся в схемах 30-32 умножения вычета на дна. R сумматорах 31-35 формир ппя соответственно разности ( 2Вы« . а - .Выч .а ) , (2Выч.Ь - 2Выч.Ь;), (2Впч . с - Вмч . с) . Полученные разности умножаются в множителях 36-38 па Выч . а , Выч.Ь,,

-лГ

а2 + Ь + с2.

(1)

Алгоритм контроля правильности вычислений имеет следуютиш вид:

((2 Выч. а - Выч.а )Выч.а- + (2-Выч.Ь - i

40

сброса в состояние 1 триггера 17. Н вход 19 поступает ьонсгаша 0, па вход 20 поступает синхронизирующая серия С, управляющая -записью в три гер 17 кода с р-входа. С выходов 21 и 2 считывается искомое значение «. Разряды аргументов а,Ь,с, выталкива емые ; з регистров 4-6, поступают на входы блоков 23-25 сформирования вычетов, формирующих значение Выч.а, Выч.Ь , Выч . соответственно. Единичный рьгхо ipnrrcpa 17 соединен с входом блока 6 формирования вычета формирующего значение Выч . Z; . Вычет аргументов a,h,c поступают на входы устройства 27-Г9 и удваиваип ся в сх мах 30-32 умножения вычета на дна. сумматорах 31-35 формир ппя соотве ственно разности ( 2Вы« . а - .Выч .а ) , (2Выч.Ь - 2Выч.Ь;), (2Впч . с - Вмч . с Полученные разности умножаются в мн жителях 36-38 па Выч . а , Выч.Ь,,

Bbw.cj coo гве гсвенно. 1 квадраторе

- Выч . Ь) Выч . Ь . -f (2 Выч. с - Выч .с ; ) Выч . с j + 39 вычисляется значение (Выч . d , ) L . 2

+ Доп (Bbi4.d;) + Доп(Выч.О;))тосШ 0 45

где Выч.а, Выч.Ь, Выч.с - вычеты аргументов а,Ь,с по модулю R; Выч.а1, Выч.Ь, Выч. с: - вычеты отработанных в i-м таге значений аргументов aj, ,/-. b;, cj по модулю К; Выч. 7,.- квадрат вычета значения функции dj, найденное в i-м шаге, Выч.0| - вычет остатка в i-м шаге, Доп.(Выч.X) - дополнение вычета X по модулю R, разрядность устройства п полагается четной. Аргументы а,Ь,с подаются на входы 1-3 устройства и с них записываются в регистры 4-6 сдвига соответственно. В

В блоке 40 формирования вычет форм руется значение О . К блоках 41 и 4 вычисления дополнения вычетов форми рую ся дополнения вычетов.В сумматор 43 формируется контрольная сумма, в схеме 44 она сравнивается с нулем. выхода 45 считывается вычет р1зульг га, а с ньгходл 46 - нгнал неисправ ности. При контроле по модуль три (1 3) фсрмиропаiели 73-26 могут быть выполнены ык, клк что п казано на гЬцг., гаком блок формиро вания сое гоит из суетно о три гера 47, на счетный Р.ХО, которл о с вхоч 48 поступает нгпрерывнтя тактовая

регистре 7 длиной п-1 разряд формируются старшие п-1 разряды функции d. В регистре 8 формируется значение остатка Oi. R группах -элементов И 9- 11, соединенных с выходами регистров 4-6, формируются частичные квадраты аргументов a,b,c. R группе -элементов И 12 формируется частичный квадрат

результата d , а в сумматорах 13 и

14 - частичные, квадраты аргументов а,Ь,с складываются. Полученная сумма в сумматоре 15 складывается с частичным квадратом функции. Знаковый разряд сумматора 15 инвертируется

элементом НЕ 16 и поступает на 1)-вход триггера 17. Синхронизирующий сигнал С1 с входа 18 поступает на входы управления СДРИГом pei петров 4-7, вход

управления записью в регистр 8 и вход

сброса в состояние 1 триггера 17. На вход 19 поступает ьонсгаша 0, па вход 20 поступает синхронизирующая серия С, управляющая -записью в триггер 17 кода с р-входа. С выходов 21 и 2 считывается искомое значение «.1. Разряды аргументов а,Ь,с, выталкиваемые ; з регистров 4-6, поступают на входы блоков 23-25 сформирования вычетов, формирующих значение Выч.а, Выч.Ь , Выч . соответственно. Единичный рьгхо ipnrrcpa 17 соединен с. входом блока 6 формирования вычета, формирующего значение Выч . Z; . Вычеты аргументов a,h,c поступают на входы устройства 27-Г9 и удваиваип ся в схемах 30-32 умножения вычета на дна. R сумматорах 31-35 формир ппя соответственно разности ( 2Вы« . а - .Выч .а ) , (2Выч.Ь - 2Выч.Ь;), (2Впч . с - Вмч . с) . Полученные разности умножаются в множителях 36-38 па Выч . а , Выч.Ь,,

39 вычисляется значение (Выч . d , ) L .

В блоке 40 формирования вычет формируется значение О . К блоках 41 и 42 вычисления дополнения вычетов формирую ся дополнения вычетов.В сумматоре 43 формируется контрольная сумма, в схеме 44 она сравнивается с нулем. С выхода 45 считывается вычет р1зульга- га, а с ньгходл 46 - нгнал неисправности. При контроле по модуль три (1 3) фсрмиропаiели 73-26 могут быть выполнены ык, клк что показано на гЬцг., гаком блок формирования сое гоит из суетно о три гера 47, на счетный Р.ХО, которл о с вхоча 48 поступает нгпрерывнтя тактовая

5

серия. На вход 4Г пос f пае г по ч нова гельныи кол числз , г IF когорт о ишегся пычег. Лпя блоков 74-75 Ьорми ропания это единичным выход с г iptnoro триггера регистра 4-6 с югвегс гвенно лля блока 76 Лорнирования - единичный выход триггера 17. Текучее ига- вычета формируется в чемгнгах И-ИЛИ 50 и 51. Сформированный впчег по сигналу описывается к гриперп 52 (старший разряд) и 53 (младший). Считывается вычет с выходов 54. Лля умножения вычета на два при R 3 достаточно его разряды поменять местами (старший разряд счигггь мчад- шим, младший старггим) . Аналогично формируется и дополнение вычег (иноки 41 и 42), разряды ныч-т меняются местами. Множитель вычегоч (Гле ки 36 38) представляют ссьом ,очбин гциг ино устройство. Чсли обозначить разряды первого вычета Х, разряды вго

рого вычета Y N и разря ai произведения по МОДУЛЮ i ри чс,ре 7, /| го

Кн 1дрсЗ тор 3е при R 3 npt дс г ич тис т собой меменг ИМИ, на вуолы toroporo подаются разряды Ri-r«.ci ч г выхода очигытае. ся мпадыии р при ре TVJII гага. (Старший разряд всегда равен

ч

Схема сформирования Ныч.( 40

лю

при R 3 MO/ р г Гыгь пос i роена н п ячейка (Лиг.З). V в/одам 55 и 5d подключается гчсредшя пара разрядов регистра 8. К 5 и 54 год- i-лючаюгся выходы 5Q ц 60 спседиеч мп 1,тшеи ячейки. Сама ячеш а г ос гон г из чгт2мент в HI 61-64 и эгнменгоп И-ИЛИ 65 и 66. Искомый вычс г с ш г i- ваегсч с выходов 54 и 60 сгарчюн Я1(еики.

Устройство paftor.ier слепуюпим образом.

Перед нача г м рапс ты г вм юр 1-3 в регис rpbi +-6 i тис i in погся аргументы а,Ь, . К ip.nm. 11гмен1ов И Ч-11 и с мчагора 13 и 1ч г юрми- сумма час гичны м iijaicn тр- г м in еж , которая про/ о ш г мер з сумматор 15 ii по( i на н оды регистра 8. Лал1 ныпс , яс гс я n-t-1 тд но тинных шагов. Ia vii ii j-n ш и начи нас гс я с подачи симм f ( 1 на вход 18. По э TOMV иг на v грш г ер 17 ус5

0

з

1 н i ч гояние 1 (т.е. lo р ряча d т.рпспшва

тан )чпив ь

31M4f ПИЮ

ется знач 1Ис )), п регистрах члнтся сдви нл одч разряд в cropoiiv сгаргих упзрчдоч, в регтгс гр

7HI григ tpa 17 пп 1М1ваегся 1-й разряд рез пьгата, в peiнегре 8 производите) запись 1черепнр о остатка.

8сумматор 15 п rvnaer очерепц- я суммт час ги иатч i BanjiarnB и частичный рртдра, ре ivju га d со знаком минус. Гс in схмма в сумма 15 не о грпца , i П-в-аде триггера 17 сигнтч 1, ести ггрицагечт i яя - сиг- пап 0. По vc гтнон 1ении ач najia на Р-вхо с грш i f та 1 п ic сигнзп

С 2 с 70 и в триггере 17 нтписы- нас ся (Счное падение -го разряда

0 d, 4s rtr-ota i n 1 ппы знеме1 гов И 17 - точное лмчспне часпч - го кпалрата DL зучь Гс г i, на ы Р о та умна п j ,1 15- гочное (паче j(r н га гк, Oj. lia -этом я зт igpepi Me гея. Г подачи сигнала С1

5 нл вход 18 начинаете и тедуюгиги таг. По 11 ом сигна iv i-, гс- миг разряд с переписывается г унгнс , 7, а в регистрах 4-7 проишо1иг я ст1вмг. триггер I7 сганан1И(1ет i i сен i IHHIU 1 ,

Q н ,jernc гр Ч i in ii i IB и г г я с г гок О и все чопгоря i i. с uiH.i iiirv вых дон с гаргии григ i i рог н i IH rpon -6 с чи- грзегся пос ч ;Ь h i n т HI in аргумегг- гов ч , h , , vor pi it ггрыичи разрядами вггерел пос гмпег i в чч Гтоков Я-TS фс рмиров шил ньп t i i в if ь i н;пед- них Лормчр |огся вычеты Ныч . т , Выч.Ь(, Выч. с . ( л П1ично п м-0 i г;шг г ерр 17 с1гигываег(я нос к i ) гепз ныи код Р 3 3yjir- га га с , чгфып пос. гмпег на

б 7ft ЛорМИрОН ППМ Ч ПК ГОВ И В ПРL челне м гЬормгр ч е гг п 1 ич . d }. В б т оке

5

0

0 Лормирпв,1,,,1я вычетов ормпр гегся

5

RI гч .(),. С п IMOI (г мы 4ч сртвнгния апг ри гм KV rpci

Ф г р м л и

М 1 ГО i л }

схсIP Н ° .

i о Г

ретпизгется

г е к и я

гроггсг п -i ч- цтвп11|,,1я корня из квадрзгов тре чгсег, по а1 г. свЛ , от тч i i h nee - с я гем, гго, i. HiiH iupe1 н ч функчион игг.Н г г i гт за счет кон i роля прани гг с ги i Ы пч- имгип , в riero иведено чяп f н г ов ( рмировяння вычегт, гри чl нтс i ru тт нл дна,

Четыре гор J Р1Гч ( 1 , Г1) МНОЛНгеля iiimeron, с ема с р i ь i н 1Я с ш тем,

два блока вычисления допоаненля вн- чега, квадратор, причем дополнительные выходы регистроь с первого по третий и выход триггера соединены с входами соответственно первого, вго- рого, третьего и четвертого блоков формирования вычета, выход последнего из коюрых через квадратор соединен с входом первого блока вычисления дополнения вычета и является третьим выходом результата устройства, входы и выходы первого, второго и третьего умножителей вычета на два соединены г соответствующими входами вычетов аргументов устройства и первыми входами одноименных сумматоров вычетов сиот- ветственно, второе входы и выходы которых подключены к выходам соогвег

55

5

( гн нлцих блоков формирования вычета и первым входам одноименных множителей вычета, вторые входы которых соединены с выходами соответствующих блоков формирования вычета, выход пя- -ого регистра чер а пятый блок формирования вычета подключен к входу второго блока вычисления дополнения вычета, выход которого, а также выходы iiepi iro, второго и третьего блоков формирования вычета и первого блока вычисления дополнения вычета соединены

с входами четвертого сумматора выче-

тов, выход которого подключен к входу о. змы сравнения с нулем, выход кото- ъой является четвертым выходом резуль- iara устройства.

Фиг. г

Авторы

Даты

1991-01-30—Публикация

1988-10-10—Подача