S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления интегра-лОВ | 1976 |

|

SU840901A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU877529A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1140118A1 |

| Устройство для вычисления квадратного корня | 1976 |

|

SU642706A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к вычислительной технике и может применяться в системах автоматического управления, измерения и контроля. Целью изобретения является обеспечение контроля устройства для вычисления квадратного корня. Поставленная цель достигается тем, что в состав устройства, содержащего коммутатор 2, накапливающий сумматор 3 и блок управления 4, введены сдвигающий регистр 5, триггер 6, элементы И 7,8 и ИЛИ 9. 2 ил.

4

00

СЛ

со

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах и устройствах.

Цель изобретения - обеспечение функ- ционального контроля устройства.

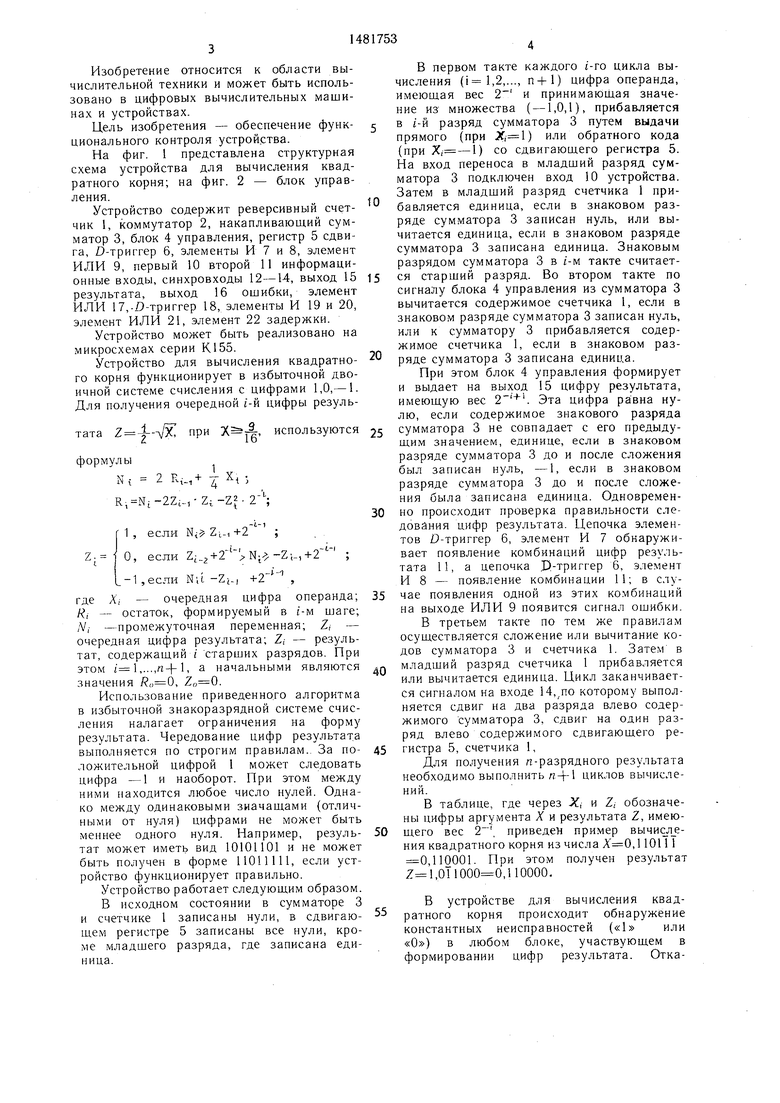

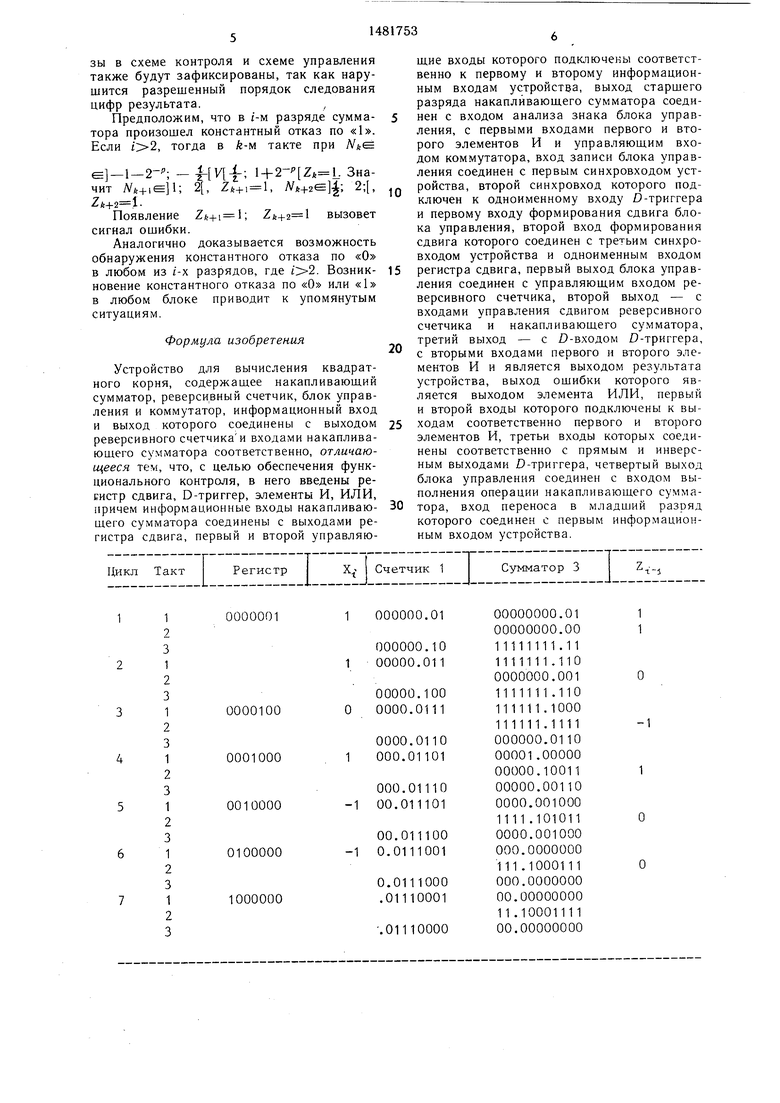

На фиг. 1 представлена структурная схема устройства для вычисления квадратного корня; на фиг. 2 - блок управления.

Устройство содержит реверсивный счетчик 1, коммутатор 2, накапливающий сумматор 3, блок 4 управления, регистр 5 сдвига, D-триггер 6, элементы И 7 и 8, элемент ИЛИ 9, первый 10 второй 11 информационные входы, синхровходы 12-14, выход 15 результата, выход 16 ошибки, элемент ИЛИ 17,-D-триггер 18, элементы И 19 и 20, элемент ИЛИ 21, элемент 22 задержки.

Устройство может быть реализовано на микросхемах серии К155.

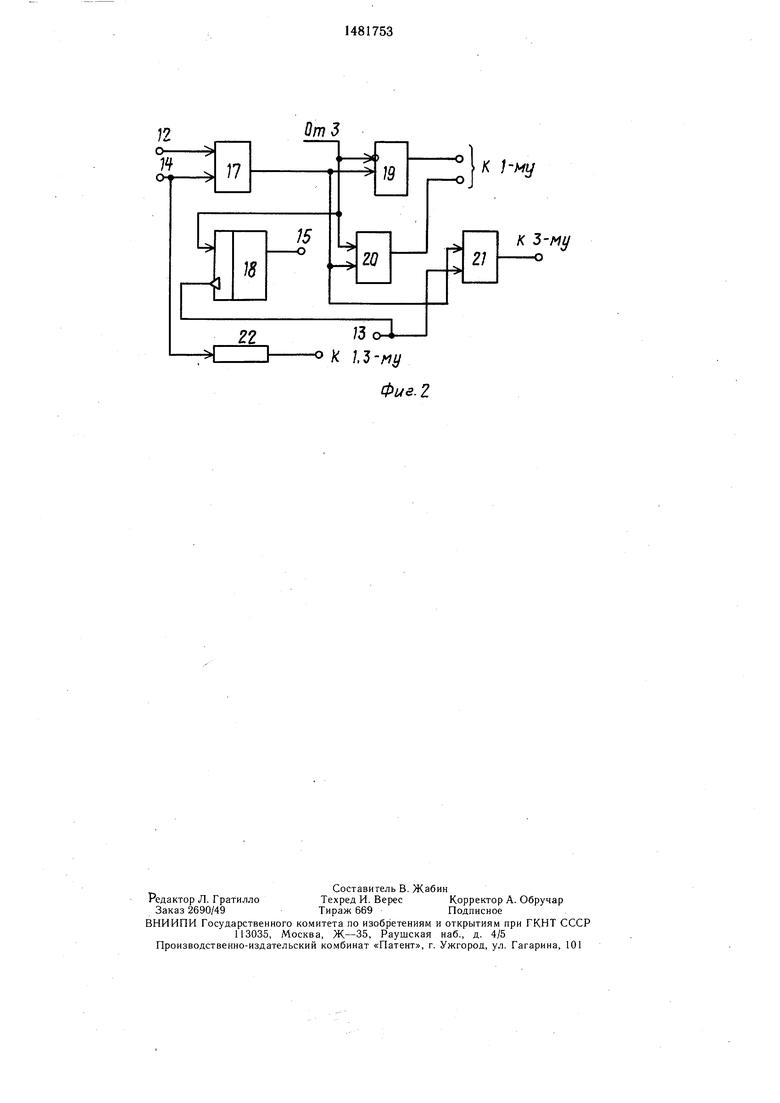

Устройство для вычисления квадратного корня функционирует в избыточной двоичной системе счисления с цифрами 1,0,- 1. Для получения очередной г-й цифры результата Z -|--VX при используются

формулы

N{ 2 RtM + I Xt 5

R Nt-ZZt-rZi-ZJ- 2Д;

( 1 , если N ZL-, ; , если ZL z+2 l U-l}-Z;L-, ;

1-1,если NIL -Z(4 +2 ,

где А, - очередная цифра операнда; R, - остаток, формируемый в ;-м шаге; N, -промежуточная переменная; Z, - очередная цифра результата; Z, - результат, содержащий / старших разрядов. При этом ( ,...,, а начальными являются значения , .

Использование приведенного алгоритма в избыточной знакоразрядной системе счисления налагает ограничения на форму результата. Чередование цифр результата выполняется по строгим правилам. За по- ложительной цифрой 1 может следовать цифра -1 и наоборот. При этом между ними находится любое число нулей. Однако между одинаковыми зиачащами (отличными от нуля) цифрами не может быть меннее одного нуля. Например, резуль- тат может иметь вид 10101101 и не может быть получен в форме 11011111, если устройство функционирует правильно.

Устройство работает следующим образом.

В исходном состоянии в сумматоре 3 и счетчике 1 записаны нули, в сдвигаю- щем регистре 5 записаны все нули, кроме младшего разряда, где записана единица.

0

0

5

5

5 л

5 0

5

0

В первом такте каждого 1-го цикла вычисления (,2,..., n+1) цифра операнда, имеющая вес и принимающая значение из множества (-1,0,1), прибавляется в г-й разряд сумматора 3 путем выдачи прямого (при Х, ) или обратного кода (при Х, - 1) со сдвигающего регистра 5. На вход переноса в младший разряд сумматора 3 подключен вход 10 устройства. Затем в младший разряд счетчика 1 прибавляется единица, если в знаковом разряде сумматора 3 записан нуль, или вычитается единица, если в знаковом разряде сумматора 3 записана единица. Знаковым разрядом сумматора 3 в i-м такте считается старший разряд. Во втором такте по сигналу блока 4 управления из сумматора 3 вычитается содержимое счетчика 1, если в знаковом разряде сумматора 3 записан нуль, или к сумматору 3 прибавляется содержимое счетчика 1, если в знаковом разряде сумматора 3 записана единица.

При этом блок 4 управления формирует и выдает на выход 15 цифру результата, имеющую вес . Эта цифра равна нулю, если содержимое знакового разряда сумматора 3 не совпадает с его предыдущим значением, единице, если в знаковом разряде сумматора 3 до и после сложения был записан нуль, -1, если в знаковом разряде сумматора 3 до и после сложения была записана единица. Одновременно происходит проверка правильности следования цифр результата. Цепочка элементов D-триггер 6, элемент И 7 обнаруживает появление комбинаций цифр результата 11, а цепочка D-триггер 6, элемент И 8 - появление комбинации 11; в случае появления одной из этих комбинаций на выходе ИЛИ 9 появится сигнал ошибки.

В третьем такте по тем же правилам осуществляется сложение или вычитание кодов сумматора 3 и счетчика 1. Затем в младший разряд счетчика 1 прибавляется или вычитается единица. Цикл заканчивается сигналом на входе 14;/по которому выполняется сдвиг на два разряда влево содержимого сумматора 3, сдвиг на один разряд влево содержимого сдвигающего регистра 5, счетчика 1,

Для получения п-разрядного результата необходимо выполнить циклов вычислений.

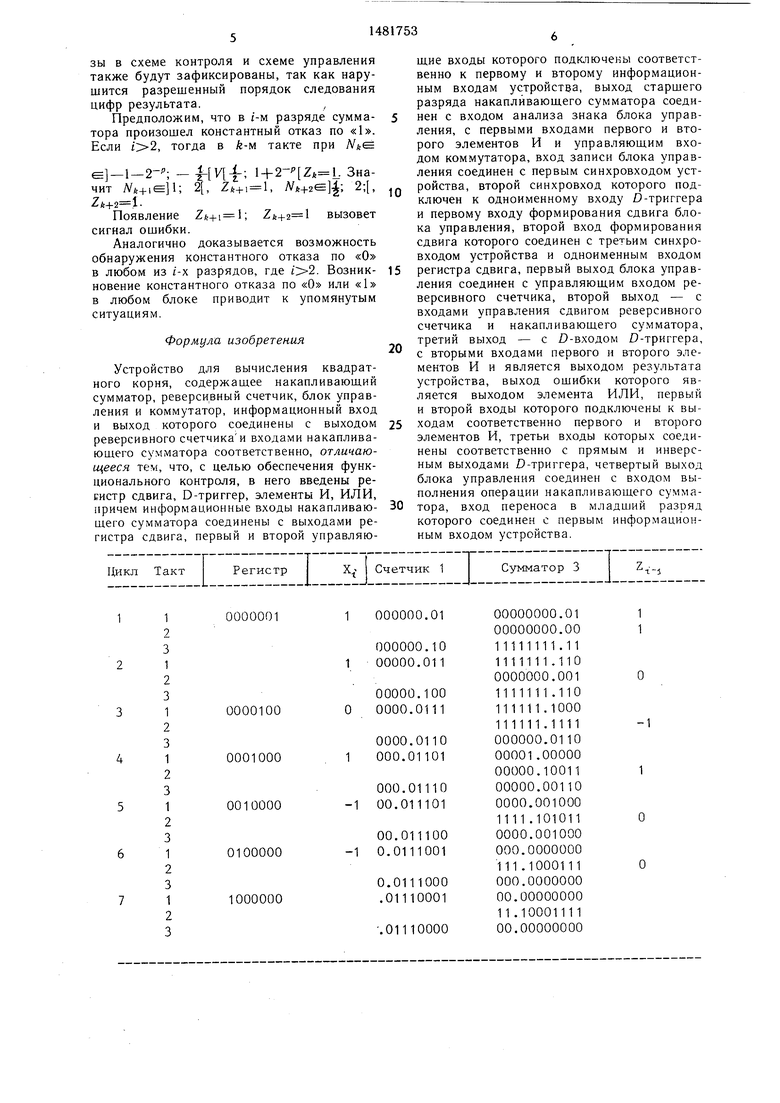

В таблице, где через X, и Z, обозначены цифры аргумента X и результата Z, имеющего вес , приведен пример вычисл е- ния квадратного корня из числа ,11011Т 0,110001. При этом получен результат Z 1,011000 0,110000.

В устройстве для вычисления квадратного корня происходит обнаружение константных неисправностей («1 или «О) в любом блоке, участвующем в формировании цифр результата. Отказы в схеме контроля и схеме управления также будут зафиксированы, так как нарушится разрешенный порядок следования цифр результата.,

Предположим, что в i-м разряде сумма- тора произошел константный отказ по «1. Если , тогда в /г-м такте при

е -1-2- ; - l + Значит 2, , l, 2;,

Появление Zfc+i l; Z/;+2 l вызовет сигнал ошибки.

Аналогично доказывается возможность обнаружения константного отказа по «О в любом из 1-х разрядов, где . Возник- новение константного отказа по «О или «1 в любом блоке приводит к упомянутым ситуациям.

Формула изобретения

Устройство для вычисления квадратного корня, содержащее накапливающий сумматор, реверсивный счетчик, блок управления и коммутатор, информационный вход и выход которого соединены с выходом реверсивного счетчика и входами накапливающего сумматора соответственно, отличающееся тем, что, с целью обеспечения функционального контроля, в него введены ре- систр сдвига, D-триггер, элементы И, ИЛИ, причем информационные входы накапливаю- щего сумматора соединены с выходами регистра сдвига, первый и второй управляю5

Q

5

0

5 0

щие входы которого подключены соответственно к первому и второму информационным входам устройства, выход старшего разряда накапливающего сумматора соединен с входом анализа знака блока управления, с первыми входами первого и второго элементов И и управляющим входом коммутатора, вход записи блока управления соединен с первым синхровходом устройства, второй синхровход которого подключен к одноименному входу D-триггера и первому входу формирования сдвига блока управления, второй вход формирования сдвига которого соединен с третьим синхровходом устройства и одноименным входом регистра сдвига, первый выход блока управления соединен с управляющим входом реверсивного счетчика, второй выход - с входами управления сдвигом реверсивного счетчика и накапливающего сумматора, третий выход - с D-входом D-триггера, с вторыми входами первого и второго элементов И и является выходом результата устройства, выход ошибки которого является выходом элемента ИЛИ, первый и второй входы которого подключены к выходам соответственно первого и второго элементов И, третьи входы которых соединены соответственно с прямым и инверсным выходами D-триггера, четвертый выход блока управления соединен с входом выполнения операции накапливающего сумматора, вход переноса в младший разряд которого соединен с первым информационным входом устройства.

12

ОтЗ

к 3-му

| 1972 |

|

SU413475A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU877529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-26—Подача