Изобретение относится к цифровой вычислительной технике и может быть использовано при создании постоянных перепрограммируемых запоминающих устройств в микропроцессорных системах и микроЭВМ.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности работы в режиме с произвольной выборкой данных,

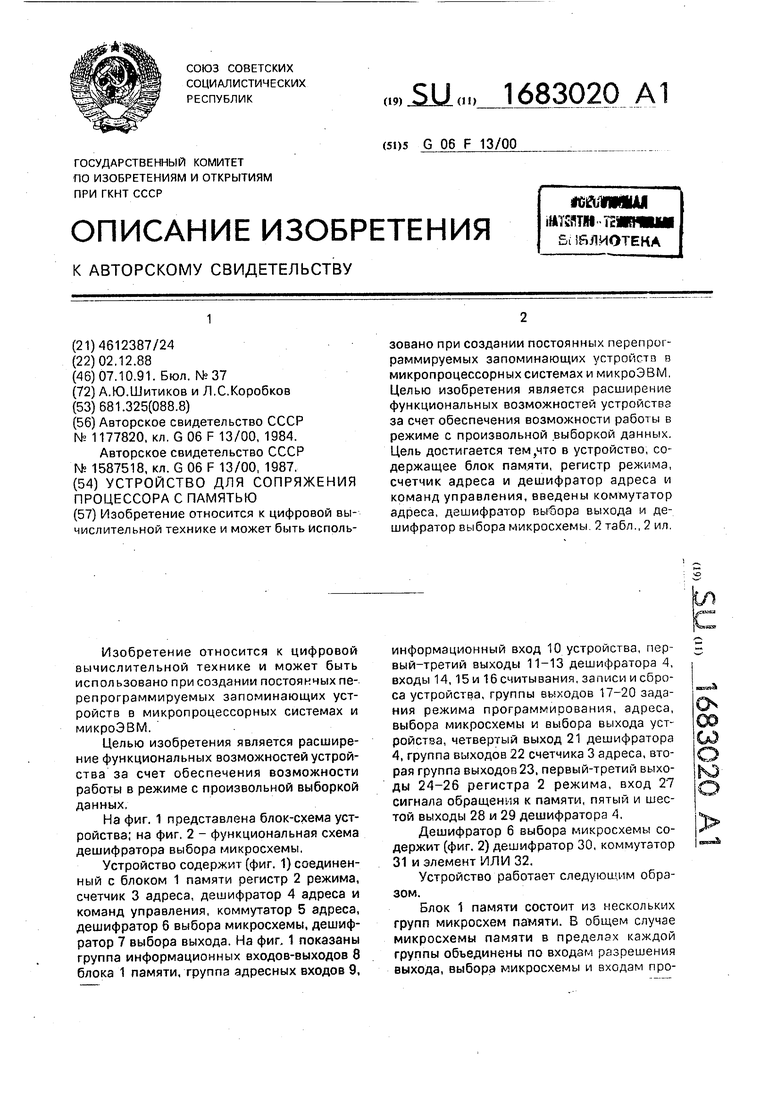

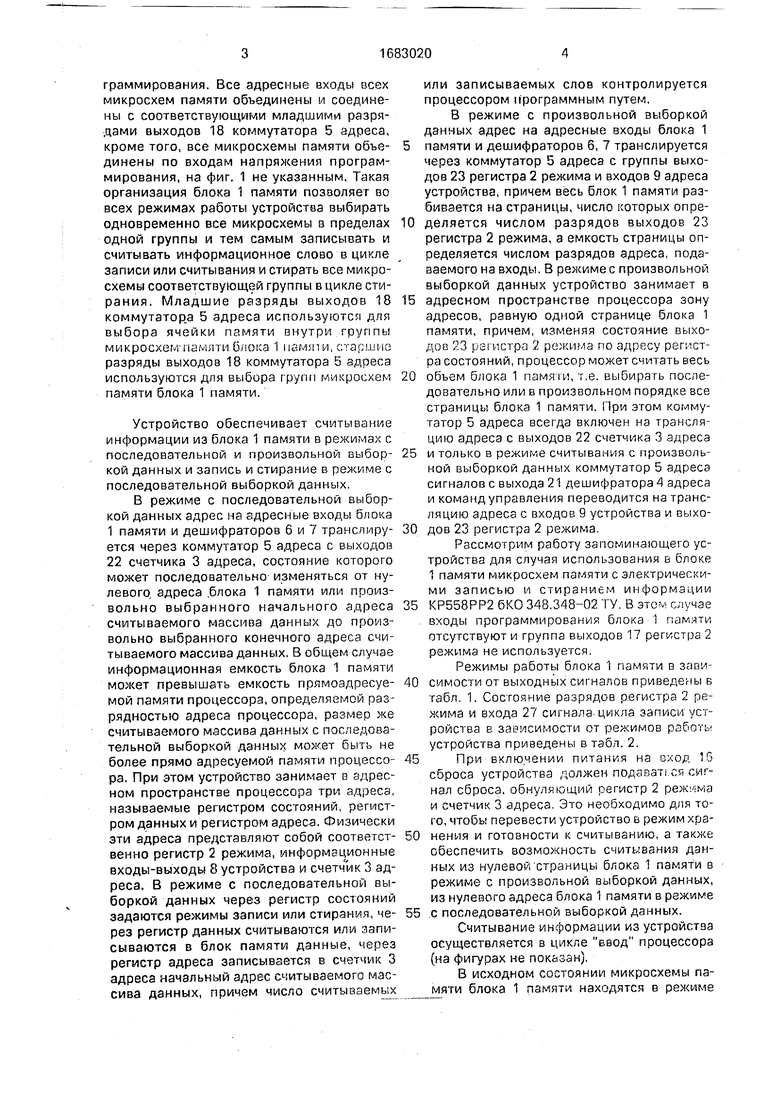

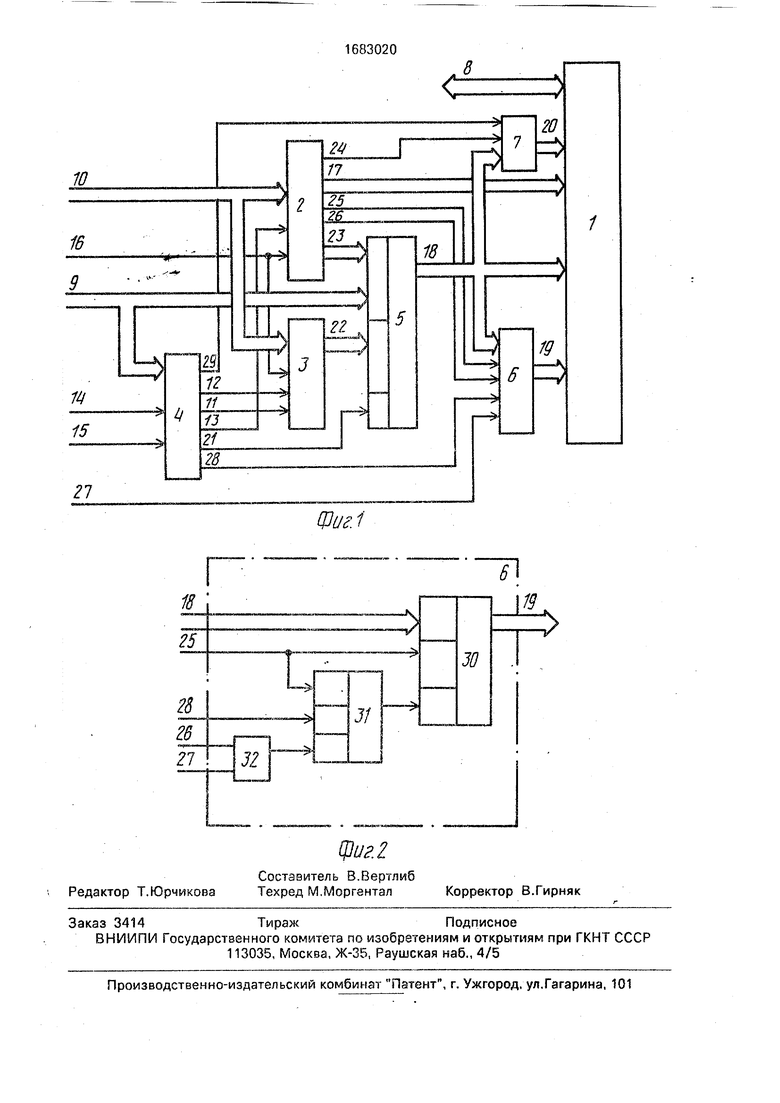

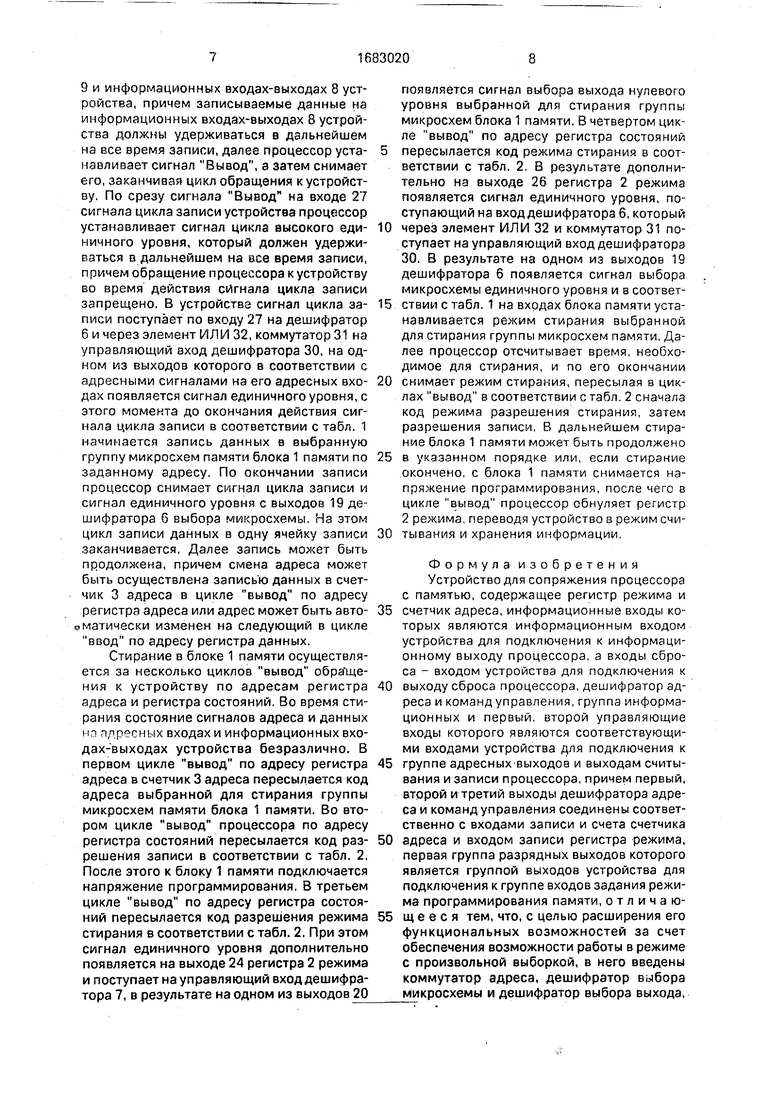

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема дешифратора выбора микросхемы.

Устройство содержит (фиг. 1) соединенный с блоком 1 памяти регистр 2 режима, счетчик 3 адреса, дешифратор 4 адреса и команд управления, коммутатор 5 адреса, дешифратор 6 выбора микросхемы, дешифратор 7 выбора выхода. На фиг, 1 показаны группа информационных входов-выходов 8 блока 1 памяти, группа адресных входов 9,

информационный вход 10 устройства, пер- вый-третий выходы 11-13 дешифратора 4, входы 14,15 и 16 считывания, записи и сброса устройства, группы выходов 17-20 задания режима программирования, адреса, выбора микросхемы и выбора выхода устройства, четвертый выход 21 дешифратора 4, группа выходов 22 счетчика 3 адреса, вторая группа выходов 23, первый-третий выходы 24-26 регистра 2 режима, вход 27 сигнала обращения к памяти, пятый и шестой выходы 28 и 29 дешифратора 4,

Дешифратор 6 выбора микросхемы содержит (фиг. 2) дешифратор 30, коммутатор 31 и элемент ИЛИ 32.

Устройство работает следующим образом.

Блок 1 памяти состоит из нескольких групп микросхем памяти. В общем случае микросхемы памяти в пределах каждой группы объединены по входам разрешения выхода, выбора микросхемы и входам программирования. Все адресные входы всех микросхем памяти объединены и соединены с соответствующими младшими разрядами выходов 18 коммутатора 5 адреса, кроме того, все микросхемы памяти объединены по входам напряжения программирования, на фиг. 1 не указанным. Такая организация блока 1 памяти позволяет во всех режимах работы устройства выбирать одновременно все микросхемы в пределах одной группы и тем самым записывать и считывать информационное слово в цикле записи или считывания и стирать все микросхемы соответствующей группы в цикле сти- рания. Младшие разряды выходов 18 коммутатор.а 5 адреса используются для выбора ячейки памяти внутри группы микросхем памяти блока 1 пам:пи, старшие разряды выходов 18 коммутатора 5 здреса используются для выбора групп микросхем памяти блока 1 памяти,

Устройство обеспечивает считывание информации из блока 1 памяти в режимах с последовательной и произвольной выборкой данных и запись и стирание в режиме с последовательной выборкой данных.

В режиме с последовательной выборкой данных адрес на адресные входы блока 1 памяти и дешифраторов 6 и 7 транслируется через коммутатор 5 адреса с выходов 22 счетчика 3 адреса, состояние которого может последовательно изменяться от нулевого, адреса .блока 1 памяти или произвольно выбранного начального адреса считываемого массива данных до произвольно выбранного конечного адреса считываемого массива данных. В общем случае информационная емкость блока 1 памяти может превышать емкость прямоадресуе- мой памяти процессора, определяемой разрядностью адреса процессора, размер же считываемого массива данных с последовательной выборкой данных может быть не более прямо адресуемой памяти процессора. При этом устройство занимает в адресном пространстве процессора три адреса, называемые регистром состояний, регистром данных и регистром адреса. Физически эти адреса представляют собой соответственно регистр 2 режима, информационные входы-выходы 8 устройства и счетч лк 3 адреса. В режиме с последовательной выборкой данных через регистр состояний задаются режимы записи или стирания, через регистр данных считываются или записываются в блок памяти данные, через регистр адреса записывается в счетчик 3 адреса начальный адрес считываемого массива данных, причем число считываемы

или записываемых слов контролируется процессором программным путем.

В режиме с произвольной выборкой данных адрес на адресные входы блока 1

памяти и дешифраторов 6, 7 транслируется через коммутатор 5 адреса с группы выходов 23 регистра 2 режима и входов 9 адреса устройства, причем весь блок 1 памяти разбивается на страницы, число которых опре0 деляется числом разрядов выходов 23 регистра 2 режима, а емкость страницы определяется числом разрядов адреса, подаваемого на входы. В режиме с произвольной выборкой данных устройство занимает в

5 адресном пространстве процессора зону адресов, равную одной странице блока 1 памяти, причем, изменяя состояние выходов 3 i- ci метра 2 режима по адресу регистра состояний, процессор может считать весь

0 объем блока 1 памяш, т.е. выбирать последовательно или в произвольном порядке все страницы блока 1 памяти. При этом коммутатор 5 адреса всегда включен на трансляцию адреса с выходов 22 счетчика 3 адреса

5 и только в режиме считывания с произвольной выборкой данных коммутатор 5 адреса сигналов с выхода 21 дешифратора 4 адреса и команд управления переводится на трансляцию адреса с входов 9 устройства и выхо0 дов 23 регистра 2 режима.

Рассмотрим работу запоминающею устройства для случая использования в блоке 1 памяти микросхем памяти с электрическими записью и стиранием информации

5 КР558РР2 6КО 348.348-02 ТУ. В STOV случае входы программирования блока 1 памяти, отсутствуют и группа выходов 17 регистра 2 режима не используется.

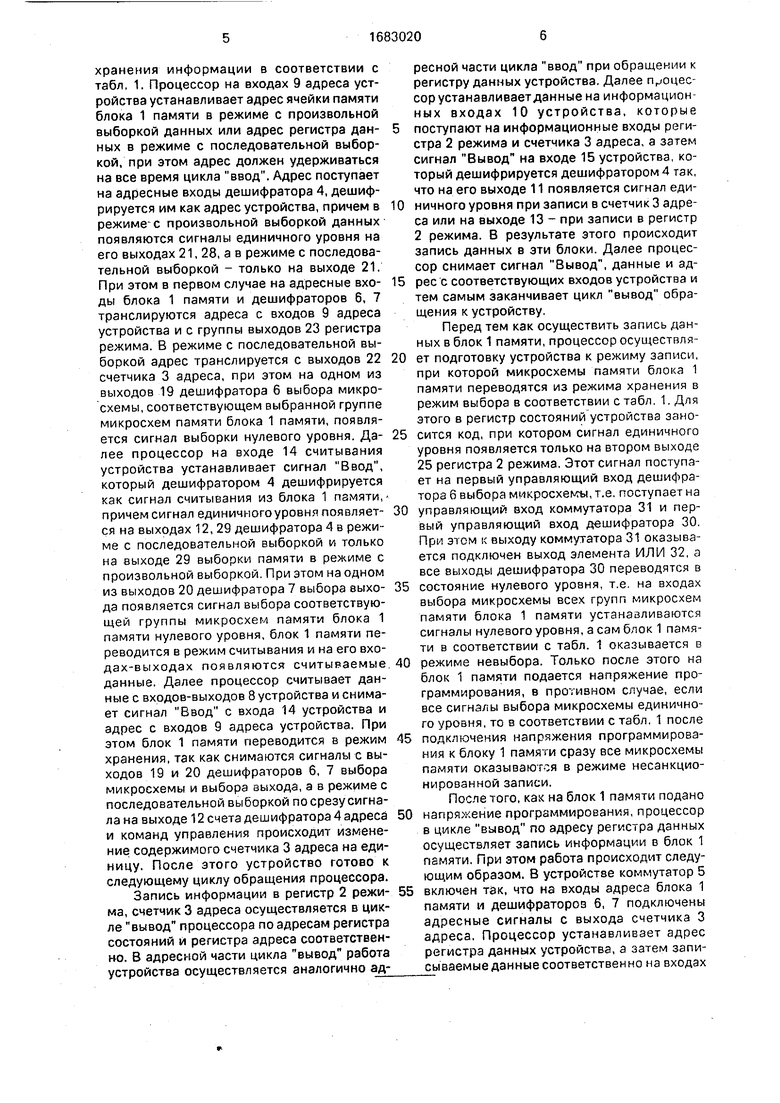

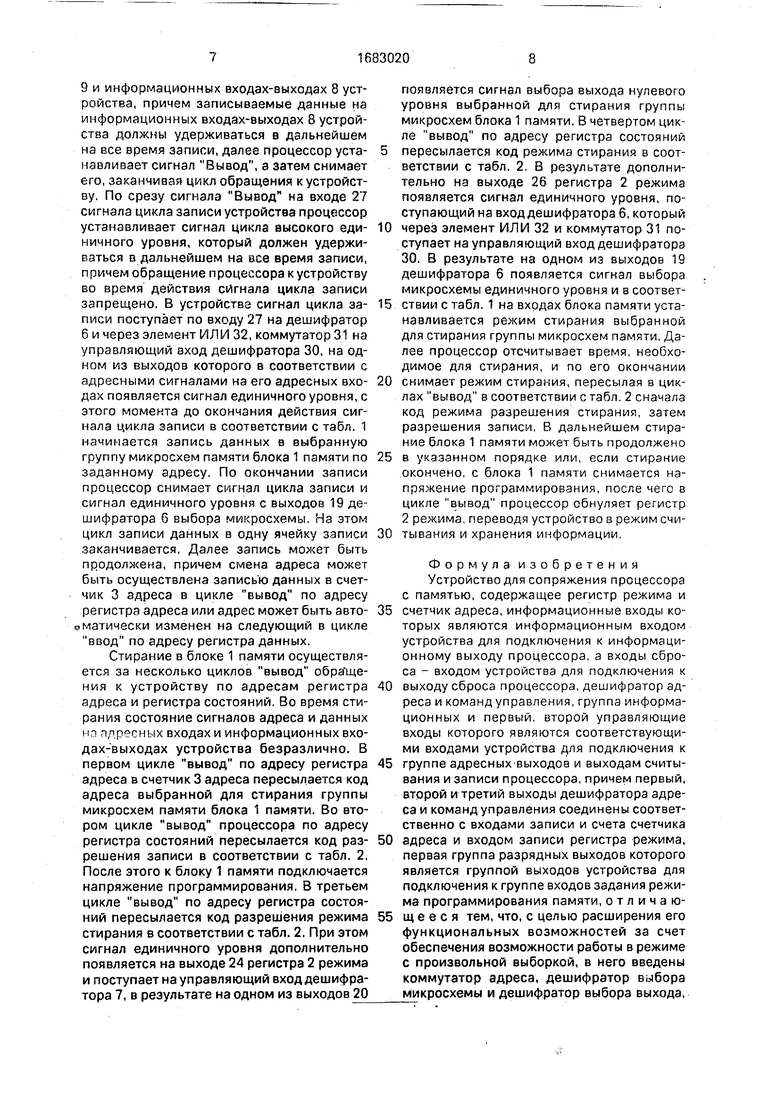

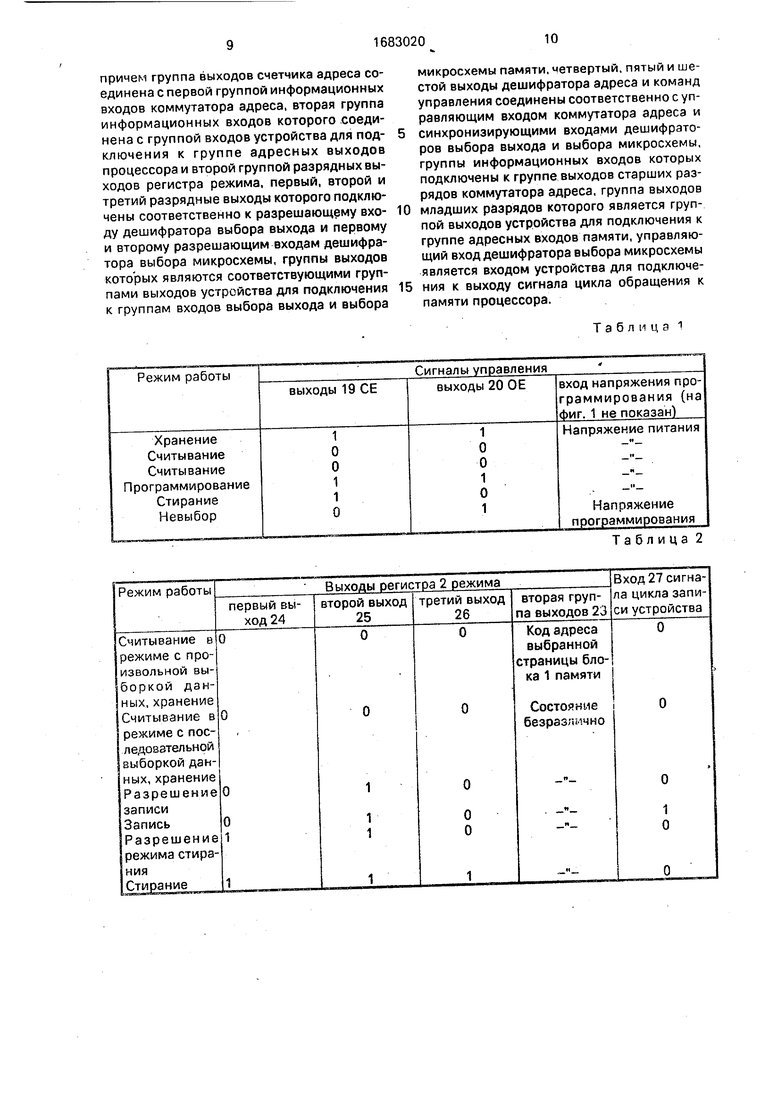

Режимы работы блока 1 памяти в зави0 симости от выходных сигналов приведены в габл. 1. Состояние разрядов регистра 2 режима и входа 27 сигнала цикла записи устройства в зависимости от режимов работа устройства приведены в табл. 2.

5При включении питания на сход 10

сброса устройства должен подавав с я сигнал сброса, обнуляющий регистр 2 режима и счетчик 3 адреса. Это необходимо для того, чтобы перевести устройство в режим хра0 нения и готовности к считыванию, а также обеспечить возможность считывания данных из нулевой страницы блока 1 памяти в режиме с произвольной выборкой данных, из нулевого адреса блока 1 памяти в режиме

5 с последовательной выборкой данных.

Считывание информации из устройства осуществляется в цикле ввод процессора (на фигурах не показан),

В исходном состоянии микросхемы памяти блока 1 памяти находятся в режиме

хранения информации в соответствии с табл, 1. Процессор на входах 9 адреса устройства устанавливает адрес ячейки памяти блока 1 памяти в режиме с произвольной выборкой данных или адрес регистра дан- ных в режиме с последовательной выборкой, при этом адрес должен удерживаться на все время цикла ввод. Адрес поступает на адресные входы дешифратора 4, дешифрируется им как адрес устройства, причем в режиме с произвольной выборкой данных появляются сигналы единичного уровня на его выходах 21, 28, а в режиме с последовательной выборкой - только на выходе 21. При этом в первом случае на адресные вхо- ды блока 1 памяти и дешифраторов 6, 7 транслируются адреса с входов 9 адреса устройства и с группы выходов 23 регистра режима. В режиме с последовательной выборкой адрес транслируется с выходов 22 счетчика 3 адреса, при этом на одном из выходов 19 дешифратора 6 выбора микросхемы, соответствующем выбранной группе микросхем памяти блока 1 памяти, появляется сигнал выборки нулевого уровня. Да- лее процессор на входе 14 считывания устройства устанавливает сигнал Ввод, который дешифратором 4 дешифрируется как сигнал считывания из блока 1 памяти, причем сигнал единичного уровня появляет- ся на выходах 12, 29 дешифратора 4 в режиме с последовательной выборкой и только на выходе 29 выборки памяти в режиме с произвольной выборкой. При этом на одном из выходов 20 дешифратора 7 выбора выхо- да появляется сигнал выбора соответствующей группы микросхем памяти блока 1 памяти нулевого уровня, блок 1 памяти переводится в режим считывания и на его входах-выходах появляются считываемые данные. Далее процессор считывает данные с входов-выходов 8 устройства и снимает сигнал Ввод с входа 14 устройства и адрес с входов 9 адреса устройства. При этом блок 1 памяти переводится в режим хранения, так как снимаются сигналы с выходов 19 и 20 дешифраторов 6, 7 выбора микросхемы и выбора выхода, а в режиме с последовательной выборкой по срезу сигнала на выходе 12 счета дешифратора 4 адреса и команд управления происходит изменение содержимого счетчика 3 адреса на единицу. После этого устройство готово к следующему циклу обращения процессора.

Запись информации в регистр 2 режи- ма, счетчик 3 адреса осуществляется в цикле вывод процессора по адресам регистра состояний и регистра адреса соответственно. В адресной части цикла вывод работа устройства осуществляется аналогично адресной части цикла ввод при обращении к регистру данных устройства. Далее п /оцес- сор устанавливает данные на информационных входах 10 устройства, которые поступают на информационные входы регистра 2 режима и счетчика 3 адреса, а затем сигнал Вывод на входе 15 устройства, который дешифрируется дешифратором 4 так, что на его выходе 11 появляется сигнал единичного уровня при записи в счетчик 3 адреса или на выходе 13 - при записи в регистр 2 режима. В результате этого происходит запись данных в эти блоки. Далее процессор снимает сигнал Вывод, данные и адрес с соответствующих входов устройства и тем самым заканчивает цикл вывод обращения к устройству.

Перед тем как осуществить запись данных в блок 1 памяти, процессор осуществляет подготовку устройства к режиму записи, при которой микросхемы памяти блока 1 памяти переводятся из режима хранения в режим выбора в соответствии с табл. 1. Для этого в регистр состояний устройства заносится код, при котором сигнал единичного уровня появляется только на втором выходе 25 регистра 2 режима. Этот сигнал поступает на первый управляющий вход дешифратора 6 выбора микросхемы, т.е. поступает на управляющий вход коммутатора 31 и первый управляющий вход дешифратора 30. При этом к выходу коммутатора 31 оказывается подключен выход элемента ИЛИ 32, а все выходы дешифратора 30 переводятся в состояние нулевого уровня, т.е. на входах выбора микросхемы всех групп микросхем памяти блока 1 памяти устанавливаются сигналы нулевого уровня, а сам блок 1 памяти в соответствии с табл. 1 оказывается в режиме невыбора. Только после этого на блок 1 памяти подается напряжение программирования, в противном случае, если все сигналы выбора микросхемы единичного уровня, то в соответствии с табл. 1 после подключения напряжения программирования к блоку 1 памяти сразу все микросхемы памяти оказываются в режиме несанкционированной записи.

После того, как на блок 1 памяти подано напряжение программирования, процессор в цикле вывод по адресу регистра данных осуществляет запись информации в блок 1 памяти. При этом работа происходит следующим образом. В устройстве коммутатор 5 включен так, что на входы адреса блока 1 памяти и дешифраторов 6, 7 подключены адресные сигналы с выхода счетчика 3 адреса, Процессор устанавливает адрес регистра данных устройства, а затем записываемые данные соответствен но на входах

и информационных входах-выходах 8 устройства, причем записываемые данные на информационных входах-выходах 8 устройтва должны удерживаться в дальнейшем на все время записи, далее процессор устанавливает сигнал Вывод, а затем снимает его, заканчивая цикл обращения к устройству. По срезу сигнала Вывод на входе 27 сигнала цикла записи устройства процессор станавливает сигнал цикла высокого единичного уровня, который должен удерживаться в дальнейшем на все время записи, п ричем обращение процессора к устройству во время действия сигнала цикла записи запрещено. В устройстве сигнал цикла записи поступает по входу 27 на дешифратор 6 и через элемент ИЛИ 32, коммутатор 31 на управляющий вход дешифратора 30, на одном из выходов которого в соответствии с адресными сигналами на его адресных входах появляется сигнал единичного уровня, с этого момента до окончания действия сигнала цикла записи в соответствии с табл. 1 начинается запись данных в выбранную группу микросхем памяти блока 1 памяти по заданному адресу. По окончании записи процессор снимает сигнал цикла записи и сигнал единичного уровня с выходов 19 дешифратора б выбора микросхемы. На этом цикл записи данных в одну ячейку записи заканчивается, Далее запись может быть продолжена, причем смена адреса может быть осуществлена записью данных в счетчик 3 адреса в цикле вывод по адресу регистра адреса или адрес может быть авто- матически изменен на следующий в цикле ввод по адресу регистра данных.

Стирание в блоке 1 памяти осуществляется за несколько циклов вывод обра ще- ния к устройству по адресам регистра адреса и регистра состояний. Во время стирания состояние сигналов адреса и данных т опросных входах и информационных входах-выходах устройства безразлично. В первом цикле вывод по адресу регистра адреса в счетчик 3 адреса пересылается код адреса выбранной для стирания группы микросхем памяти блока 1 памяти. Во втором цикле вывод процессора по адресу регистра состояний пересылается код разрешения записи в соответствии с табл. 2, После этого к блоку 1 памяти подключается напряжение программирования, В третьем цикле вывод по адресу регистра состояний пересылается код разрешения режима стирания в соответствии с табл. 2. При этом сигнал единичного уровня дополнительно появляется на выходе 24 регистра 2 режима и поступает на управляющий вход дешифратора 7, в результате на одном из выходов 20

появляется сигнал выбора выхода нулевого уровня выбранной для стирания группы микросхем блока 1 памяти. В четвертом цикле вывод по адресу регистра состояний

пересылается код режима стирания в соответствии с табл. 2. В результате дополнительно на выходе 26 регистра 2 режима появляется сигнал единичного уровня, поступающий на вход дешифратора 6, который

через элемент ИЛИ 32 и коммутатор 31 поступает на управляющий вход дешифратора 30. В результате на одном из выходов 19 дешифратора 6 появляется сигнал выбора микросхемы единичного уровня и в соответствии с табл. 1 на входах блока памяти устанавливается режим стирания выбранной для стирания группы микросхем памяти. Далее процессор отсчитывает время, необходимое для стирания, и по его окончании

снимает режим стирания, пересылая в циклах вывод в соответствии с табл. 2 сначала код режима разрешения стирания, затем разрешения записи, В дальнейшем стирание блока 1 памяти может быть продолжено

в указанном порядке или, если стирание окончено, с блока 1 памяти снимается напряжение программирования, после чего в цикле вывод процессор обнуляет регистр 2 режима, переводя устройство в режим считывания и хранения информации.

Формула изобретения Устройство для сопряжения процессора с памятью, содержащее регистр режима и

счетчик адреса, информационные входы которых являются информационным входом устройства для подключения к информационному выходу процессора, а входы сброса - входом устройства для подключения к

выходу сброса процессора, дешифратор адреса и команд управления, группа информационных и первый, второй управляющие входы которого являются соответствующими входами устройства для подключения к

группе адресных выходов и выходам считывания и записи процессора, причем первый, второй и третий выходы дешифратора адреса и команд управления соединены соответственно с входами записи и счета счетчика

адреса и входом записи регистра режима, первая группа разрядных выходов которого является группой выходов устройства для подключения к группе входов задания режима программирования памяти, отличающ е е с я тем, что, с целью расширения его функциональных возможностей за счет обеспечения возможности работы в режиме с произвольной выборкой, в него введены коммутатор адреса, дешифратор выбора микросхемы и дешифратор выбора выхода,

причем группа выходов счетчика адреса соединена с первой группой информационных входов коммутатора адреса, вторая группа информационных входов которого соединена с группой входов устройства для подключения к группе адресных выходов процессора и второй группой разрядных выходов регистра режима, первый, второй и третий разрядные выходы которого подключены соответственно к разрешающему входу дешифратора выбора выхода и первому и второму разрешающим входам дешифратора выбора микросхемы, группы выходов которых являются соответствующими группами выходов устройства для подключения к группам входов выбора выхода и выбора

микросхемы памяти, четвертый, пятый и шестой выходы дешифратора адреса и команд управления соединены соответственно с управляющим входом коммутатора адреса и

синхронизирующими входами дешифраторов выбора выхода и выбора микросхемы, группы информационных входов которых подключены к группе выходов старших разрядов коммутатора адреса, группа выходов

младших разрядов которого является группой выходов устройства для подключения к группе адресных входов памяти, управляющий вход дешифратора выбора микросхемы является входом устройства для подключения к выходу сигнала цикла обращения к памяти процессора.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Запоминающее устройство | 1987 |

|

SU1425693A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при создании постоянных перепрограммируемых запоминающих устройств в микропроцессорных системах и микроЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности работы в режиме с произвольной выборкой данных. Цель достигается тем,что в устройство, содержащее блок памяти, регистр режима, счетчик адреса и дешифратор адреса и команд управления, введены коммутатор адреса, дешифратор выбора выхода и дешифратор выбора микросхемы. 2 табл., 2 ил.

Таблица 2

Щи г. 1

фиг 2

Редактор Т.Юрчикова

Составитель В.Вертлиб Техред М.Моргентал

Корректор В.Гирняк

| Авторское свидетельство СССР № 1177820, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1988-12-02—Подача