гистр 6 вывода питания, блоки 7, 11, 13 и 14 проверки на четность, постоянной памяти, распределения синхронизирующих импульсов и сравнения соответственно. Кроме того, устройство имеет счетчик 8 адреса, регистр 10 входов-выходов, коммутатор 12 выводов питания, триггер 15 результата, многоканальный зонд 16 и индикаИзобретение относится к контрольно-измерительной технике и может быть использовано для контроля цифровых микросхем.

Цель изобретения - расширение области применения устройства за счет возможности контроля нескольких типов микросхем, имеющих различное расположение входов, запрещенных для логических сигналов.

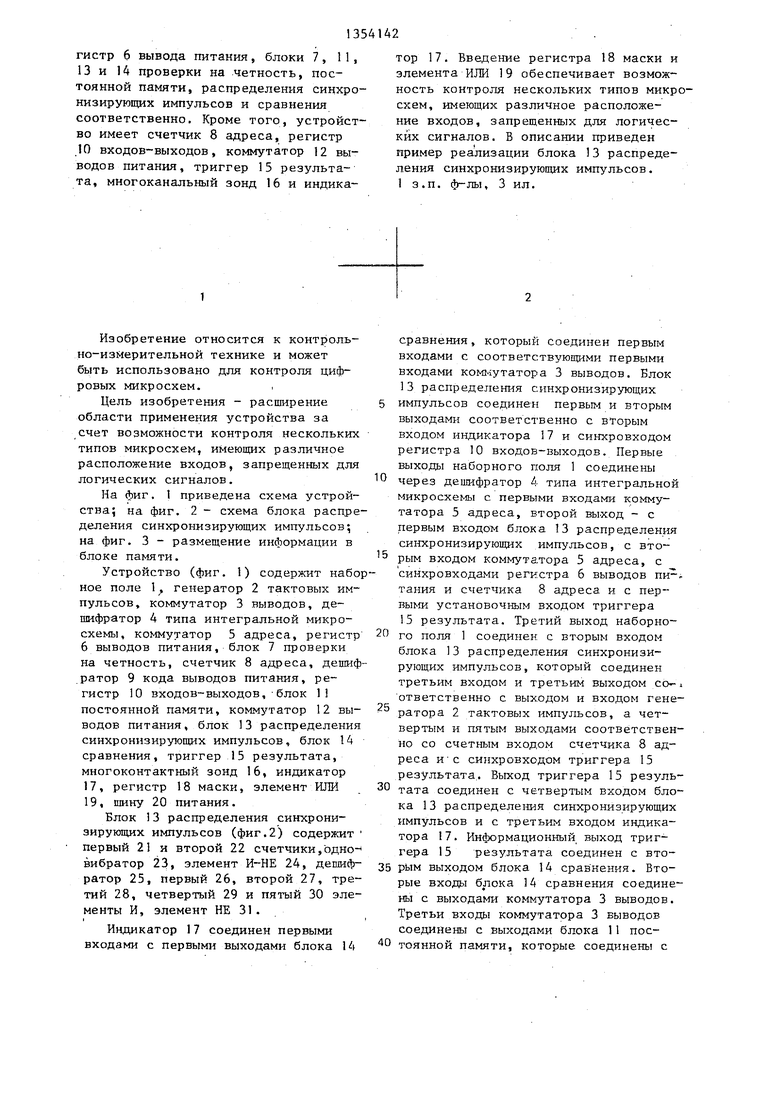

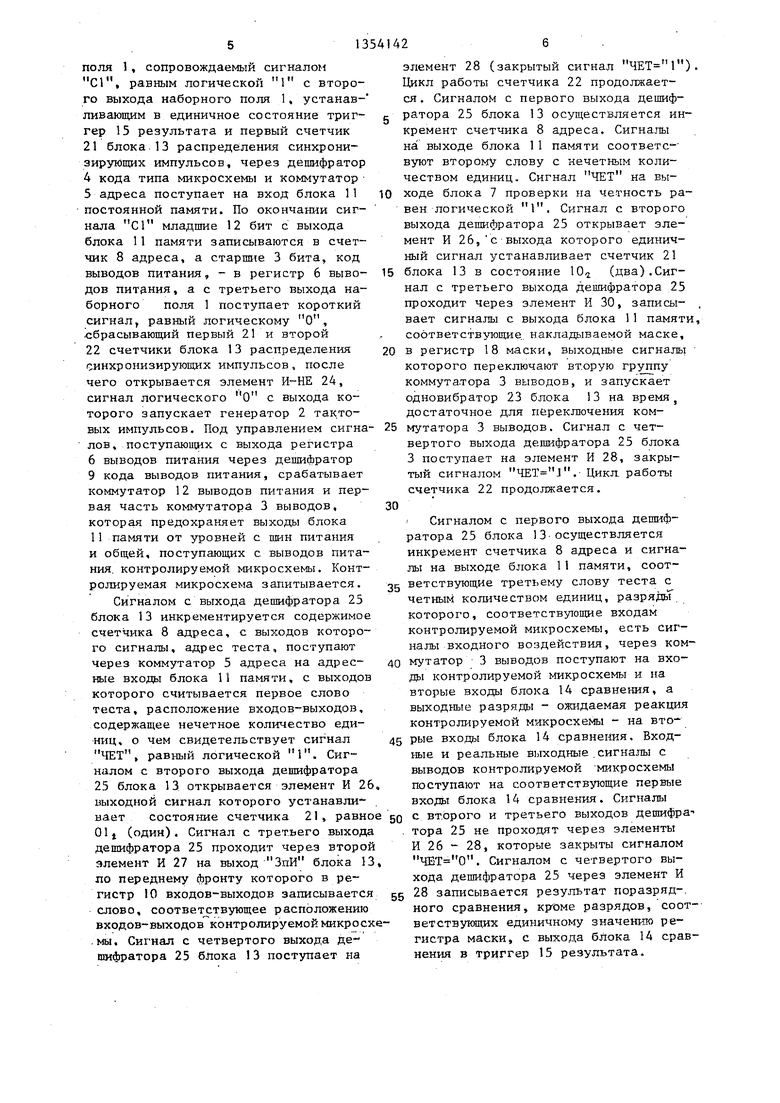

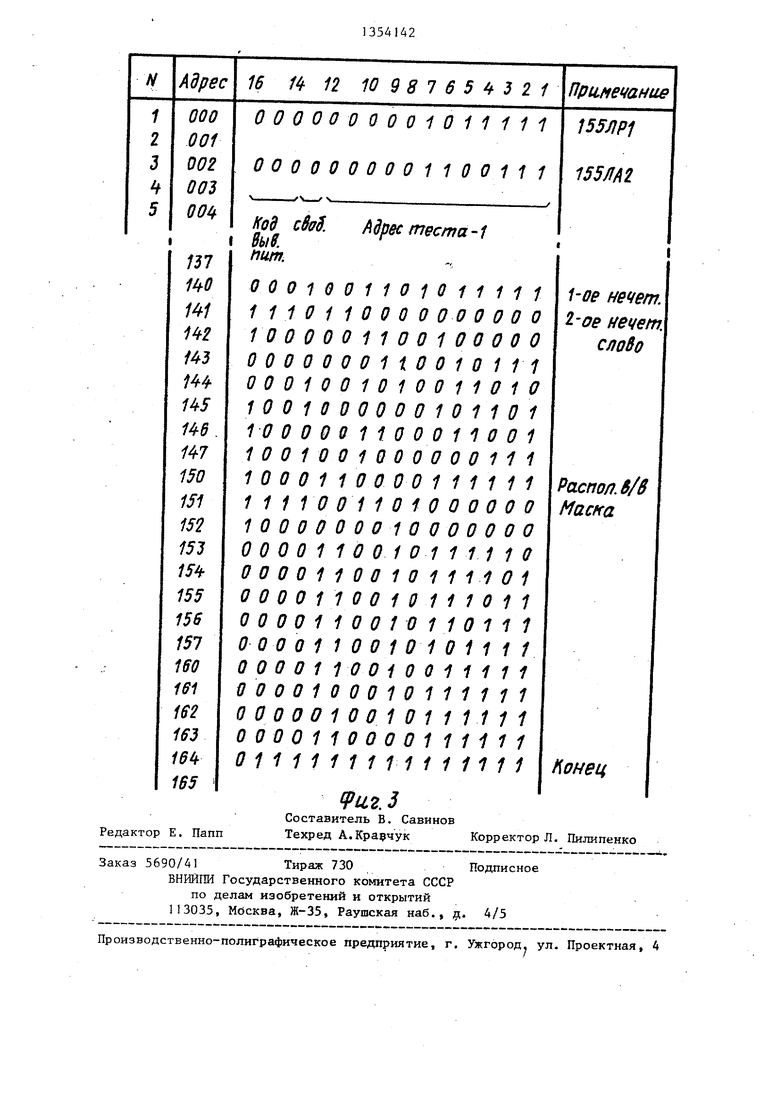

На фиг, 1 приведена схема устройства; на фиг. 2 - схема блока распределения синхронизирующих импульсов; на фиг. 3 - размещение информации в блоке памяти.

Устройство (фиг. 1) содержит набоное поле 1, генератор 2 тактовых импульсов, коммутатор 3 выводов, дешифратор 4 типа интегральной микросхемы, коммутатор 5 адреса, регистр 6 выводов питания, блок 7 проверки на четность, счетчик 8 адреса, дешифратор 9 кода выводов питания, регистр 10 входов-выходов,блок 1 постоянной памяти, коммутатор 12 выводов питания, блок 13 распределения синхронизирующих импульсов, блок 14 сравнения, триггер 15 результата, многоконтактный зонд 16, индикатор 17, регистр 18 маски, элемент ИЛИ 19, шину 20 питания.

Блок 13 распределения синхронизирующих импульсов (фиг.2) содержит первый 21 и второй 22 счетчики,одновибратор 23, элемент И-НЕ 24, дешифратор 25, первый 26, второй 27, третий 28, четвертый 29 и пятый 30 элементы И, элемент НЕ 31.

Индикатор 17 соединен первыми входами с первыми выходами блока 14

тор 17. Введение регистра 18 маски и элемента ИЛИ 19 обеспечивает возможность контроля нескольких типов микросхем, имеющих различное расположение входов, запрещенных для логических сигналов. В описании приведен пример реализации блока 13 распределения синхронизирующих импульсов. 1 з.п. ф-лы, 3 ил.

сравнения, который соединен первым входами с соответствующими первыми входами коммутатора 3 выводов. Блок 13 распределения синхронизирующих

импульсов соединен первым и вторым выходами соответственно с вторым входом индикатора 17 и синхровходом регистра 10 входов-выходов. Первые выходы наборного поля 1 соединены

через дешифратор 4 типа интегральной микросхемы с первыми входами коммутатора 5 адреса, второй выход - с первым входом блока 13 распределения синхронизирующих импульсов, с вторым входом коммутатора 5 адреса, с синхровходами регистра 6 выводов пи-, тания и счетчика 8 адреса и с первыми установочным входом триггера 15 результата. Третий выход наборного поля 1 соединен с вторым входом блока 13 распределения синхронизирующих импульсов, который соединен третьим входом и третьим выходом со- ответственно с выходом и входом гене

ратора 2 тактовых импульсов, а четвертым и пятым выходами соответственно со счетным входом счетчика 8 адреса И с синхровходом триггера 15 результата.. Выход триггера 15 результата соединен с четвертым входом блока 13 распределения синхронизирующих импульсов и с третьим входом индикатора 17. Информационный выход триггера 15 результата соединен с вторым выходом блока 14 срав нения. Вторые входы блока 14 сравнения соединены с выходами коммутатора 3 выводов. Третьи входы коммутатора 3 выводов соединены с выходами блока 11 пос40

тояннои памяти, которые соединены с

3135

соответствующими информационными входами регистра 10 входов-выходов, регистра 6 выводов питания, счетчика 8 адреса и блока 7 проверки на четность. Выходы счетчика 8 адреса соединены с соответствующими третьими входами коммутатора 5 адреса. Выход коммутатора 5 адреса соединен с входами блока 11 постоянной памяти Выход блока 7 проверки на четность соединен с пятым входом блока 13 распределения синхронизирующих импульсов, выходы регистра 6 выводов питания соединены через дешифратор 9 кода выводов питания с четвертыми входами коммутатор а 3 выводов И с управляющими входами коммутатора 12 выводов питания, который соединен первым и вторым потенциальными входами соответственно с общей шиной и шиной питания устройства, выходами - с соответствующими выводами многоконтактного зонда 16 и с соответствующими первыми входами блока 14 сравнения. Шестой выход блока 13 распределения синхронизирующих импульсов соединен с синхровходом регистра 18 маски, информационные входы которого соединены с соответствующими выходами блока II постоянной памяти. Регистр 18 маски прямыми выходами соединен с первыми входами элемента ИЛИ 19, вторые входы которого соединены с соответствующими выходами регистра 10 входов

выходов, а выхода элемента ИЛИ 19 соединены с первой группой входов коммутатора 3 выводов, инверсными выходами регистр 18 маски соединен с третьим входом блока 14 сравнения.

Блок 13 распределения синхрони- -5ирующих импульсов содержит первый счетчик 21, который соединен S-BXO- дом с первым входом блока, С-вхо- дом - с выходом первого элемента И 26. Первый элемент И 26 соединен первым входом с пятым входом блока, с первым входом второго элемента И 27 и с инвертирующим входом третьего элемента И 28, вторым входом - с первым выходом дешифратора 25. Вторым выходом дешифратора 25 Соединен с четвертым выходом блока, третьим выходом - с вторым входом второго элемента И 27, четвертьм выходом - с н инвертирующимвходом третьего элемента И 28, который соединен выходом с пятым выходом блока. Второй счетчик 22 соединен выходамис

-5

10

0

5

входами дешифратора 25, С-входом - с третьим входом блока,R-входом- с R-входом первого счетчика 21 и вторым входом блока.Прямой выход первого разряда первого счетчика 2 1 соединен с третьим входом второго элемента И 27, выход которого соединен с вторым выходом блока. Выход элемента И-НЕ 24 соединен с третьим выходом блока, первый вход - выходом одновибра- - тора 23, второй вход - с четвертым входом блока. Первый вход четвертого элемента И 29 соединен с прямым вы- 15 ходом первого разряда первого счетчика 21, а выход - с первым выходом блока и с входом элемента НЕ 31. Выход элемента НЕ 31 соединен с третьим входом элемента И-НЕ 24. Пя- тьп элемент И 30 выходом соединен с шестым выходом блока и с входом одновибратора 23, первым и вторым входами соответственно - с первым и вторым входами второго элемента И 27, третьим входом - с прямым выходом второго разряда первого счетчика 2I и с вторым входом четвертого элемен- |та И 29.

Блок 11 постоянной памяти (фиг.З) в каждом слове первой части содержит: 1-12 биты - адрес начала теста минус один; бит 13 - свободен; 14-16 биты - код выводов питания. Во второй части содержит; первое слово (нечетное количество единиц) - указывает на расположение входов-выходов контролируемой микросхемы (логическая 1 - вход, логическая О - выход);

второе слово (нечетное количество единиц) - маска, значение логический

1 которой соответствуют входам, на которые зепрещена подача логических сигналов; третье и другие слова - собственно тест на данную микросхему; последнее слово - признак конца (нечетное количество; единиц). Номера разрядов памяти теста соответствуют номерам выводов контролируемой микросхемы, дополнение слов до нечетности количества единиц производится за счет разрядов, соответствующих выводов питания или свободных, признак конца, с целью экономии памяти, может быть .первым (нечетным) словом следуклцего теста. Устройство работает следующим образом.

Опред еленной комбинацией кнопок сигнал с первого выхода наборного

0

5

0

5

0

5

оля 1, сопровождаемый сигналом С1, равным логической 1 с второго выхода наборного поля 1, устанав- ивающим в единичное состояние триг- g гер 15 результата и первый счетчик

21блока.13 распределения синхронизирующих импульсов, через дешифратор

4кода типа микросхемы и коммутатор

5адреса поступает на вход блока 11 ю постоянной памяти. По оконча ши сигнала С1 младшие 12 бит с выхода блока 11 памяти записываются в счетчик 8 адреса, а старшие 3 бита, код выводов питания, - в регистр 6 выво- 15 дов питания, а с третьего выхода наборного поля 1 поступает короткий сигнал, равный логическому О, ;брасывающий первый 21 и второй

22счетчики блока 13 распределения 20 синхронизирующих импульсов, после

чего открывается элемент И-НЕ 24, сигнал логического О с выхода которого запускает генератор 2 так.то- вых импульсов. Под управлением сигна- 25 лов, поступающих с выхода регистра

6выводов питания через дешифратор

9 кода выводов питания, срабатывает коммутатор 12 выводов питания и первая часть коммутатора 3 выводов, 30 которая предохраняет выходы блока 11 памяти от уровней с шин питания и общей, поступающих с выводов питания, контролируемой микросхемы. Контролируемая микросхема запитывается. gg

Сигналом с выхода дешифратора 25 блока 13 инкрементируется содержимое счетчика 8 адреса, с выходов которого сигналы, адрес теста, поступают через коммутатор 5 адреса на адрес- 40 ные входы блока 11 памяти, с выходов которого считывается первое слово теста, расположение входов-выходов, содержащее нечетное количество единиц, о чем свидетельствует сигнал 45 ЧЕТ, равный логической 1. Сигналом с второго выхода дешифратора 25 блока 13 открывается элемент И 26, выходной сигнал которого устанавливает состояние счетчика 21, равное gg 01t (один). Сигнал с третьего выхода дешифратора 25 проходит через второй элемент И 27 на выход ЗпИ блока 13, по переднему фронту которого в регистр 10 входов-выходов записывается gg слово, соответствующее расположению входов-выходов контролируемой микросхе- .мы. Сигнал с четвертого выхода дешифратора 25 блока 13 поступает на

элемент 28 (закрытый сигнал Цикл работы счетчика 22 продолжается . Сигналом с первого выхода дешифратора 25 блока 13 осуществляется инкремент счетчика 8 адреса. Сигналы на выходе блока 1 1 памяти соответс - вуют второму слову с нечетным количеством единиц. Сигнал ЧЕТ на выходе блока 7 проверки на четность равен логической 1. Сигнал с второго выхода дешифратора 25 открывает элемент И 26, с Выхода которого единичный сигнал устанавливает счетчик 21 блока 13 в состояние 10 (два).Сигнал с третьего выхода дешифратора 25 проходит через элемент И 30, записывает сигналы с выхода блока II памят соответствующие., накладываемой маске, в регистр 18 маски, выходные сигналь: которого переключают вторую группу коммутатора 3 выводов, и запускает одновибратор 23 блока 13 на время, достаточное для переключения коммутатора 3 выводов, Сигнал с четвертого выхода дешифратора 25 блока 3 поступает на элемент И 28, закрытый сигналом .- Цикл работы счетчика 22 продолжается.

Сигналом с первого выхода дешифратора 25 блока 13-осуществляется инкремент счетчика 8 адреса и сигналы на выходе блока 11 памяти, соответствующие третьему слову теста с четным количеством единиц, разряды которого, соответствуюш 1е входам контролируемой микросхемы, есть сигналы входного воздействия, через коммутатор 3 выводов поступают на входа контролируемой микросхемы и на вторые входы блока 14 сравнения, а выходные разряды - ожидаемая реакция контролируемой микросхемы - на вторые входы блока 14 сравнения. Входные и реальные выходные.сигналы с выводов контролируемой микросхемы поступают на соответствующие первые входы блока 14 сравнения. Сигналы с второго и третьего выходов дешифратора 25 не проходят через элементы И 26 28, которые закрыты сигналом . Сигналом с четвертого выхода дешифратора 25 через элемент И 28 записывается результат поразряд-. ного сравнения, кр оме разрядов, соот ветстэуннцих единичному значению регистра маски, с выхода блока 14 сравнения в триггер 15 результата.

Если триггер 15 результата сброшен, т.е. обнаружена ошибка (при этом ), то закрывается элемент И-НЕ 24 блока 13, единичный сигнал с выхода которого блокирует генератор 2 тактовых импульсов, а индикатор 17 высвечивает позицию де фектного вывода. Работа устройства завершена.

В противном случае приведенный цикл повторяется до считывания блок 11 памяти третьего нечетного слова - признака конца теста, после чего состояние счетчика 21 блока 13 ста- новится 112 (три) и единичный сигнал с выхода элемента И 29 -блокируе работу генератора 2 тактовых импульсов, с выхода элемента И 29 сигнал поступает на второй вход индикатора 17, который высвечивает положительный результат контроля миросхемы. Повторный запуск устройств происходит нажатием кнопок наборног поля 1.

Формула изобретения

1, Устройство для контроля цифрог вых интегральных микросхем, содержа- щее индикатор, соединенньп первыми входами с первыми выходами блока сравнения, соединенного первыми входами с соответствующими первыми входами коммутатора выводов,блок распре деления синхронизирующих импульсов, соединенный первым и вторым выходами соответственно с вторым входом индикатора и синхровходом регистра входов-выходов, наборное поле, пер- вые выходы которого соединены через дешифратор типа интегральной микросхемы с первыми входами коммутатора адреса, второй выход - с первым входом блока распределения синхронизи- рующих импульсов, с вторым входом коммутатора адреса, с синхровходами регистра выводов питания и счетчика адреса и с первым установочным входом триггера результата, третий вы- ход наборного поля соединен с вторым входом блока распределения синхронизирующих импульсов, соединенного третьим выходом и третьим входом соответственно с входом и выходом ге- нератора тактовых импульсов, четвертым и пятым выходами - соответственно со счетным входом счетчика адреса и с синхровходом триггера резуль

тата, соединенного выходом с четвертым входом блока распределения синхронизирующих импульсов и с третьим входом индикатора, информационным входом - с вторым выходом блока сравнения , соединенного вторыми входами с выходами, коммутатора выводов, соеди- ненного третьими входами с выходами блока постоянной памяти, которые соединены с соответствующими информационными входами регистра входов- выходов, регистра выводов питания, счетчика адреса и блока проверки на четность, выходы счетчика адреса соединены с соответствующими третьими входами коммутатора адреса, выход которого соединен с входами блока постоянной памяти, выход блока проверки на четность соединен с пятым входом блока распределения синхронизирующих импульсов, выходы регистра выводов питания соединены через дешифратор кода выводов питания с четвертыми входами коммутатора выводов и с управляющими входами коммутатора выводов питания, соединенного первым и вто- -рым потенциальными входами соответственно с общей шиной и шиной питания устройства, выходами - с соответст-. вующими выводами многоконтактного зонда и с соответствующими тервыми входами блока сравнения, О Т л и - чающееся тем, что, с целью расширения области применения устрой- ства, в него введены регистр маски и элемент РШИ, причем шестой выход блока распределения синхронизирующих импульсов соединен с синхровходом регистра маски, информационные входы которого соединены с соответствующими выходами блока постоянной памяти, регистр маски прямыми выходами соединен с первыми входами элемента ИЛИ, вторые входы которого соединены с соответствующими выходами регистра входов-выходов, а выходы элемента ИЛИ соединены с первой группой входов коммутатора выводов, инверсными выходами регистр маски соединен с третьими входами блока сравнения .

2. Устройство по п. 1, о т л и - чающееся тем, что блок распределения синхронизирующих импульсов содержит первый счетчик, соединенный S-входом с первым входом блока, С-вхором - с выходом первого элемента И, соединенного первым

91354142.

ходом с пятым входом блока, с перым входом второго элемента И и с инертирующим входом третьего элемена И, вторым входом - с первым выхоом дешифратора, соединенного втоым выходом с четвертым выходом блоа, третьим выходом--- с вторым входом второго элемента И, четвертым выходом - с неинвертирукщим входом ю. третьего элемента И, соединенного выходом с пятым выходом блока, второй счётчик, соединенный выходами с входами дешифратора, С-входом - с третьим входом блока, R-входом - 15 с R-вхадом первого счетчика и вторым входом блока, .Прямой выход первого разряда первого счетчика соединен с третьим входом второго элемен- та И, выход которого соединен с вто- 20 рым выходом блока, элемент И-НЕ,

вых вы хо с и пе со ра с эл с 1Ъ1 ше ви со вх вх ра рь та

42.

10

выход которого соединен с третьим выходом блока, первый вход - с выходом одновибратора, второй вход - с четвертым входом блока, четвертый и пятый элементы И и элемент НЕ, первый вход четвертого элемента И соединен с прямым выходом первого разряда первого счетчика, а выход - с первым выходом блока и с входом элемента НЕ, выход которого соедине с третьим входом элемента И-НЕ, пя- 1Ъ1й элемент И выходом соединен с шестым выходом блока и с входом одн вибратора, первым и вторым входами соответственно с первым и вторым входами второго элемента И, третьим входом - с Прямым выходом второго разряда первого счетчика и с вто рьи входом четвертого элемен та И.

Редактор E. Папп

Составитель В. Савинов Техред А.Кравчук

Заказ 5690/41 Тираж 730Подписное

ВНИЙПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород ул. Проектная, 4

9u2,3

Корректор Л. Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

Изобретение относится к контрольно-измерительной технике. Цель .изобретения расширение области применения устройства контроля цифровых интегральных схем. Устройство содержит наборное поле 1, генератор 2 тактовых импульсов, -коммутатор 3 выводов, дешифратор 4 типа интегральной микросхемы, дешифратор 9 Кода выводов питания, коммутатор 5 адреса, ре(Л С со ел ю

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-23—Публикация

1986-03-14—Подача