;Ш1

1

сд

ч

bzz

h

X

05

fff

ff

Г2

73(

f4.

Изобретение относится, к вычислительной технике и может быть использовано при проектировании микросхем памяти,

Цель изобретения - повышение усточивости оперативного запоминающего устройства (ОЗУ) к кратковременному воздействию дестабилизируклцих факторов (ДФ)f не приводящему к необратимому изменению параметров транзисторов .элементов памяти ОЗУ.

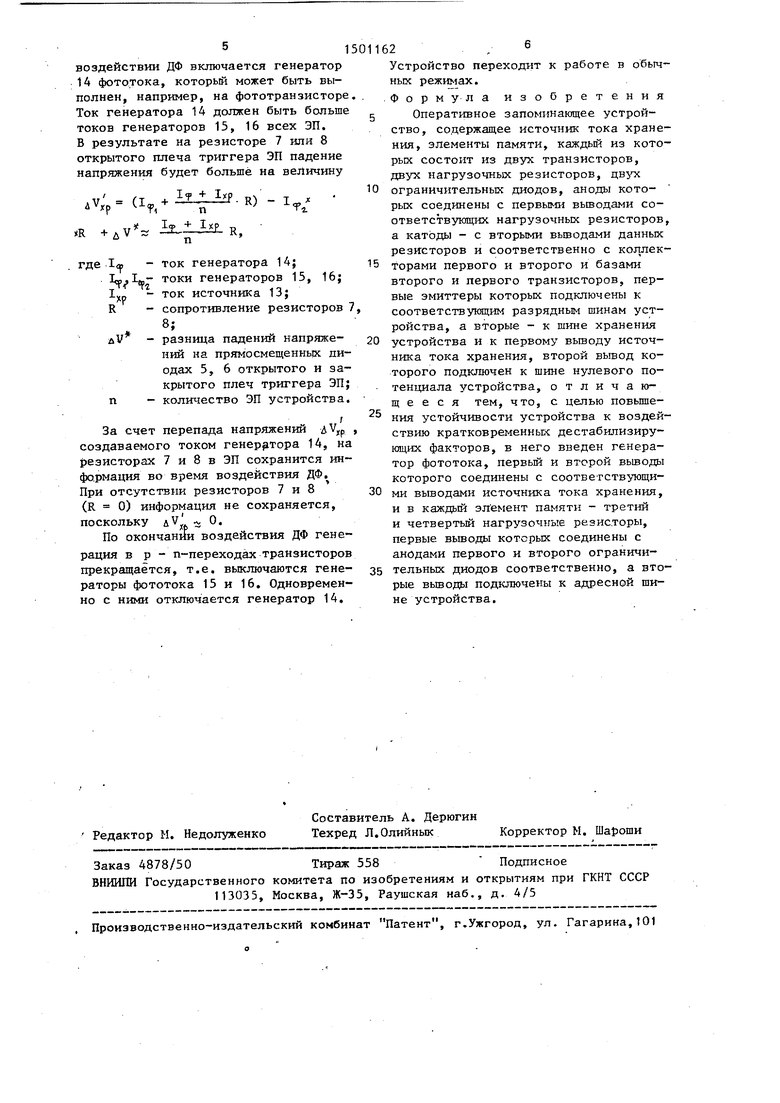

На чертеже представлена электричекая схема ОЗУ.

Предлагаемое ОЗУ содержит элементы памяти (ЭП), каждый из которых состоит из двух транзисторов 1 и 2, первого и второго нагрузочных резисторов 3 и 4, двух ограничительных диодов 5, 6, третьего и четвертого нагрузочных резисторов 7 и 8, адресную шину 9, шину 10 хранения, разрядные шины 115 12, источник 13 тока хранения, генератор 14 фототока.

Генераторы фототока 15 и 16 отражают суммарный ток р-п-транзнеторов переходов ЭП, возникающий из-за воз- действия ДФ.

ОЗУ работает следукщим образом.

Б режиме хранения сопротивление нагрузок плеч ЭП определяется резисторами 3, 4, так как источник 13 задает через каждый ЭП такой ток, чт на резисторе 3 или 4 открытого плеча триггера падает напряжение, равное примерно 0,5 V, где V - падение напряжения на открытом диоде 5, 6. В результате диод 5 или 6 открытого плеча оказывается под таким же прямы смещением 0,5 V, так что ток через него практически не течет. Падение напряжения на нагрузке закрытого плеча триггера определяется током базы открытого транзистора 1 или 2. Этот ток в } раз, где - коэффициент у.сипения транзистора по току, меньше тока его коллектора, поэтому и падение напряжения на резисторе 3 или 4 закрытого плеча ЭП в раз меньше, т.е. 0,5 . В результате диод 5 или 6 закрытого плеча окажется под смещением, близким к нулевому и ток через него также не протекает Номиналы резисторов 7, 8 более чем на порядок меньше номиналов резисторов 3 и 4, поэтому падением напряжения на них можно пренебречь. Таким

образом, разность потенциалов коллекторов транзисторов 1 и 2 составит

5

0

5

0

д

5

5

0

5

AV,

1,

0,5 V(1 - j)

)гр j-- V -j-; 0,5 V .

В режиме выборки повьш1ается потенциал адресной шины 9. В результате повышается и потенциал шины 10.

Через первые эмиттеры транзисторов 1 и 2 ток перестает протекать. Ток записи или считывания протекает через второй эмиттер одного из транзисторов. 1 и 2. При этом транзистор работает в квазинасыщенном режиме, т.е. его коллекторный переход оказывается под прямым смещением. Однако наличие ограничительных диодов 5 и 6 не позволяет достигнуть этому прямому смещению величины V, обеспечивая высокое быстродействие ЭП. Так как номинал резисторов 7 и 8 мал, то падение напряжения на них в режиме выборки 0,15-0,2 В не оказывает существенного влияния на быстродействие ЭП из-за увеличения степени насьш1е- ния открытого транзистора.

При кратковременном воздействии на микросхему памяти ДФ обращение к ней запрещается, т.е. все ЭП находятся в режиме хранения. Воздействие ДФ вызьюает генерацию заряда в р - п-переходах транзисторов и, следовательно, возникновение фототоков, которые отражены генераторами 15 и 16. Величина этих токов может быть значительно больше величины тока хранения ЭП более чем в 2 раза. Фототоки возникают независимо от состояния ЭП одновременно в обоих его плечах, вызьшая увеличение падений напряжений на резисторах 3 и 4 до тех пор, пока не откроются днод}ы 5 и 6. Дифференциальные сопротивления открытых диодов 5 и 6 малы, поэтому небольшой ток хранения, задаваемый источником 13 тока, не в состоянии обеспечить на диодах 5 и 6 перепад напряжений, достаточкьм для сохранения информации. Резисторы 7, 8 обеспечивают увеличение общего дифференциального сопротивления нагрузки, так как они включены последовательно с диодами 5, 6. Однако только увеличение сопротивления нагрузок ЭП недостаточно для сохранения в нем информации, так как по-прежнему мал ток хранения. Для того чтобы ЭП сохранил записанную в нем информацию, при

515011

воздействии ДФ включается генератор 14 фототока, который может быть выполнен, например, на фототранзисторе, . Ток генератора 14 должен быть больше токов генераторов 15, 16 всех ЭП. В результате на резисторе 7 или 8 открытого плеча триггера ЭП падение напряжения будет больше на величину

AVxp (1,If +

лК

де 1а - ток генератора 14;

. IM.IJ-- токи генераторов 15, 16;

15

Р

лУ

ток источника 13; сопротивление резисторов 7, 8;

разница падений напряже- 20 НИИ на прямосмещенньк диодах 5, 6 открытого и закрытого плеч триггера ЭП; количество ЭП устройства.

За счет перепада напряжений V,,p создаваемого током генератора 14, на резисторах 7 и 8 в ЭП сохранится ин- фо.рмация во время воздействия ДФ. При отсутствии резисторов 7 и 8 (R 0) информация не сохраняется,

поскольку AV .V; 0.

По окончании воздействия ДФ генерация в р - п-переходах транзисторов прекращается, т.е. выключаются генераторы фототока 15 и 16. Одновременно с ними отключается генератор 14,

0

5

0

5

0

5

62,6

Устройство переходит к работе в обычных режимах. Формула изобретения

Оперативное запоминающее устройство, содержащее источник тока хранения, элементы памяти, каждьй из кото- рьк состоит из двух транзисторов, двух нагрузочных резисторов, дв зтс ограничительных диодов, аноды которых соединены с первыми вьшодами соответствующих нагрузочных резисторов, а катоды - с вторыми вьшодами данных резисторов и соответственно с коллекторами первого и второго и базами второго и первого транзисторов, первые эмиттеры которых подключены к соответствуклцим разрядным шинам устройства, а вторые - к шине хранения устройства и к первому вьшоду источника тока хранения, второй вывод которого подключен к шине нулевого потенциала устройства, отличающееся тем, что, с целью повьшге- ния устойчивости устройства к воздействию кратковременных дестабилизирующих факторов, в него введен генератор фототока, первьй и второй вьшоды которого соединены с соответствующими выводами источника тока хранения, и в каждый эл емент па1-{яти - третий и четвертьй нагрузочные резисторы, первые вьшоды которых соединены с анодами первого и второго ограничительных диодов соответственно, а вторые вьшоды подключены к адресной шине устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1987 |

|

SU1501161A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1569901A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Запоминающее устройство | 1990 |

|

SU1751814A1 |

| Элемент памяти | 1987 |

|

SU1474736A1 |

| Генератор тока для устройств выборкииНфОРМАции из НАКОпиТЕля | 1979 |

|

SU851490A1 |

| Релаксационный генератор | 1977 |

|

SU702491A1 |

| Инвертор | 1988 |

|

SU1566478A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

Изобретение относится к вычислительной технике и может быть применено в микросхемах памяти. Целью изобретения является повышение устойчивости оперативного запоминающего устройства (ОЗУ) к кратковременному воздействию дестабилизирующих факторов. Поставленная цель достигается тем, что в устройство введен генератор 14 фототока, а в каждый элемент памяти - третий и четвертый нагрузочные резисторы 7,8. При воздействии на ОЗУ дестабилизирующих факторов включается генератор 14 фототока и поддерживает на резисторах 7,8 перепад напряжений, необходимый для сохранения информации. 1 ил.

| Валиев К.А., Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Советское радио, 1979, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Там же, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-28—Подача