Изобретение относится к цифровой- вычислительной технике и может, бы ть использовано при построении устройств сдвига, блоков памяти и блоков обра- бртки универсальных цифровых вычислительных Г211ШН.

Цель изобретения - повышение быстродействия формирователя.

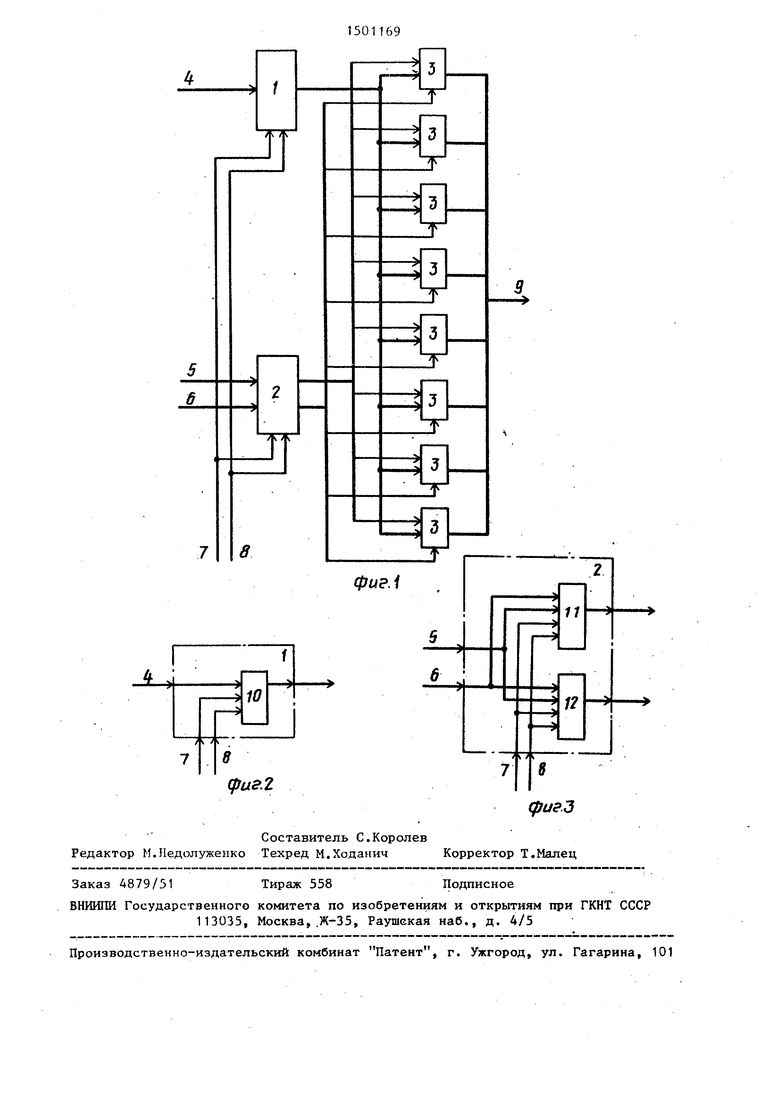

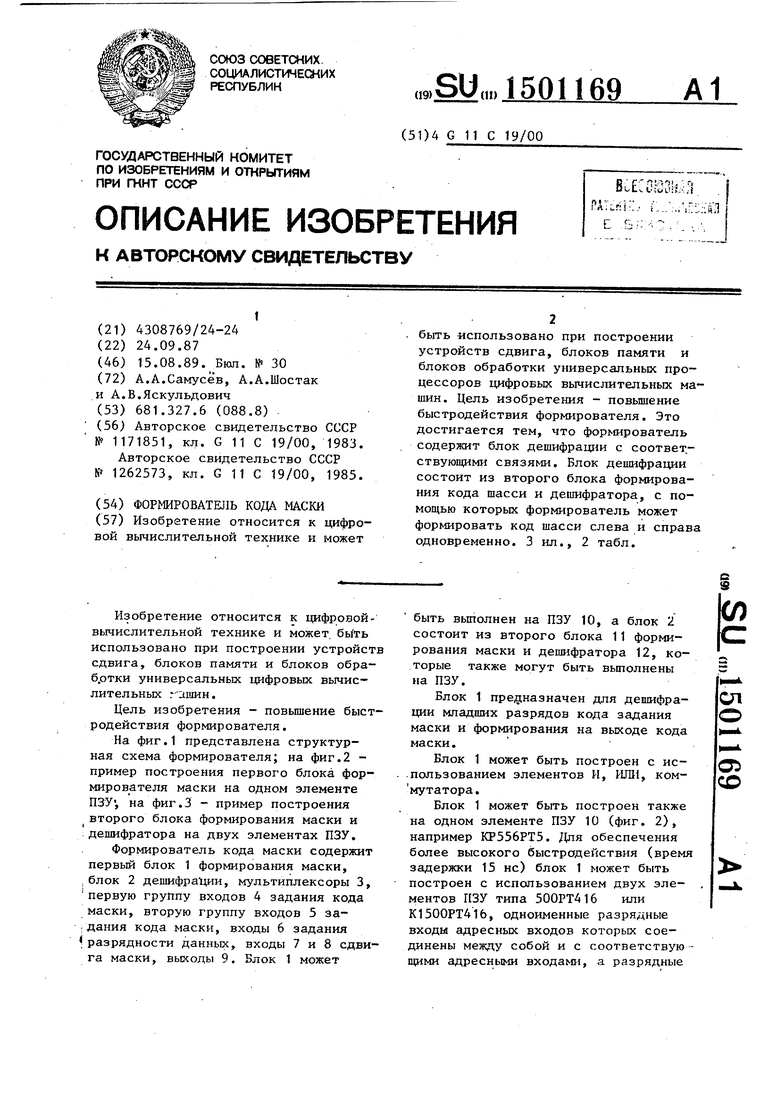

На фиг.1 представлена структурная схема формирователя; на фиг.2 - пример построения первого блока формирователя маски на одном элементе ПЗУ , на фиг.3 - пример построения второго блока формирования маски и : дешифратора на двух элементах ПЗУ.

Формирователь кода маски содержит первый блок 1 формирования маски, , блок 2 дешифрагу и, мультиплексоры 3, первую группу входов 4 задания кода маски, вторую группу входов 5 за- ; Дания кода маски, входы 6 задания разрядности данных, входы 7 и 8 сдвига маски, выходы 9, Блок 1 может

быть вьшолнен на ПЗУ 10, а блок 2 состоит из второго блока 11 формирования маски и дешифратора 12, которые также могут быть вьшолнены на ПЗУ.

Блок 1 предназначен для дешифрации младших разрядов кода задания маски и формирования на выходе кода маски.

Блок 1 может быть построен с ис- .пользованием элементов И, ИЛИ, ком- мутатора.

Блок 1 может быть построен также на одном элементе ПЗУ 10 (фиг. 2), например КР556РТ5. Для обеспечения более высокого быстродействия (время задержки 15 не) блок 1 может быть построен с использованием двух элементов ПЗУ типа 500РТ416 или К1500РТ416, одноименные разрядные входы адресных входов которых соединены между собой и с соответствующими адресными входами, а разрядные

(Л С

сд

05 СО

выходы элементов ПЗУ соединены с соответствующими разрядными выходами

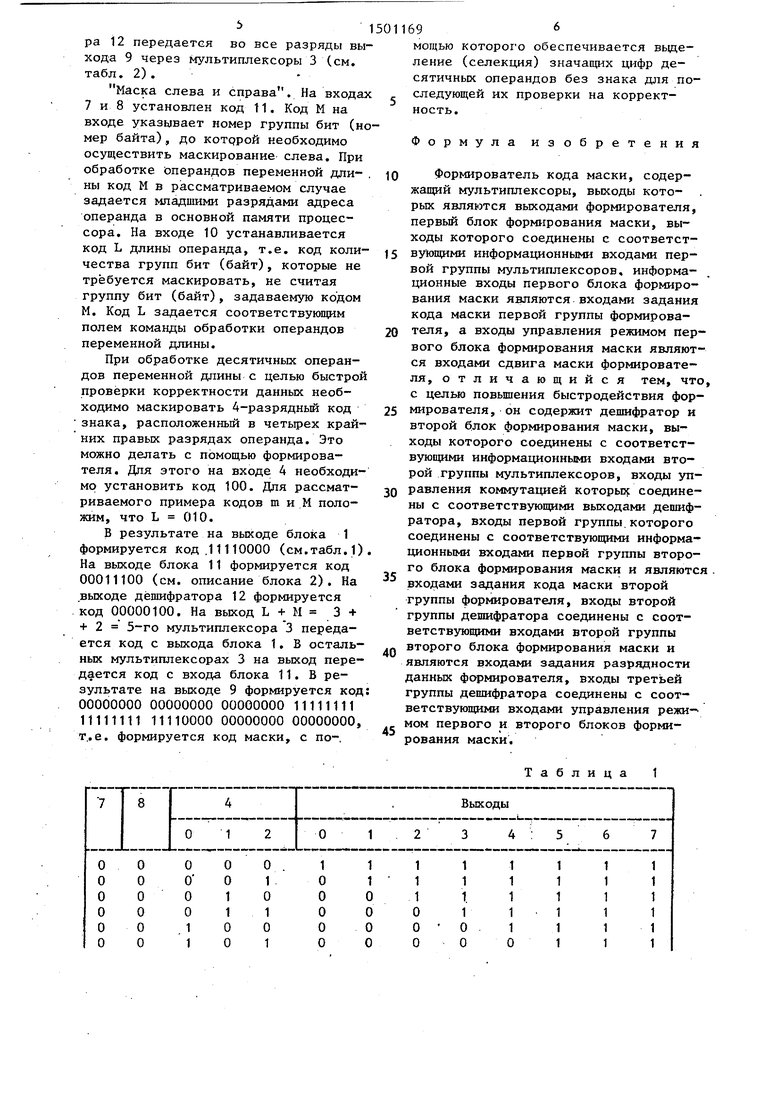

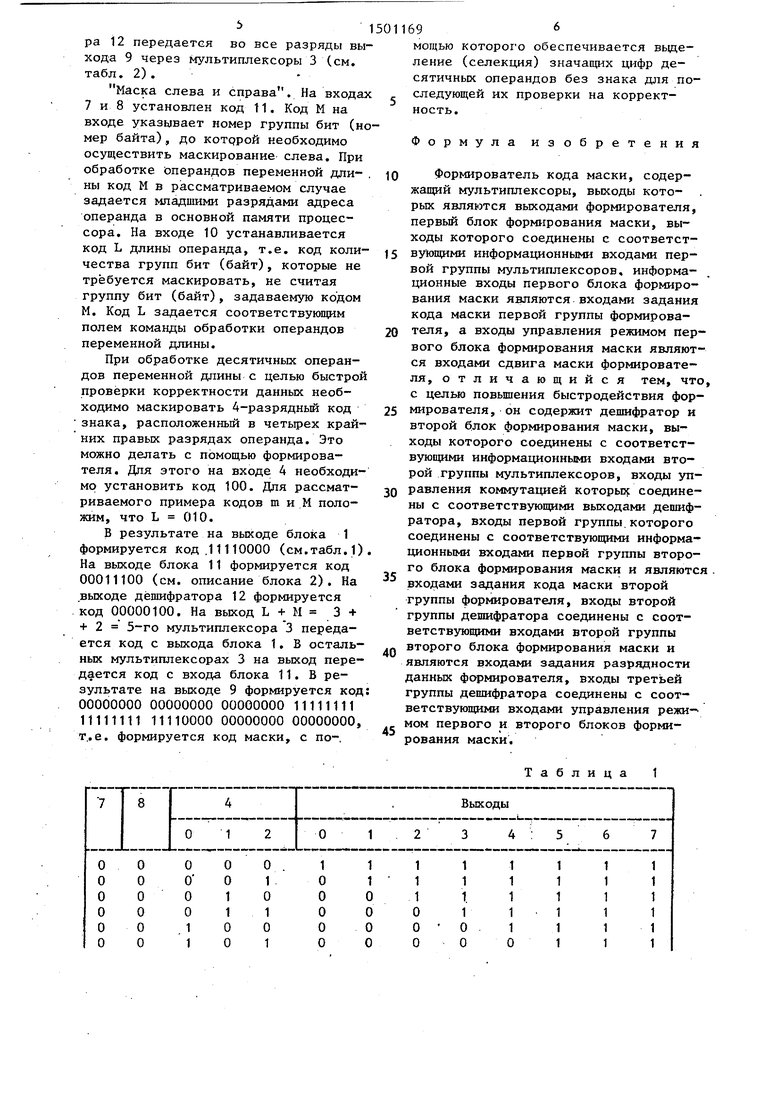

Блок 1 функционирует в соответствии с табл. 1.

Обозначение X в табл. 1 означает произвольное значение кода на соот- ветствующем разрядном входе. Табл.1 является также таблицей кодировки дл элемента ПЗУ 10.

Блок 2 предназначен для дешифрации старших разрядов кода задания маски (на входе 5), формирования на выходе блока 11 кода побайтной маски (или маски для групп бит) и форми- рования управляющих сигналов.на выходе дешифратора 12 с учетом управляющих сигналов на входах 7, 8 и кода длины операнда на входе 6,

Блок 2 может быть построен с ис- пользованием элементов И, ИЛИ, коммутаторов, дешифратора, сумматора или на элементах ПЗУ (фиг.З), так же как и блок 1 с использованием тех же интегральных схем.

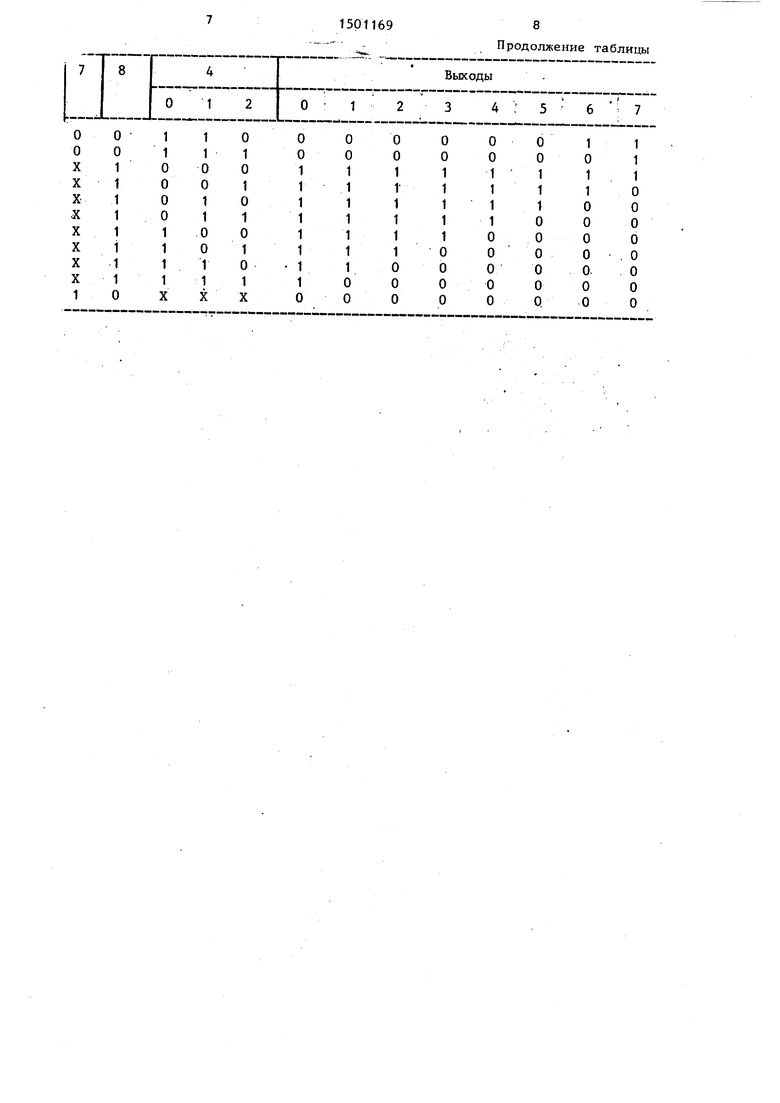

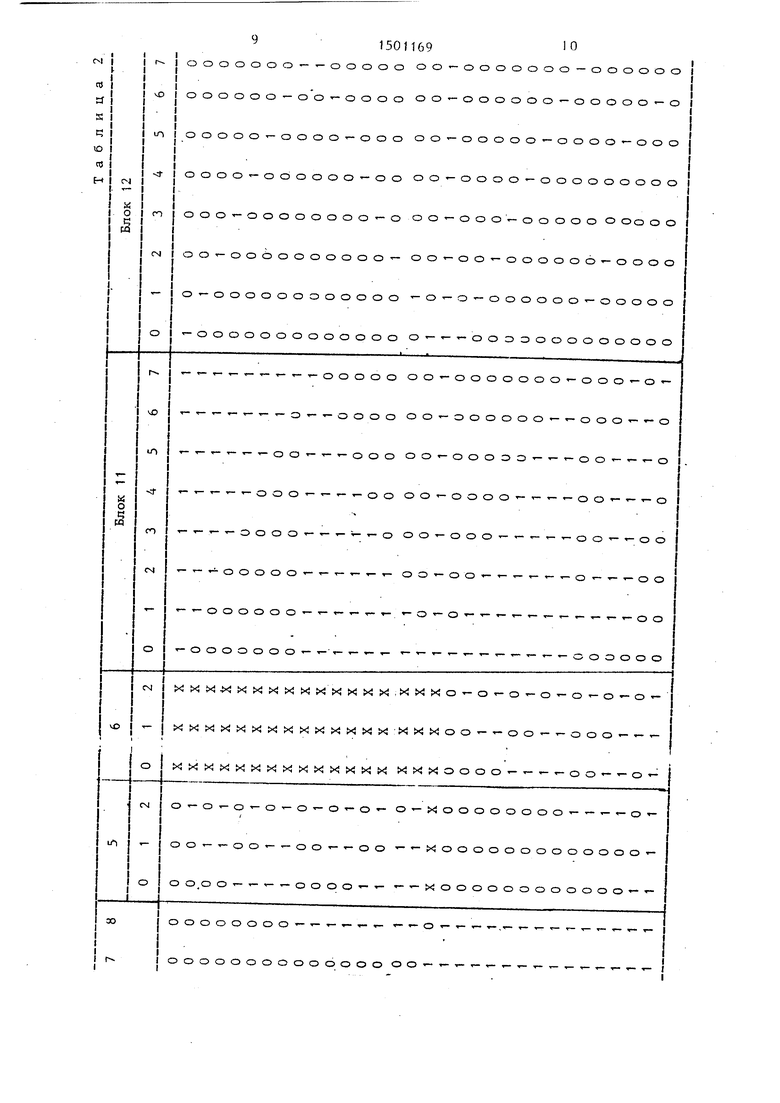

При этом блоки 11 и 12 функ1Ц1о- нируют в соответствии с табл. 2,где oбoзнiaчeниe X произвольное значение кода.

Мультиплексор 3 представляет со- бой стандартный узел,аналогичньй по структуре, например, микросхеме типа 1533КП16 или 500ТМ173 (без элементов памяти) .

Формирователь функционирует еле- дующим образом,

В исходном состоянии на входах 4, 5 устанавливается код задания маски. При этом на входах 4 устанавливаются младшие, а на входах 5 - старшие разряды кода задания маски. На входе 10 устанавливается код длины операнда (или код количества груп бит операнда, которые необходимо выделить (не маскировать)). На входах 7 и 8 устанавливается код функции.

В устройстве предусмотрены следующие функции;

- маска слева (при коде 00 на входах 7,8);

- масЛа справа (при коде 01 на входах 7, 8),

- единичный код (при нулевом коде на входах 7, 8, 4, 5)J

- нулевой код (при коде 10 на входах 7, 8);

- маска слева и справа (при коде 11 на входах 7, 8).

Для этого рассмотрим конкретный .пример установки на входе 4 кода m 100, на входе 5 - кода М 011, на входе 6 - кода L 010, К 64, К 8 (фиг.1).

Маска слева. На входах 7 и 8 установлен код 00. На выходе блока 1 формируется код 00001111 (табл. 1). На выходе блока 11 формируется код 00011111 (табл.2). На выходе дешифратора 12 формируется код 00010000. Под управлением сигналов на выходе дешифратора 12 все мультиплексоры 3, кроме мультиплексора 3 с номером М 35передают на выход код с выходов блока 11. На выходе М-го мультиплексора 3 передается код с выхода блока 1. В результате на выходе 9 формируется код:

00000000 00000000 00000000 00001111 11111111 11111111 11111111, . т.е.как и задано слева,, сформировано М К + га 3 8 + 4 28 логических нулей.

Маска справа. На входах 7 и 8 установлен код 01. На выходе блока 1 формируется код 11110000 (фиг. 1). На выходе блока 11 формируется код 11111000 (см. табл.2). На выходе дешифратора 12 формируется код 00001000 Под управлением сигналов на выходе дешифратора 12 все мультиплексоры 3, кроме мультиплексора 3- с номером 64 8

N .. --М1

-3-1 8 - 3 - 1

4, передают на выход код с выходов

N блока 11, На выход (- - М - 1)-го

Jx

мультиплексора 3 передается код с выхода блока 1, В результате на выходе 9 формируется код: 11111111 11111111 11111111 11111111 11110000 00000000 00000000 00000000, jT.e,, справа сформировано 28-логических нулей,

Единичный код. На входах 7, 8 и 5 устанавливается нулевой код. На выходах блоков 1 и 11 формируется единичньй код (табл, 1 и 2). В результате на все разряды выхода 9 через мультиплексор 3 передаются логические единицы, т.е. формируется единичный код,

Нулевой код. На входах 7 и 8 устанавливается код 10. На выходе блока 1 формируется нулевой код (см, табл, 1), который под управлением единичного кода на выходе дешифратоь 1

pa 12 передается во все разряды выхода 9 через мультиплексоры 3 (см, табл. 2).

Маска слева и справа. На входах 7 и 8 установлен код t1. Код М на входе указывает номер группы бит (номер байта), до котррой необходимо осуществить маскирование слева. При обработке операндов переменной дли- . ны код М в рассматриваемом случае задается младшими разрядами адреса опер1анда в основной памяти процессора. На входе 10 устанавливается код L длины операнда, т.е. код количества групп бит (байт), которые не требуется маскировать, не считая группу бит (байт), задаваемую кодом М. Код L задается соответствующим полем команды обработки операндов переменной длины.

При обработке десятичных операндов переменной длины с целью быстрой проверки корректности данных необходимо маскировать 4-разрядный код знака, расположенный в четырех крайних правых разрядах операнда. Это можно делать с помощью формирователя. Для этого на входе 4 необходимо установить код 100. Для рассматриваемого примера кодов m и М положим, что L 010.

В результате на выходе блока 1 формируется Код.11110000 (см.табл.1). На выходе блока 11 формируется код 00011100 (см. описание блока 2). На выходе дешифратора 12 формируется код 00000100. На выход L + М 3 + + 2 5-го мультиплексора 3 передается код с выхода блока 1. В остальных мультиплексорах 3 на выход передается код с входа блока 11. В результате на выходе 9 формируется код: 00000000 00000000 00000000 11111111 11111111 11110000 00000000 00000000, т..е. формируется код маски, с по-,

10

15

20

25

30

35

40

45

69

мощью которого обеспечивается вьще- ление (селекция) значащих цифр десятичных операндов без знака для последующей их проверки на корректность.

Формула изобретения

Формирователь кода маски, содержащий мультиплексоры, выходы которых являются выходами формирователя, первый блок формирования маски, выходы которого соединены с соответствующими информационными входами первой группы мультиплексоров, информационные входы первого блока формирования маски являются входами задания кода маски первой группы формирователя, а входы управления режимом первого блока формирования маски являются входами сдвига маски формирователя, отличающийся тем, что, с целью повьшения быстродействия формирователя, он содержит дешифратор и второй блок формирования маски, выходы которого соединены с соответст- вуюЕцими информационными входами второй группы мультиплексоров, входы управления коммутацией которых соединены с соответствующими выходами дешифратора, входы первой группы.которого соединены с соответствующими информационными входами первой группы второго блока формирования маски и являются входами задания кода маски второй группы формирователя, входы второй группы дешифратора соединены с соответствующими входами второй группы второго блока формирования маски и являются входами задания разрядности данных формирователя, входы третьей группы дешифратора соединены с соответствующими входами управления режимом первого и второго блоков формирования маски.

Таблица 1

01 i

со

cr s ч ю

пЗ И

rj

1501169 О

г I ООООООО - ООООО ОО -ООООООО- ОООООО

vO

ОООООО -ОО- ОООО ОО -ОООООО -ООООО -О

ООООО -ОООО -ООО ОО -ООООО-ОООО -ООО

OOOO -OdOOOO -OO ОО -ОООО -ООООООООО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для проверки монтажа | 1987 |

|

SU1509937A1 |

| Сумматор по модулю семь | 1989 |

|

SU1608645A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ПЕРЕПОЛНЕНИЯ | 1992 |

|

RU2020556C1 |

| Сумматор по модулю пятнадцать | 1989 |

|

SU1603375A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств сдвига, блоков памяти и блоков обработки универсальных процессоров цифровых вычислительных машин. Цель изобретения - повышение быстродействия формирователя. Это достигается тем, что формирователь содержит блок дешифрации с соответствующими связями. Блок дешифрации состоит из второго блока формирования кода шасси и дешифратора, с помощью которых формирователь может формировать код шасси слева и справа одновременно. 3 ил., 1 табл.

&

ООО ОООООООО -ООО -ООО--ООООО ООООО I

CN ООг-ОООООООООО- ОО -ОО ОООООО -ОООО I

О -ОООООООООООО -О-г-О -ОООООО -ООООО

--ООООООООООООО О - -ОООЭООООООООО

ООООО ОО -ООООООО -ООО -О чО

ОООО ОО -ОООООО - -ООО - -О

л

ОО -ООО ОО -ООООО -ОО - - О

W о

ч ю

го

- - -ОО ОООО - -«-«- - о

- - -ОООО

о о о - о о о

о о - о о

tN

т- г- ООООО

f-T-OOOOOO

о I т-ооооооо

I

CN) I XXX-XXXxJXlxitxJXXXX.XXXO O -O O- -O -O -O

чо I -гXXXXXXXXXXXXiXXXXXOO - ОО - -ооо - О ХХХХХХХХХХХХХХ ХХХОООО - - -г-оО - -О О -О -О О -О -О -О - О -ХОООООООО - - - -О 1Л

ОО - -ОО - ОО - -ОО - -ХООООООООООООО . о I о о,о О - - - ООрО - - - - ХОООООООООООО - «аз

оооооооо

I ОООООООООООООО ОО

о о о - о о о

о о - о о

о о о о

о о

о о

о о

ООООО

qjue:5

Составитель С.Королев Редактор М.Яедолуженко Техред М.Ходанич Корректор Т.Малец

Заказ 4879/51

Тираж 558

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва,.Ж-35, Раушекая наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Авторское свидетельство СССР № 1171851, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для формирования кода маски | 1984 |

|

SU1262573A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1987-09-24—Подача