а

Сд5

со со со

Изобретение относится к вычислительной технике и может быть использовано для построения устроств сдвига двоичных кодов в виде больших интегральных схем (БИС).

Целью изобретения является сокращение аппаратурных затрат.

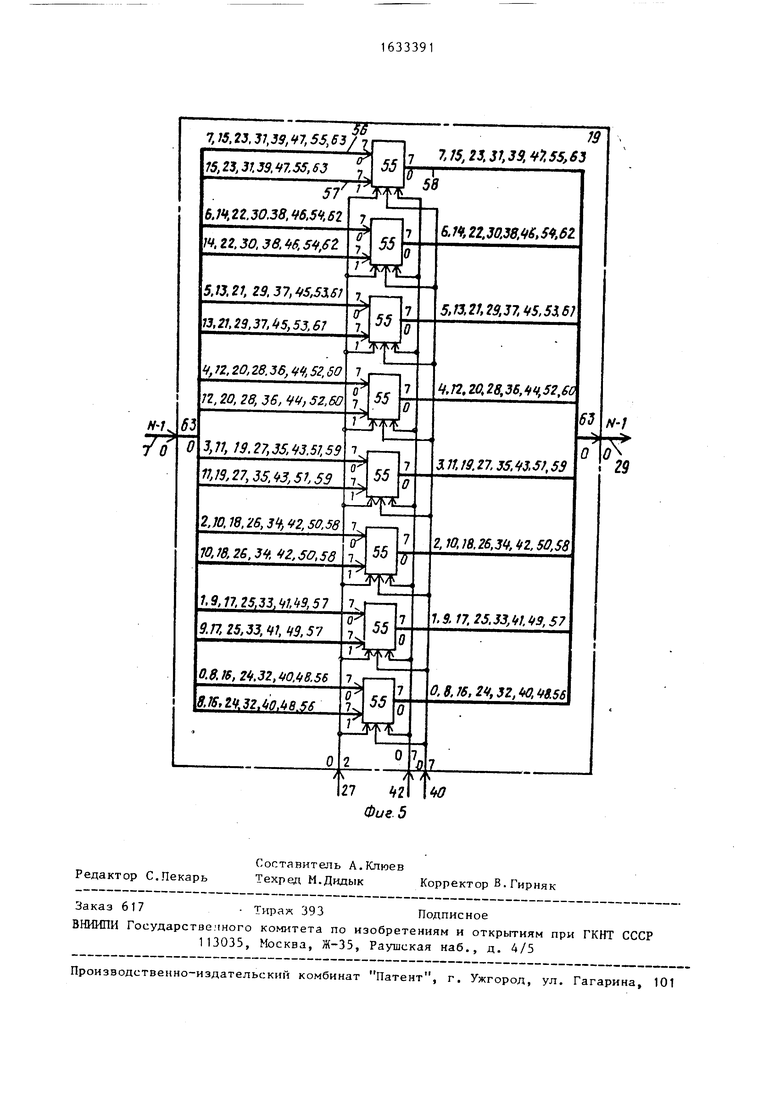

На фиг.1 представлена схема устройства для сдвига операндов; на фиг.2 - структурная схема блока одностороннего сдвига; на Аиг.З - структурная схема формирователя кода маски; на фиг.4 - функциональная охема преобразователя двоичного кода в единичный код; на фиг.5 - структурная схема узла группового сдвига.

Устройство (фиг.1) содержит блок 1 одностороннего сдвига, элемент И 2, формирователь 3 кода маски, преобра- зователь 4 прямого кода в дополнительный, блок 5 элементов И, знаковый вход 6, информационный вход 7, вход 8 задания типа сдвига, вход 9 разряда задания арифметического сдвига входа 8 задания типа сдвига, вход 10 задания типа сдвиг-а блока 1 одностороннего сдвига, вход 11 разряда задания направления сдвига входа 8 задания типа сдвига, знаковый вход 12 блока 1 одностороннего сдвига, первый и второй выходы 13 и 14 формирователя 3 кода маски, второй вход 15 блокирования блока 1 одностороннего сдвига, вход 16 задания величины сдвига, вход 17 задания величины сдвига блока 1 одностороннего сдвига, выход 18.

Блок 1 одностороннего сдвига (фиг.2) содержит узел 19 группового сдвига, узел 20 разрядного сдвига, первую группу элементов И 21, первый элемент НЕ 22, вторую группу элементов И 23, группу элементов ИЛИ 24, элемент ИЛИ 25, второй элемент НЕ 26, входы 27 и 28 -задания величины сдвига узлов 19 и 20 соответственно, выход 29 узла 19, выходы 30 К старших разрядов выхода 29 узла 19, выходы 31 (N-K) младших разрядов выхода 29 узла 19, выходы 32 (К-1) старших разря- дов выхода 29 узла 19, выходы 33 элементов И 23 группы, выходы 34 элементов ИЛИ 24 группы, входы 35 старших разрядов первого входа блокировки блока 1 односторонних сдвигов, выход 36 элемента НЕ 22, выходы 37 элементов И 21 группы, выход 38 элемента ИЛИ 25, вход 39 разряда задания циклического сдвига входа 10 блока 1 од

o

5

0 5О

45 5Q

55

посторонних сдвигов, первый вход 40 блокировки узла 19, вход 41 старшего разряда входа 40 блокировки узла 19, второй вход 42 блокировки узла 19, вход 43 старшего разряда входа 42 блокировки узла 19.

Формирователь 3 кода .маски (фиг.З) содержит преобразователь 44 двоичного кода в единичный код, коммутатор 45.

Преобразователь 44 двоичного кода в единичный код (фиг.4) содержит первый элемент ИЛИ 46, первую группу элементов И 47, вторую группу элементов И 48, второй элемент ИЛИ 49, группу элементов ИЛИ 50, третий элемент ИЛИ 51, первый и второй элементы И 52 и 53, выход 54 преобразователя 44 двоичного кода в единичный код.

Узел 19 группового сдвига (фиг.5) содержит группу модулей 55 сдчига, первый и второй инЛормационные входы 56 и 57 и выход 58 модуля 55 сдвига.

Цифры и буквы около жгутов управляющих и информационньгх входов узлов на фиг.1-5 обозначают номера разрядов.

Блок 1 сдвига предназначен для осуществления сдвига в одну сторону (вправо) кода, установленного на входе 7, соответствующего маскирования (обнуления) разрядов слева или справа и распространения кода знака, установленного на входе 12, в освобождаемых разрядах слева в соответствии с заданными управляющими кодами на входах 15, 17, 10 и выходе 13.

Узел 19 предназначен для осуществления циклического сдвига в одну сторону (вправо) кода, установленного на входе 7, на величину, равную М К, где М - значение кода на входе 27, маскирования соответствующего ко-, личества групп по К разрядов в группе справа или слева на выходе 29 под управлением и в соответствии с кодом маски, установленным на входе 40, и для формирования кода знака на соответствующем количестве групп слева по К разрядов в группе под управлением и в соответствии с кодом, установленным на входе 42. При этом крайняя правая группа из К разрядов выхода 29 никогда не маскируетсяtна ее разрядах не устанавливается код знака.

Узел 19 (фиг.5) содержит -модули 55 сдвига, которые по структуре и функционированию (реализованы на нуль516

типлексорах) аналогичны узлу односторонних сдвигов в известном устройстве с тем отличием, что содержат дополнительно первый и второй К-раз- рядные входы блокировки, соединенные соответствующими входами мультиплексоров, т.е. первый и второй входы блокировки 1-го (при отсчете слева направо) мультиплексора в модуле 55 соединены с i-ми разрядами первого 40 и второго 42 входов блокировки соответственно (для приведенного при

N мера на фиг.5 и 2 i (--- - 1) 7).

К

При установке на первом входе блокировки логической единицы на выходе мультиплексора устанавливается логический нуль, если на втором входе блокировки установлен логический нуль, или логическая единица, если на втором входе блокировки установлена логическая единица. При установке на втором входе блокировки логической единицы на выходе мультиплексора устанавливается логическая единица независимо от кодов на входах 27 и 40. При установке на входах блокировки логического нуля на выход мультиплексора передается код с М-го информационного входа, где N - значение кода на входе 27.

В узле 19 i-й разряд первого и второго входа блокировки каждого модуля 55 соединяется с i-м разрядом соответственно первого и второго входов 40 и 42 блокировки узла 19.

Узел 19 (фиг.5) функционирует следующим образом. При установке на входах 42 и 40 нулевого кода на выходе 29 формируется циклически сдпину- тый вправо код относительно кода,установленного на входе 7, на величину, равную М-К, где М - значение кода,установленного на входе 27, а С 8. Если при этом в i-м разряде входа 42 установить логическую единицу, то в в i-й группе разрядов (при отсчете слева направо по К разрядов в группе) выхода 29 установится нулевой код. Если при этом в i-м разряде 42 установить логическую единицу, то в этой же i-й группе разрядов выхода 29 установится единичный код.

Узел 20 предназначен для формирования на выходе 18 сдчинутого вправо кода относительно кода на первом информационном входе (выходах 31 и 37) на величину (0 Ј m (К-1), где

0

5

m - значение кода, установленного на входе 28, с вдвиганием в освобождаемые разряды соответствующей части кода, установленного на входах 34. Структура узла 20 аналогична структуре второго узла сдвига в известном устройстве.

Преобразователь 4 идентичен по назначению структуре и функционированию преобразователю кода известного устройства.

Формирователь 3 предназначен для

,N

формирования --- - разрядного кода К

маски на выходе 13 и (--- - 1)-раяК

рядного кода маски на выходе 14 с учетом кода величины сдвига на вхо0 де 16 и кода типа сдвига на входе 10.

Преобразователь 44 Функционирует следующим образом. При установке на разрядах (0/2) входа 16 кода N, на разрядах (3/5) входа 16 нулевого ко5 да, а на входах 39 и 11 - логической единицы на разрядах (0/N-1) (О Јх Н 6- 7) выхода 54 устанавливается логическая единица, а на остальных разрядах - логический ноль. При этом

0 если на разрядах О/5) входа 16 будет установлен любом не нулевоЯ код, то логическая единица установится на разрядах (0/N) выхода 54. Если на входе 11 будет установлен логический ноль, то независимо от значения кода на разрядах ( входа 16 логическая единица установится на разрядах (0/N-1) выхода 54. Гели на входе 39 установлен логический ноль, то на всех разрядах выхода 54 установится логический ноль. Коп. с разрядов (0/6) выхода 54 передается на выход 14 формирователя 3. Код с выхода 54 транзитом через коммутатор 45 переда5 ется на выход 13 при установке на входе 11 логического нуля или на выход 13 передается транспонированный код с выхода 54 при установке на входе 1 1 логической единицы.Транспонирование эа0 ключается в данном случае в обратном расположении разрядов кода относительно разрядов выхода 13.

Устройство (фиг.1) Лункционирует следующим образом.

5

0

В исходном состоянии на входе 7 устанавливается сдвигаемый дпоичный код. На выходе 16 уст.знативлотся код величины сдвига. Нл «холе 8 устанавливастся код типа сдвига. Возможны слецукнчие типы сдвига с установкой на входах 9, 11 и 39 разрядов соответствующих кодов: логический сдвиг вправо (ЛП) при коде 001; логический сдвиг влево (Л.П) при коде 011; арифметический сдвиг вправо (АП) при коде 101; 1р1клический сдвиг вправо (1Щ) при коде 000; циклический сдвиг влево (1Щ) при коде 010.

На входе 6 устанавливается код знака при арифметическом сдвиге вправо. При этом параллельно на нулевом разряде входа 7 также устанавливается код знака в силу принятого способа кодирования арифметических операндов в универсальных цифровых вычислительных машинах.

На выходе 16 формируется сдвинутый код в соответствии с заданной величиной и типом сдвига.

Для определенности положим N 68 К 8, на входе 7 устанавливается код 11110000111100001111000011110000 11110000111100001111000000000000, на входе 16 устанавливается код 0101010 т.е. со значением, равным 26. Рассмотрим функционирование устройства при всех типах сдвига. Код знака на входе 6 равен логической единице.

При коде 001 (ЛП) на входе 8 на выходе элемента И 2 устанавливается нуль, запираюрртй блок 5 элементов И. В результате на входе 15 устанавливается нулевой код. На выходе 13 на разрядах (0/7) сформируется код 11100000. На вход 17 транзитом передается код 011010 с входа 16. При этом на разряды входа 27 (фиг. 2) передается код М 011 со значением, равным 3, а на разряды входа 28 - код in 010 со значением, равным 2. Так как на входе 42 узла 19 установлен нулевой код, то он не влияет на формирование сдвинутого кода на выходе 29. На разрядах (0/2) выхода 13 и входа 40 сформированы логические единицы, под действием которых в тре группах разрядов слева (т.е. в нулевой, первой и второй слева группах разрядов) выхода 29 (при количестве разрядов в группе, равном К 8) сформируется логический ноль, т.е. в разрядах (0/23) выхода 29 устано- ,вится логический ноль. В остальные разряды будет передана оставшаяся часть циклически сдвинутого кода, установленного на входе 7, так как на

5

0

5

0

5

0

5

0

разрядах (3/7) входа 40 установлен логический нуль, т.е. на выходе 29 сформируется код 0000 0000 0000 0000 0000 0000 1111 0000 1111 0000 1111 0000 1111 0000 1111 0000.

N

Нулевой код с (--- - 1) седьмого К

разряда выхода 13 устанавливается на входе элемента НЕ 22, на выходе 36 которого устанавливается логическая единица, отпирающая группу элементов И 21.

В результате код с выхода 29 устанавливается на разрядах первого информационного входа узла 20. Так как на входе 39 установлена логическая единица, на выходе элемента НЕ 26 устанавливается логический ноль, который с логическим нулем на другом входе элемента ИЛИ 25 обеспечивает формирование логического нуля на входе группы элементов И 23. В результате на выходах 33 формируется нулевой код. Так как на входе 12 также сформирован логический ноль, то на выходах 34 устанавливается нулевой код. В узле 20 осуществляется сдвиг вправо на m 2 бит (разряда) со сдвиганием в освобождаемые разряды на два крайних правых бита кода, установленного на выходах 34.

В результате на вькоде 18 формируется код 00 0000 0000 0000 0000 0000 0000 1111 0000 1111 0000 1111 0000 1111 0000 1111 00, т.е. осуществляется логический сдвиг вправо на величину 26 бит (разрядов).

При коде 011 (ЛЛ) на входе 8 на выходах 12 и 15 устанавливаются нулевые коды. На выходе 13 устанавливается код 0000 1111 (если бы т было равно нулю, то на выходе 13 сформировался бы код 00000111). На входе 17 формируется дополнительный код от кода, установленного на входе 16, т.е. код 00110. При этом на разрядах входа 27 (фиг.2) устанавливается код М 100 со значением, равным 4, а на разрядах входа 28 - код m 110 со значением, равным 6. Так как на входе 42 узла 19 сформирован нулевой код, то он не влияет на формирование кода на выходе 29. Так как на

55

-г -

седьмом разряде входа 40

установлен логический ноль, то крайняя правая группа из К 8 разрядов

выхода 29 не маскируется, а четвертая, пятая и шестая группы разрядов маскируются, так как в разрядах (4/6 выхода 13 установлены логические единицы. Логическая единица с седьмого разряда выхода 13 устанавливается на входе элемента НЕ 22.

В результате на выходах 37 устанавливается нулевой код.

Таким образом, на выходе 29 формируется код 1111 0000 1111 0000 1111 0000 0000 0000 0000 0000 0000 0000 0000 0000 1111 0000, а на выходах 31 и 37 установится код 1111 0000 1111 0000 1111 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000.

Так как на входе 11 установлена логическая единица, то код с выходов 32, равный 1110000, передается на выходы 34, поскольку на входе 12 установлен логический ноль.

В узле 20 осуществляется сдвиг вправо на m 6 бит (разрядов) с вдвиганием в освобождаемые разряды слева соответствующей части кода с выходов 34.

В результате на выходе 18 формируется код 11 0000 1111 0000 1111 0000 1111 0000 0000 0000 0000 0000 0000 0000 0000 0000 00, т.е. осуществляется логический сдвиг влево на величину 26 бит (разрядов).

При коде 101 (АП) на входе 8 уст- роство функционирует так же, как и при ЛП, с тем отличием, что на выход элемента И 2 будет передан код знака с входа 6. Если код знака является нулевым, то функционирование устройства ничем не отличается от функционирования при ШТ. В рассматриваемом примере код знака является единичным. В этом случае на вход 15 будет передан код с выхода 14, в котором в разрядах (0/2) сформированы логические единицы, под действием которых в трех группах разрядов (фиг.2) слева (т.е. в нулевой, первой и второй слева группах разрядов) выхода 29 (при количестве разрядов в группе, равном К 8) сформируется логическая единица, т.е. в разрядах (0/23) выхода 29 установится логическая единица, соответствующая коду знака.

На выходе 29 сформируется код 1111 1111 1111 1111 1111 1111 1111 0000 1111 0000 1111 0000 1111 0000

25

1111 0000, который установится на первом информационном входе узла 20.

Под действием логической единицы на входе 12 на выходах 34 сформируется единичный код.

В результате сдвига в узле 20 на выходе 18 сформируется код 11

11111111 11111111 11111111 11111111

10 11110000 11110000 11110000 11110000 1111 00, т.е. осуществляется арифметический сдвиг вправо на 26 разрядов.

При коде 000 (ЦП) на входе 8 уст15 ройство функционирует так же, как и при ЛП, с тем отличием, что на выходе 13 формируется нулевой код. В результате в узле 19 маскирования разрядов не происходит и на выходе формируется

20 код 1111 0000 1111 0000 00000000

11110000 11110000 11110000 1111 0000 11110000. Так как на входе 39 (фиг.2) установлен логический ноль, то на выходе 38 установится логическая единица и код 111 0000 с выходов 32 будет передан на выходы 34.

В результате сдвига в узле 20 на выходе 18 сформируется код 00 11110000 11110000 00000000 11110000 11110000

0 11110000 11110000 1111 00, т.е. осуществляется циклический сдвиг вправо на 26 разрядов.

При коде 010 (1Щ) на входе 8 уст- г ройство функционирует так же, клк и при ЛЛ, с тем отличием, что на выходе 13 формируется нулевой код. В результате в узле 19 группы разрядов кода на выходе 29 не маскируются, а на 0 выходе 36 устанавливается логическая единица, обеспечивающая передачу кода с выходов 30 на выходы 37. В результате код 11110000 11110000 11110000 00000000 11110000 1111000011110000 5 11110000, сформированный на выходах 31 и 37, сдвигается в узле 20 на шесть разрядов вправо с вдвиганием в освобождаемые разряды слена соответствующей части кода 11110000. На выходе 18 0 формируется код 11 0000 1111 0000

1 m оооо 1111оооо оооооооо 11110000

11110000 11110000 11, т.е. осуществляется циклический сдвиг влево на 26 разрядов.

Следует отметить, что за счет реализации формирователя кода маски в виде комбинационной схемы (в отличие от ПЗУ в прототипе) улучшается технологичность устройства.

Формула изобретения

1. Устройство для сдвига операндов, содержащее блок односторонних сдвигов, элемент И, формирователь кода маски,п преобразователь прямого кода в дополнительный код и блок элементов Н, причем информационный вход устройства соединен с информационным входом блока одностороннего сдвига, выход которого соединен с выходом устройства, знаковый вход которого соединен с первым входом элемента И, второй вход которого соединен с вхо- дом задания арифметического сдвига входа задания типа сдвига устройства, выход элемента И соединен со знаковым входом блока одностороннего сдвига, первый вход блокировки которого соединен с первым выходом формирователя кода маски, первый и второй входы разрядов управляющего входа которого соединены с входами разрядов задания направления сдвига и цикличе- ского сдвига входа задания типа сдвига устройства соответственно, входы разрядов задания направления сдвига и циклического сдвига входа задания типа сдвига устройства соединены с со- ответствующими входами разрядов входа типа сдвига блока одностороннего сдвига, вход задания величины сдвига которого соединен с выходом преобразователя прямого кода в дополни- тельный код, вход разрешения которого соединен с входом разряда задания направления сдвига входа задания типа сдвига устройства, вход задания величины сдвига которого соединен с ин- формационными входами преобразователя прямого кода в дополнительный код и формирователя кода маски, выход элемента И соединен с первым входом блока элементов И, о т л и ч а ю ч е - е с я тем, что, с целью сокращения аппаратурных затрат, второй выход формирователя кода маски соединен с вторым входом блока элементов И, выход которого соединен с вторым входом

блокировки блока одностороннего сдвига.

2. Устройство поп.1, отличающееся тем, что блок одностороннего сдвига содержит узел группового сдвига, узел разрядного сдвига и вторую группы элементов И, группу элементов ИЛИ, первый и второй

0 Q 5 0

5

элементы НЕ, элемент ИЛИ, причем информационный вход блока одностороннего сдвига соединен с информационным входом узла группового сдвига, выходы (N-K) (где N 2, К 2, 1 4, О i «с 1) младших разрядов выхода которого соединены с входами соответствующих разрядов первого информационного входа узла разрядного сдвига, входы К старших разрядов первого информационного входа которого соединены с выходами соответствующих элемен тов И первой группы, первые входы которых соединены соответственно с выходами К старших разрядов выхода узла группового сдвига, выходы (K-l)-ro старших разрядов выхода которого соединены с первыми входами соответству- ющих элементов И второй группы, выходы которых соединены г первыми входами соответствующих элементов ИЛИ группьц, выхоцы которых соединены с входами соответствующих разрядов второго информационного входа узла разрядного сдвига, выход которого является выходом блока одностороннего сдвига, входы младших и старших разрядов входа задания величины сдвига которого соединен i соответственно с входами разрядов задания величины сдвига узлл разрядного сдвига и узла группового сдвига, входы старших разрядов первого и второго входов блокировки которого соединены с входом логического нуля устройства, входы гшадглгх разрядов первого и второго входов блокировки узла группового сдвига соединены с входами соответствуклтих разрядов первого и второго входов блокировки блока одностороннего сдвига соответственно, вход старшего разряда первого входа блокировки которого соединен с входом первого элемента НЕ, выход которого соединен с вторыми входами элементов И первой группы, вторые входы элементов И второй группы соединены с выходом элемента ИЛИ, первый вход которого соединен с входом разряда задания направления сдвига входа задания типа сдвига блока одностороннего сдвига, второй вход эпе- мента ИЛИ соединен с выходом второго элемента НЕ, вход которого соединен с входом разряда задания циклического сдвига входа задания типа сдвига блока одностороннего сдвига, знаковый вход которого соединен с вторыми входами элементов ППИ группы.

3. Устройство по и.1, отличающееся тем, что формирователь кода маски содержит преобразователь двоичного кода в единичный код и коммутатор, причем информационный вход формирователя кода маски соединен с информационным входом преобразователя двоичного кода в единичный код, выходы разрядов которого соединены с входами соответствующих разрядов первого информационного коммутатора, выход которого является первым выходом формирователя кода маски, первый и второй входы разря- дов управляющего входа которого со

r

0

единены соответственно с входом задания режима и входом разрешения преобразователя двоичного кода в единичный код, выходы младших разрядов которого соединены соответственно с выходами разрядов второго выхода формирователя кода маски, выходы разрядов преобразователя двоичного кода в единичный код соединены перекрестно с входами разрядов второго информационного входа коммутатора, управляющий вход которого соединен с входом задания режима преобразователя двоичного кода в единичный код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ПЕРЕПОЛНЕНИЯ | 1992 |

|

RU2020556C1 |

| Формирователь кода маски | 1987 |

|

SU1501169A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

Изобретение относится к вычислительном технике и гшлет JUT, использовано для построения vcтройств сдвига двоичных кодов в гиде больших интегральных схем. Цель изобретрцич - сокращение аппаратурных аграт. Лечь достигается благодаря то|чу, что устройство для сдвига операн.чон, содержащее блок 1 одностороннего сдвига, преобразователь 4 прямого кода в дополнительный код, (Ьориироваталь 3 кода маски, эпемснг I 2, блок 5 элементов И, имеет opi .шитащпо связей. 2 т.п. Л-лы, 5 iui .

15

| Устройство для сдвига операндов | 1985 |

|

SU1298739A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР № 1568041, KJi | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-07—Публикация

1988-07-11—Подача