Јь

00

Јь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для сдвига операндов | 1986 |

|

SU1330626A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Формирователь кода маски | 1987 |

|

SU1501169A1 |

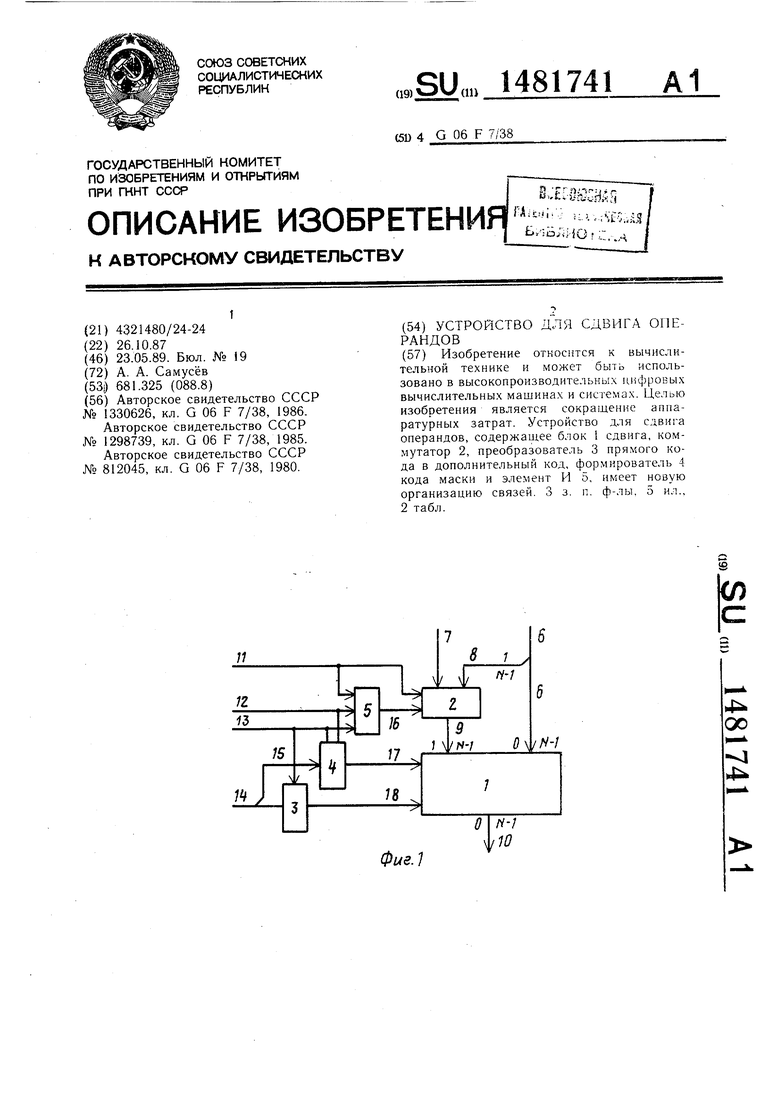

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных цифровых вычислительных машинах и системах. Целью изобретения является сокращение аппаратурных затрат. Устройство для сдвига операндов, содержащее блок 1 сдвига, коммутатор 2, преобразователь 3 прямого кода в дополнительный код, формирователь 4 кода маски и элемент И 5, имеет новую организацию связей. 3 з.п.ф-лы, 5 ил., 2 табл.

Фие.1

Изобретение относится к области вычислительной техники и может быть использовано в высокопроизводительных цифровых вычислительных машинах и системах.

Целью изобретения является сокращение аппаратурных затрат.

На фиг. 1 изображена структурная схема устройства для сдвига операндов; на фиг. 2-структурная схема блока сдвига, первый вариант; на фиг. 3 - то же, второй вариант; на фиг. 4 - структурная схема первого узла одностороннего сдвига; на фиг. 5 - структурная схема второго узла одностороннего сдвига.

Устройство (фиг. 1) содержит блок 1 сдвига, коммутатор 2, преобразователь 3 прямого кода в дополнительный код, формирователь 4 кода маски, элемент И 5, информационный вход 6 устройства, знаковый вход 7 устройства, первый информационный вход 8 коммутатора 2, выход 9 коммутатора 2, выход 10 устройства, вход 11 задания арифметического сдвига устройства, вход 12 задания циклического сдвига устройства, вход 13 задания направления сдвига устройства, вход 14 задания величины сдвига устройства, информационный вход 15 формирователя 4 кода маски, выход 16 элемента И 5, вход 17 блокировки блока 1 сдвига, вход 18 задания величины сдвига блока 1 сдвига.

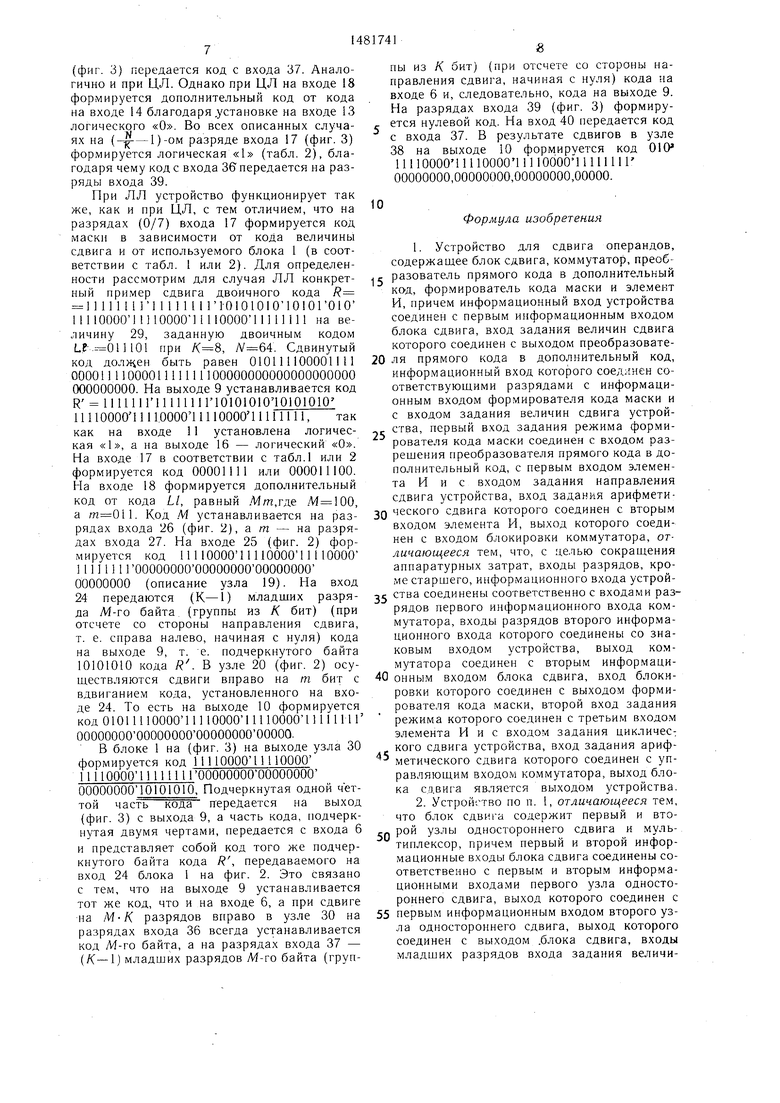

Блок 1 сдвига по первому варианту (фиг. 2) содержит первый узел 19 одностороннего сдвига, второй узел 20 одностороннего сдвига, мультиплексор 21, информационный вход 22 мультиплексора 21, второй информационный вход 23 узла 19 одностороннего сдвига, второй информационный вход 24 узла 20 одностороннего сдвига, первый информационный вход 25 узла 20 одностороннего сдвига, входы 26 и 27 соответственно старших и младших разрядов входа 8 задания величины сдвига блока 1.

Блок 1 сдвига по второму варианту (фиг. 3) содержит группу элементов И 28, мультиплексор 29, первый узел 30 одностороннего сдвига, вход 31 блокировки узла 30 одностороннего сдвига, вход 32 разряда входа 17 блока 1 сдвига, входы 33 разрядов, кроме двух старших, входа 17 блока 1 сдвига, вход 34 старшего разряда входа 31 блокировки узла 30 односторонних сдвигов, вход 35 (N/K-1)-го разряда входа 17 блока 1 сдвига, первый вход 36 группы элементов И 28, первый информационный вход 37 мультиплексора 29, второй узел 38 односторонних сдвигов, первый информационный вход 39 узла 38 односторонних сдвигов, второй информационный вход 40 узла 38 односторонних сдвигов.

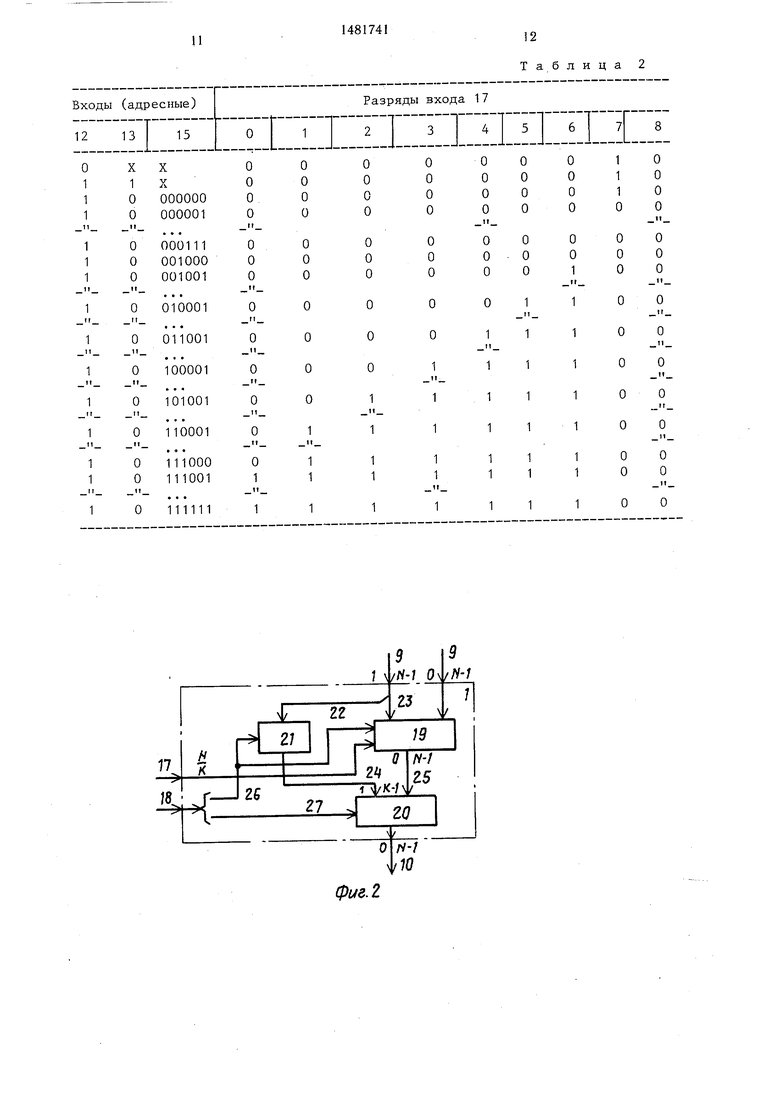

Первый узел 19(30) односторонних сдвигов (фиг. 4) содержит модули 4 сдвига, первый и второй информационные входы 42

0

и 43 и выход 44 модуля 41 сдвига соответственно, второй узел 20(38) односторонних сдвигов (фиг. 5) содержит модули 45 сдвига, первый и второй информационные 5 входы 46 и 47 и выход 48 модуля 45 сдвига соответственно.

Цифры и буквы около жгутов разрядов информационных входов на фиг. 1-5 и около управляющих разрядных входов означают номера разрядов или количество разрядов.

Модуль 41(45) сдвига (фиг. 4 и 5) по структуре аналогичен узлу односторонних сдвигов устройства для сдвига операндов. На выходе 44 модуля 41 формируется

5 сдвинутый код относительно кода установленного на входе 42 на величину, определяемую кодом на входе 26. В освобождаемые разряды (в рассматриваемом примере - слева) вдвигается соответствующая (правая) часть кода, установленного на вхо0 де 43. Каждый модуль 41 определенным образом подключается разрядами входов 42 и 43 и выхода 44 к разрядам входоь соответственно 6, 23 и 25. То есть(5 + t-K)-ft разряд входа 6 соединяется с t-ьш разря5 Дом входа 42 5-го модуля 41, где 1 ...,(-Ј---1), а , 1,..., (/(-1). Аналогично осуществляется связь разрядов входа 25 с разрядами выходов 44 модулей 41. Таким же образом осуществляется связь разрядов входа 23 с разрядами входа 43 модулей 41

0 с тем отличием, что (Л-1). На выходе узла 19(30) формируется сдвинутый код относительно кода, установленного на входе 6 на величину, равную М-К, где М - значение кода на входе 26, а К равно 8. В освобождаемые разряды (слева)

5 в узле 19(30) вдвигается соответствующая часть кода с входа 23, причем имеется возможность маскировать группы разрядов на выходе благодаря связи 17(31). При единичном коде на входе 17(31) на выходе фор мируется нулевой код независимо от значений кодов на входах 6 и 23. При нулевом коде на входе 17(31) ни один разряд выхода не маскируется, т, е. не обнуляется. В остальных случаях установленный на 5-ом разряде входа 17(31) логический «0(«1),

5 передается на вход блокировки 5-го мультиплексора всех модулей 41, на выходе которою и, следовательно, на 5-ом (при отсчете слева направо) разряде выхода всех модулей 41 устанавливается переданная информация (логический «О). Но так как 5-ые

0 разряды всех модулей 41 образуют группу соседних разрядов (байт) с номером 5, то з 5-ую группу разрядов выхода передается информация (логический «О), где , 1..., (-5-1). Описанные структуры и функционирование узла 19 на фиг. 4 соответст5 вуют конкретному случаю, когда , т. е., например, , .

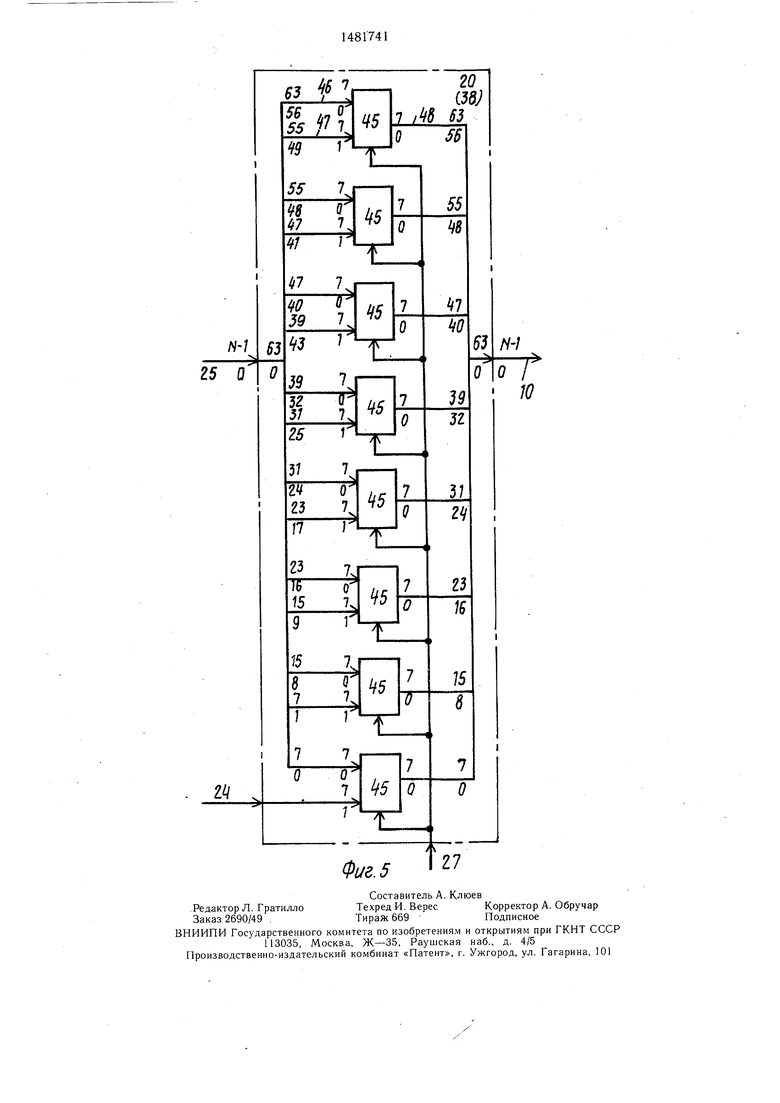

Узел 20(38) (фиг. 5) построен на модулях 45 сдвига, аналогичных модулям 41

сдвига, разряды входов и выхода которых соединены с разрядами входов 24 и 25 и выхода 10 (фиг. 5). Узел 20(38) сдвига предназначен для формирования на выходе 10 сдвинутого вправо кода относительно кода на входе 25 на величину М( ;(/(- 1) где М - значение кода, установленного на входе 27, с вдвиганием в освобождаемые разряды соответствующей части кода, установленного на входе 24. Мультиплектеля 4 осуществляются в соответствии о табл. 2 (при , ).

По таблице 2 видно, что для формирования требуемых сигналов на ()-ом разряде входа 17 формирователя достаточно в формирователь 4 для блока I (фиг. 3) ввести элемент И, первый и второй входы которого соединены с входами 12 и 13, а выход элемента И соединен с разрядом входа 17. Остальные разряды входа 17

сор 21 является N/K-входовым. Мульти- 10 необходимо соединить с выходом ПЗУ, в

плексор 29 является двухвходовым. При логическом и арифметическом сдвиге вправо на входах 32 и 35 (фиг. 3) формируется логическая «1, на входах 33 - логический «О. В результате на вход 40 передает- ся код с выхода 9, а на разряды входа 39 - код с входа 36. То есть на информационных и управляющих входах узлов 30, 38 формируются те же коды, что и на входах узлов 19 и 20 (фиг. 2) при тех же типах сдвигов.

При циклических сдвигах, в отличие от сдвигов вправо (логического и арифметического), на входе 32 формируется логический «О. В результате на вход 40 передается код с входа 37, т. е. код последней не выдвинутой группы бит в узле 30 для вдвигания в узле 38 той его части, которая выдвигается в узле 38, что необходимо для правильного выполнения циклических сдвигов.

При логическом сдвиге влево на входах 33 формируется код маски, при котором предотвращается передача информации с входа 6 на выход узла 30, кроме группы бит, передаваемой на вход 36 (благодаря логическому «О на входе 34). Предотвращение передачи этой группы на первый информационный вход узла 38 осуществляется с помощью группы элементов И 28 благодаря установке на входе 35 логического «О. На входе 32 устанавливается логический «О, благодаря чему код с вхокотором ()-ый разряд кодируется

инверсным значением по сравнению с ПЗУ в формирователе 4 для блока на фиг. 2 (табл. 1).

Устройство (фиг. 1) функционирует следующим образом.

В исходном состоянии на входе 6 (фиг. 1) устанавливается сдвигаемый код. На входе 7 устанавливается код знака. На входе 14 устанавливается код величины сдвига. На 20 входах -11 -13 задается ,од гипа сдвига. Возможны следующие типы сдвига при установке соответствующих кодов на входах 11-13: логический сдвиг вправо (ЛП) при коде 111; арифметический сдвиг вправо (АП) при коде 011; циклический сдвиг вправо (ЦП) при коде 101; циклически) сДвиг влево (ЦЛ) при коде 100; логический сдвиг влево (ЛЛ) при коде 110.

На выходе 10 формируется соответствующим образом сдвинуты код од При ЛП на выходе 16 формируемся логическая ., блокирующая коммутатор 2. В результате на выходе 9 формируется нулевой код. На входе 17 формируется код маски в соответствии с табл. 1 или 2, т. е. нулевой код маски (маска отсутствует). На вход 18 передается код с входа 14. В результате в блоке 1 осуществляется сдвиг вправо двоичного кода, установленного на входе 6 с заполнением освобождаемых разрядов логическим «(Ь, так как логический «О устанавливается и на

25

35

да 37 передается на вход 40. Этот код являет- 40 входе 23, и на входах 24 и 40 (описание блося тем кодом, который необходимо вдвигать в узле 38 для получения правильно сдвинутого влево двоичного кода на выходе 10.

Формирователь 4 кода маски предназков 1 на фиг. 2 и 3). При АП устройство функционирует так же, как и при ЛП, с тем отличием, что на входе 11 устанавливается логический «О. В результате на выходе 16 формируется логический «О и на выход 9

- - vj-А К.

начен для формирования - --разрядного ко- 4Э передается с входа 7 код знака для вдвида маски с учетом кода величины сдвига, направления сдвига и типа сдвига. Формирователь 4 может быть построен на логических элементах или на элементах постоянных запоминающих устройств (ПЗУ), например, типа КР556РТ11 или КР556РТ17. В зависимости от используемого блока 1 ПЗУ формирователя 4 необходимо по-разному кодировать. При использовании блока 1 на фиг. 2 колировка и функционирование форгания в освобождаемые разряды.

При ЦП устройство функционирует так же, как и при ЛП, с тем отличием, что на входе 11 устанавливается логическая «1. а на выходе 16 устанавливается логический 50 «О. В результате на выход 9 передается код (без крайнего левого разряда) с входа 6 для вдвигания соответствующей его правой части в освобождаемые разряды, что необходимо для формирования циклически сдвимирователя 4 осуществляются в соответст- 55 НУТОГО вправо кода. При этом, при испольвии с табл. 1 (при , ).

При использовании .блока 1 на фиг. 3 кодировка и функционирование формировазовании блока 1 (фиг. 3) на ()-ом разряде входа 17 формируется логический «О, под управлением которого на вход 40

теля 4 осуществляются в соответствии о табл. 2 (при , ).

По таблице 2 видно, что для формирования требуемых сигналов на ()-ом разряде входа 17 формирователя достаточно в формирователь 4 для блока I (фиг. 3) ввести элемент И, первый и второй входы которого соединены с входами 12 и 13, а выход элемента И соединен с разрядом входа 17. Остальные разряды входа 17

необходимо соединить с выходом ПЗУ, в

0 необходимо соединить с выходом ПЗУ, в

котором ()-ый разряд кодируется

инверсным значением по сравнению с ПЗУ в формирователе 4 для блока на фиг. 2 (табл. 1).

Устройство (фиг. 1) функционирует следующим образом.

В исходном состоянии на входе 6 (фиг. 1) устанавливается сдвигаемый код. На входе 7 устанавливается код знака. На входе 14 устанавливается код величины сдвига. На 0 входах -11 -13 задается ,од гипа сдвига. Возможны следующие типы сдвига при установке соответствующих кодов на входах 11-13: логический сдвиг вправо (ЛП) при коде 111; арифметический сдвиг вправо (АП) при коде 011; циклический сдвиг вправо (ЦП) при коде 101; циклически) сДвиг влево (ЦЛ) при коде 100; логический сдвиг влево (ЛЛ) при коде 110.

На выходе 10 формируется соответствующим образом сдвинуты код д При ЛП на выходе 16 формируемся логическая ., блокирующая коммутатор 2. В результате на выходе 9 формируется нулевой код. На входе 17 формируется код маски в соответствии с табл. 1 или 2, т. е. нулевой код маски (маска отсутствует). На вход 18 передается код с входа 14. В результате в блоке 1 осуществляется сдвиг вправо двоичного кода, установленного на входе 6 с заполнением освобождаемых разрядов логическим «(Ь, так как логический «О устанавливается и на

5

5

входе 23, и на входах 24 и 40 (описание блоков 1 на фиг. 2 и 3). При АП устройство функционирует так же, как и при ЛП, с тем отличием, что на входе 11 устанавливается логический «О. В результате на выходе 16 формируется логический «О и на выход 9

передается с входа 7 код знака для вдви4Э передается с входа 7 код знака для вдвигания в освобождаемые разряды.

При ЦП устройство функционирует так же, как и при ЛП, с тем отличием, что на входе 11 устанавливается логическая «1. а на выходе 16 устанавливается логический 50 «О. В результате на выход 9 передается код (без крайнего левого разряда) с входа 6 для вдвигания соответствующей его правой части в освобождаемые разряды, что необходимо для формирования циклически сдвиНУТОГО вправо кода. При этом, при использовании блока 1 (фиг. 3) на ()-ом разряде входа 17 формируется логический «О, под управлением которого на вход 40

(фиг. 3) передается код с входа 37. Аналогично и при ЦЛ. Однако при ЦЛ на входе 18 формируется дополнительный код от кода на входе 14 благодаря .установке на входе 13 логического «О. Во всех описанных случаях на (-$--1)-ом разряде входа 17 (фиг. 3) формируется логическая «1 (табл. 2), благодаря чему код с входа 36 передается на разряды входа 39.

При ЛЛ устройство функционирует так же, как и при ЦЛ, с тем отличием, что на разрядах (0/7) входа 17 формируется код маски в зависимости от кода величины сдвига и от используемого блока 1 (в соответствии с табл. 1 или 2). Для определенны из К. бит) (при отсчете со стороны направления сдвига, начиная с нуля) кода на входе 6 и, следовательно, кода на выходе 9. На разрядах входа 39 (фиг. 3) формируется нулевой код. На вход 40 передается код с входа 37. В результате сдвигов в узле 38 на выходе 10 формируется код 010 111ЮООО 1 11 ЮООО 111 ЮООО 1 ИППР 00000000,00000000,00000000,00000.

10

Формула изобретения

ныи пример 11111111 11110000411 личину 29,

сдвига двоичного кода / 111111 П-ОЮЮЮ ЮЮГОЮ lOOOO 11110000 llllllll на ве- заданную двоичным кодом

ности рассмотрим для случая ЛЛ конкрет- ir разователь прямого кода в дополнительный

код, формирователь кода маски и элемент И, причем информационный вход устройства соединен с первым информационным входом блока сдвига, вход задания величин сдвига которого соединен с выходом преобразовате- 20 ля прямого кода в дополнительный код, информационный вход которого соединен соответствующими разрядами с информационным входом формирователя кода маски и с входом задания величин сдвига устройLf 011101 при , . Сдвинутый код должен быть равен 010111100001111 0000111100001111111100000000000000000000 000000000. На выходе 9 устанавливается код

R iiiiiiriiiiiiirioioioicnoioioio

111 ЮООО 111 ЮООО 111 ЮООО 11111111, так

на входе 11 установлена логичес- 2s CT8a пеРвыи ВХ°Д задания режима формикак

кая «1, а на выходе 16 - логический « На входе 17 в соответствии с табл.1 или 2 формируется код 00001111 или 000011100. На входе 18 формируется дополнительный код от кода LI, равный Мт,где .,

рователя кода маски соединен с входом разрешения преобразователя прямого кода в дополнительный код, с первым входом элемента И и с входом задания направления сдвига устройства, вход задания арифметиа . Код М устанавливается на раз- 30 ческого сдвига которого соединен с вторым

рядах входа 26 (фиг. 2), а т - на разрядах входа 27. На входе 25 (фиг. 2) формируется код 111100001111000011110000 1111111 ГОООООООО 00000000 00000000 00000000 (описание узла 19). На вход 24 передаются (К-1) младших разряда М-го байта (группы из /С бит) (при отсчете со стороны направления сдвига, т. е. справа налево, начиная с нуля) кода на выходе 9, т. е. подчеркнутого байта 10101010 кода R . В узле 20 (фиг. 2) осуществляются сдвиги вправо на m бит с вдвиганием кода, установленного на входе 24. То есть на выходе 10 формируется код 010111 ЮООО 111 ЮООО 111 ЮООО 11111111 ОООООООО 00000000 ОООООООО ООООО.

В блоке 1 на (фиг. 3) на выходе узла 30 формируется код 111 ЮООО 11110000 11110000 11111111 ОООООООО ОООООООО 0000000010101010, Подчеркнутая одной чет- той часть кода передается на выход (фиг. 3) с выхода 9, а часть кода, подчеркнутая двумя чертами, передается с входа 6

и представляет собой код того же подчеркнутого байта кода , передаваемого на вход 24 блока 1 на фиг. 2. Это связано с тем, что на выходе 9 устанавливается тот же код, что и на входе 6, а при сдвиге на М- К разрядов вправо в узле 30 на разрядах входа 36 всегда устанавливается код М-го байта, а на разрядах входа 37 - (К-1) младших разрядов М-го байта (трупвходом элемента И, выход которого соединен с входом блокировки коммутатора, отличающееся тем, что, с целью сокращения аппаратурных затрат, входы разрядов, кроме старшего, информационного входа устрой35 ства соединены соответственно с входами разрядов первого информационного входа коммутатора, входы разрядов второго информационного входа которого соединены со знаковым входом устройства, выход коммутатора соединен с вторым информаци40 онным входом блока сдвига, вход блокировки которого соединен с выходом формирователя кода маски, второй вход задания режима которого соединен с третьим входом элемента И и с входом задания цикличес:

45

кого сдвига устройства, вход задания арифметического сдвига которого соединен с управляющим входом коммутатора, выход блока савига является выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок сдвига содержит первый и вто50 рой узлы одностороннего сдвига и мультиплексор, причем первый и второй информационные входы блока сдвига соединены соответственно с первым и вторым информационными входами первого узла одностороннего сдвига, выход которого соединен с

55 первым информационным входом второго узла одностороннего сдвига, выход которого соединен с выходом .блока сдвига, входы младших разрядов входа задания величины из К. бит) (при отсчете со стороны направления сдвига, начиная с нуля) кода на входе 6 и, следовательно, кода на выходе 9. На разрядах входа 39 (фиг. 3) формируется нулевой код. На вход 40 передается код с входа 37. В результате сдвигов в узле 38 на выходе 10 формируется код 010 111ЮООО 1 11 ЮООО 111 ЮООО 1 ИППР 00000000,00000000,00000000,00000.

Формула изобретения

CT8a пеРвыи ВХ°Д задания режима формирователя кода маски соединен с входом разрешения преобразователя прямого кода в дополнительный код, с первым входом элемента И и с входом задания направления сдвига устройства, вход задания арифметического сдвига которого соединен с вторым

входом элемента И, выход которого соединен с входом блокировки коммутатора, отличающееся тем, что, с целью сокращения аппаратурных затрат, входы разрядов, кроме старшего, информационного входа устройства соединены соответственно с входами разрядов первого информационного входа коммутатора, входы разрядов второго информационного входа которого соединены со знаковым входом устройства, выход коммутатора соединен с вторым информационным входом блока сдвига, вход блокировки которого соединен с выходом формирователя кода маски, второй вход задания режима которого соединен с третьим входом элемента И и с входом задания цикличес:

кого сдвига устройства, вход задания арифметического сдвига которого соединен с управляющим входом коммутатора, выход блока савига является выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок сдвига содержит первый и второй узлы одностороннего сдвига и мультиплексор, причем первый и второй информационные входы блока сдвига соединены соответственно с первым и вторым информационными входами первого узла одностороннего сдвига, выход которого соединен с

первым информационным входом второго узла одностороннего сдвига, выход которого соединен с выходом .блока сдвига, входы младших разрядов входа задания величины сдвига которого соединены с входами разрядов входа задания величины сдвига второго узла одностороннего сдвига, второй информационный вход которого соединен с выходом мультиплексора, входы разрядов информационного входа которого соединены с входами соответствующих разрядов второго информационного входа блока сдвига, входы старших разрядов входа задания величины сдвига которого соединены с входами

сдвига которого соединены с входами разрядов входа задания величины сдвига соответственно второго и первого узлов одностороннего сдвига, входы /(-го и (N/К. - 1)- го разрядов вхо д.а блокировки блока сдвига соединены соответственно с управляющим входом мультиплексора и с вторыми входами элементов И группы, входы разрядов второго информационного входа мультиплексора соединены соответственно с входами

15

разрядов управляющего входа мультиплек- 10 (К. - 1)-х младших разрядов второго инфор- сора и с входами разрядов входа задания величины сдвига первого узла одностороннего сдвига, вход блокировки которого соединен с входом блокировки блока сдвига. 3. Устройство по п. 1, отличающееся тем, что блок сдвига содержит первый и второй узлы одностороннего сдвига, мультиплексор, группу элементов И, причем первый и второй информационные входы блока сдвига соединены соответственно с первым и вторым информационными входами первого узла одностороннего сдвига, выходы Л/-/( (, , , ) младших разрядов которых соединены с входами соответствующих разрядов первого информационного входа второго узла одностороннего сдвига, входы К старших р.азрядов первого информационного входа которого соединены с выходами соответствующих элементов И группы, первые входы которых соединены с выходами К старших разрядов

20

25

мационного входа блока сдвига, входы разрядов, кроме двух старших, входа блокировки которого соединены с входами соответствующих разрядов входа блокировки первого узла одностороннего сдвига, вход старшего разряда входа блокировки которого соединен с входом нулевого потенциала устройства.

}-}-(Р-1). /К-го разряда второго информапервого узла односторонних сдвигов, выходы 0 иионного входа первого узла одновибратор(К-1)-х старших разрядов которого соедине-ного сдвига, вход задания величины сдвига

ны соответственно с входами разрядов пер-которого соединен с входами задания вевого информационного входа мультиплексо-личины сдвига модулей сдвига, выход

ра, выход которого соединен с вторым инфор-/-го разряда /-го модуля сдвига является

мационным входом второго узла односто-выходом /-}-(/-)N/K-ro разряда выхода зроннего сдвига, выход которого соединен35 ла одностороннего сдвига, вход блокировки

с выходом блока сдвига, входы младшихкоторого соединен с входами блокировки

и старших разрядов входа задания величинмодулей сдвига.

Таблица 1

сдвига которого соединены с входами разрядов входа задания величины сдвига соответственно второго и первого узлов одностороннего сдвига, входы /(-го и (N/К. - 1)- го разрядов вхо д.а блокировки блока сдвига соединены соответственно с управляющим входом мультиплексора и с вторыми входами элементов И группы, входы разрядов второго информационного входа мультиплексора соединены соответственно с входами

(К. - 1)-х младших разрядов второго инфор-

мационного входа блока сдвига, входы разрядов, кроме двух старших, входа блокировки которого соединены с входами соответствующих разрядов входа блокировки первого узла одностороннего сдвига, вход старшего разряда входа блокировки которого соединен с входом нулевого потенциала устройства.

Фив. 2

Таблица 2

/7

v«

Фие.З

| Устройство для сдвига операндов | 1986 |

|

SU1330626A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига операндов | 1985 |

|

SU1298739A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 812045, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-26—Подача