f

Г21) 4317037/24-09

(22) 13.10.87

(46) 15.08.89. Бюл. № 30

(71)Ереванский политехнический институт им. К.Маркса и Ленинградский электротехнический институт связи им. проф. М.А.Бонч-Бруевича

(72)Л.М.Гольденберг и Р.Р.Бадалян (53) 681.32 (088.8)

(56) Погрибной В.А.Цифровые фильтры последовательного действия с им- пульсно-кодовой модуляцией. Радиотехника, , 1984, № 4, с. 33, рис. 2.

(54) ПОСЛЕДОВАТЕЛЬНЫЙ ЦИФРОВОЙ ФИЛЬТР

(57) Изобретение относится к вычислительной технике. Цель изобретения уменьшение частоты дискретизации и упрощение фильтра. Последовательный цифровой фильтр содержит кодер 1, шифратор 2, блоки памяти и сдвига 3 и 4, коммутатор 5, элемент ИСКШО- ЧАЩЕЕ ИЛИ-НЕ 6, сумматоры 7, 10, 11 и 12, дешифратор 8 и умножитель 9. Цель достигается за счет исключения многоразрядного умножения и сокрап1ения количества разрядов, необходимых д.пя представления отсчетов входного сигнала и весовых коэффициентов. 1 ил., 2 табл.

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| Устройство передачи телевизионного сигнала | 1988 |

|

SU1570028A1 |

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2003 |

|

RU2242085C1 |

| Цифровой фазометр | 1983 |

|

SU1188669A2 |

| ЦИФРОВОЙ ГЕНЕРАТОР СИНУСНО-КОСИНУСНЫХ ФУНКЦИЙ | 1973 |

|

SU399851A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

Изобретение относится к вычислительной технике. Цель изобретения - уменьшение частоты дискретизации и упрощение фильтра. Последовательный цифровой фильтр содержит кодер 1, шифратор 2, блоки памяти и сдвига 3 и 4, коммутатор 5, элемент Исключающее ИЛИ-НЕ 6, сумматоры 7, 10, 11 и 12, дешифратор 8 и умножитель 9. Цель достигается за счет исключения многоразрядного умножения и сокращения количества разрядов, необходимых для представления отсчетов входного сигнала и весовых коэффициентов. 1 ил., 2 табл.

СП

ND

315

Изобретение относится к вычислительной технике, в частности к технике цифровой обработки сигналов.

Цель изобретения - уменьшение частоты дискретизации и упрощение за счет исключения многоразрядного умножения и сокращения количества разрядов, необходимых для представления отсчетов входного сигнала и весовых коэффициентов.

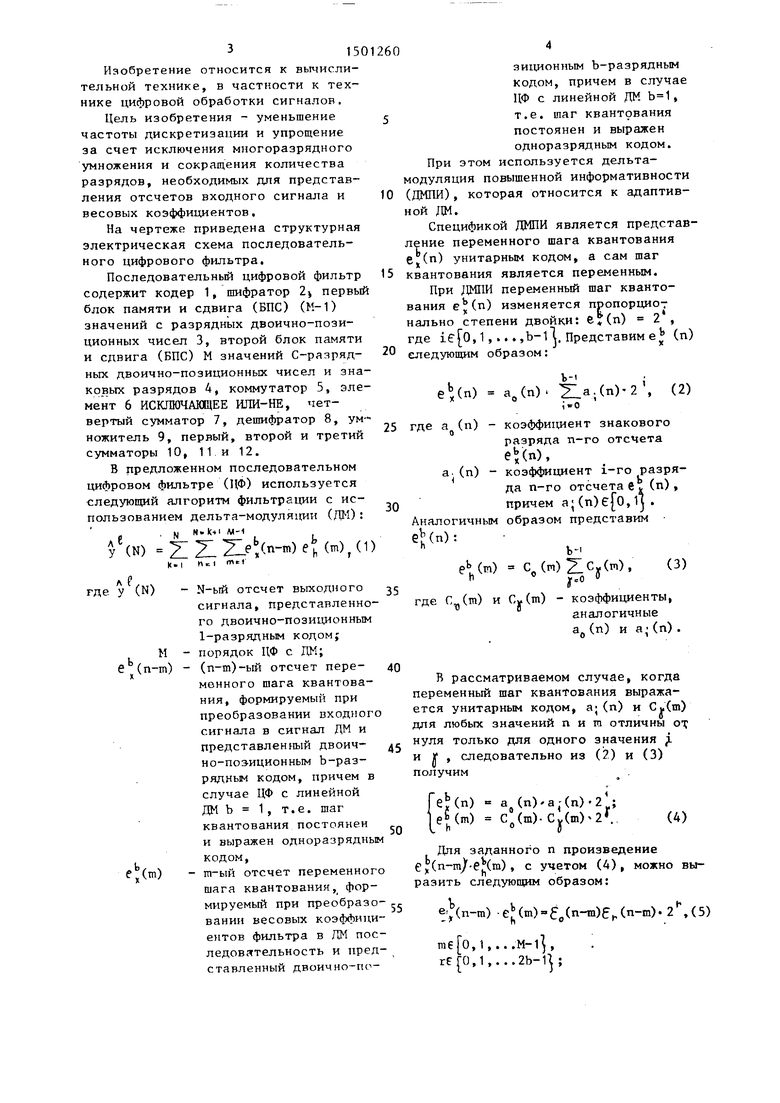

На чертеже приведена структурная электрическая схема последовательного цифрового фильтра.

Последовательный цифровой фильтр содержит кодер 1, шифратор 2 первы блок памяти и сдвига (БПС) (М-1) значений с разрядных двоично-позиционных чисел 3, второй блок памяти и сдвига (БПС) М значений С-разряд- ных двоично-позиционных чисел и знаковых разрядов А, коммутатор 5, элемент 6 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, четвертый сумматор 7, дешифратор 8, ум ножитель 9, первый, второй и третий сумматоры 10, 11 и 12.

В предложенном последовательном цифровом фильтре (ЦФ) используется следующий алгоритм фильтрации с ис

пользованием дельта-модуляции (ДМ):

N

N. Ic-ti М-1

k.i hci

I

,п-т)е (m),(1)

e

де у (N) - N-ый отсчет выходного 35 сигнала, представленного двоично-позиционным 1-разрядным кодом; М - порядок ЦФ с ДМ; е (n-m) - (п-т)-ый отсчет пере- 40 манного шага квантования, формируемый при преобразовании входного сигнала в сигнал ДМ и представленный двоич- д5 но-позиционным Ь-раз- рядным кодом, причем в случае ЦФ с линейной ДМ b 1, т,е. шаг квантования постоянен и выражен одноразрядным кодом,

f (т) - т-ый отсчет переменного шага квантования, формируемый при преобразо-, вании весовых коэффициентов фильтра в ДМ последовательность и пред- ставленный двоично-по50

зипяонным Ь-разрядным кодом, причем в случае ЦФ с линейной ДМ , т.е, шаг квантования постоянен и выражен одноразрядным кодом. При этом используется дельта- модуляция повышенной информативности (ДМПИ), которая относится к адаптивной ДМ.

Спецификой ДМЦИ является представление переменного шага квантования е(п) унитарным кодом, а сам шаг квантования является переменным.

При ДМПИ переменный шаг квантования е(п) изменяется пропорцио7 нально степени двойки: в,(п) 2 , где ,1,... ,Ь-Н. Представим е (п) следующим образом:

(п) а„(п). .(n) 2 (2)

i-o

где а (п) - коэффшщент знакового разряда п-го отсчета

е(п),

а (п) - коэффициент i-ro разряда п-го отсчетаеV (п), причем а (п),1. Аналогичным образом представим

ehn):

Ьн

e l(m) с (n)21c(m), (3) п

где С(т) и Cv, (т) - коэффициенты,

аналогичные а,(п) и а- (п) .

В рассматриваемом случае, когда переменный шаг квантования выражается унитарным кодом, а; (п) и Cu(in) для любых значений пит отличны о- нуля только для одного значения и г , следовательно из (2.) и (3) получим

е(п) еМш)

а(п)-а-(п)-2 ; С „(т).Су(т)2.

Г

(4)

Для заданного п произведение e(n-mj -e(m) , с учетом (4), можно выразить следуюш м образом:

%(n-m) -eJ(m) f(n-m)e(п-m).2(5)

,1,.,,M-1, rf ,1,... 2b-U ;

б(п-т) л,(n-m) @ СдСт); (6)

г

i У

где 5 (n-m) и f(n-m) - коэффициенты,

аналогичные з,(п) , а, (п) и Cg(m),C(m)

Учитывая (5), (6), (7) перепиигем выражение (1) следующим образом: К1 М-1 21 ZlZfo - (n-m).2(8

М . « А. /ч

):

k,i Пг1 mmO

Из (5), (6), (7) следует, что для определения произведения e(n-m) 6 (га) достаточно определить коэффициент знакового разряда в соответствии с (6) и значение отличного от нуля разряда г в соответствии с (7). Сле- довательно, при выполнении свертки в соответствии с алгоритмом (8) операция умножения перерождается в операцию управляемого сдвига. Имеется в виду, что произведение унитарных кодов также является унитарным кодом, причем номер единичного разряза произведения определяется суммой номеров единичных разрядов сомножителей.

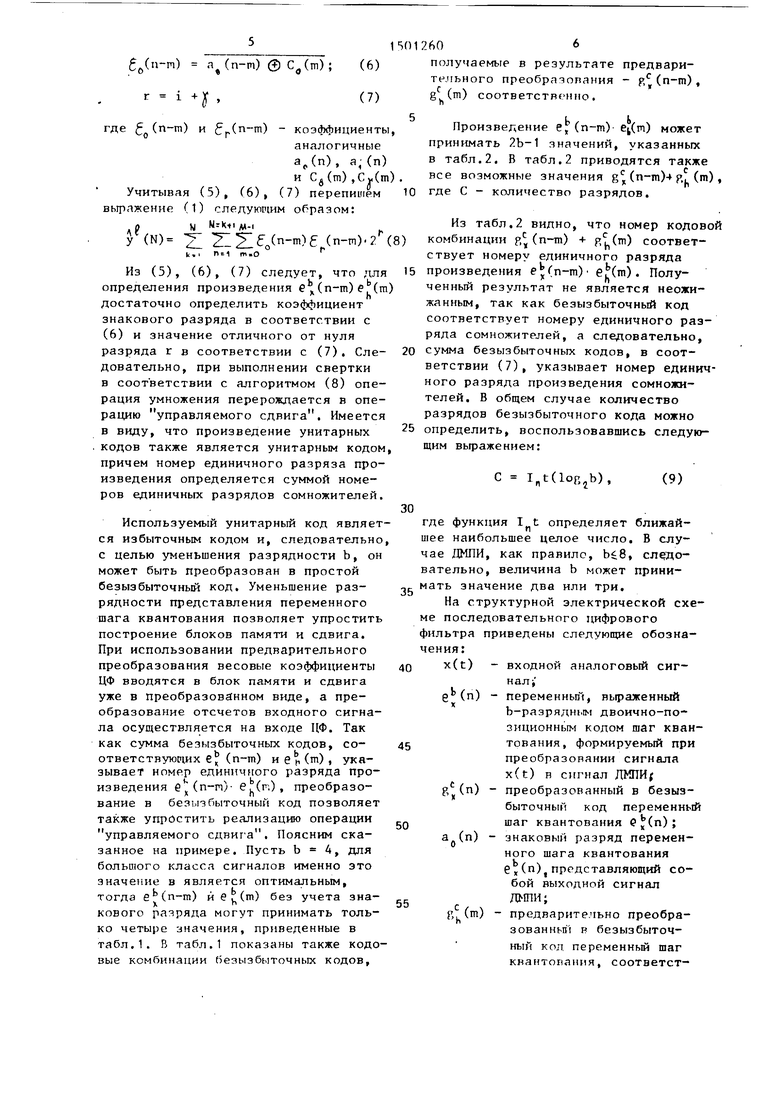

Используемый унитарный код является избыточным кодом и, следовательно с целью уменьшения разрядности Ь, он может быть преобразован в простой безызбыточный код. Уменьшение раз- рядности представления переменного шага квантования позволяет упростить построение блоков памяти и сдвига. При использовании предварительного преобразования весовые коэффициенты ЦФ вводятся в блок памяти и сдвига уже в преобразованном виде, а преобразование отсчетов входного сигнала осуществляется на входе ЦФ. Так как сумма безызбыточных кодов, со- ответствуюрщх е (п-т) и е (i (m) , указывает номер единичного разряда произведения е(п-п)- е( 0, преобразование в безызбыточный код позволяет также упростить реализацию операции управляемого сдвига. Поясним сказанное на примере. Пусть b 4, для большого класса сигналов именно это значение в является оптимальным,

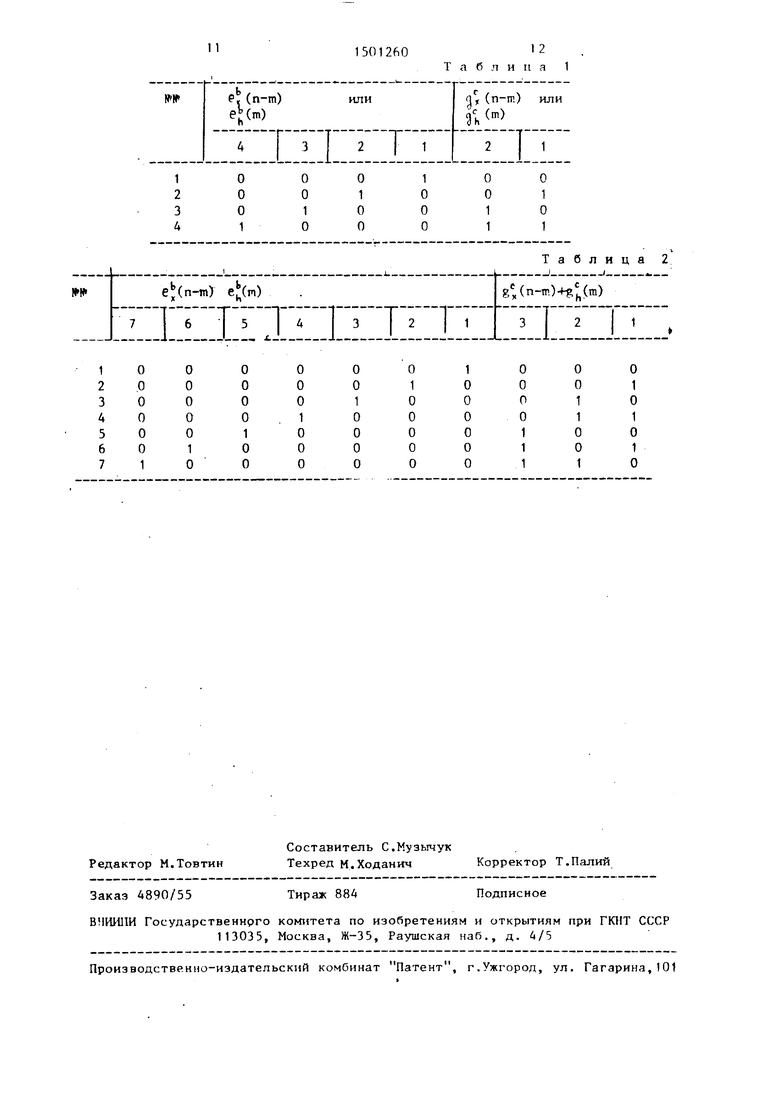

тогда e (n-m) и е (ni) без учета зна- X

кового разряда могут принимать только четыре значения, приведенные в табл.1. В табл.1 показаны также кодовые комбинации безызбыточных кодов.

S01

.

Ю 8)

5 20

2606

получаемые в результате предварительного преобразования - р, (п-т) ,

g.(га) соответственно.

п

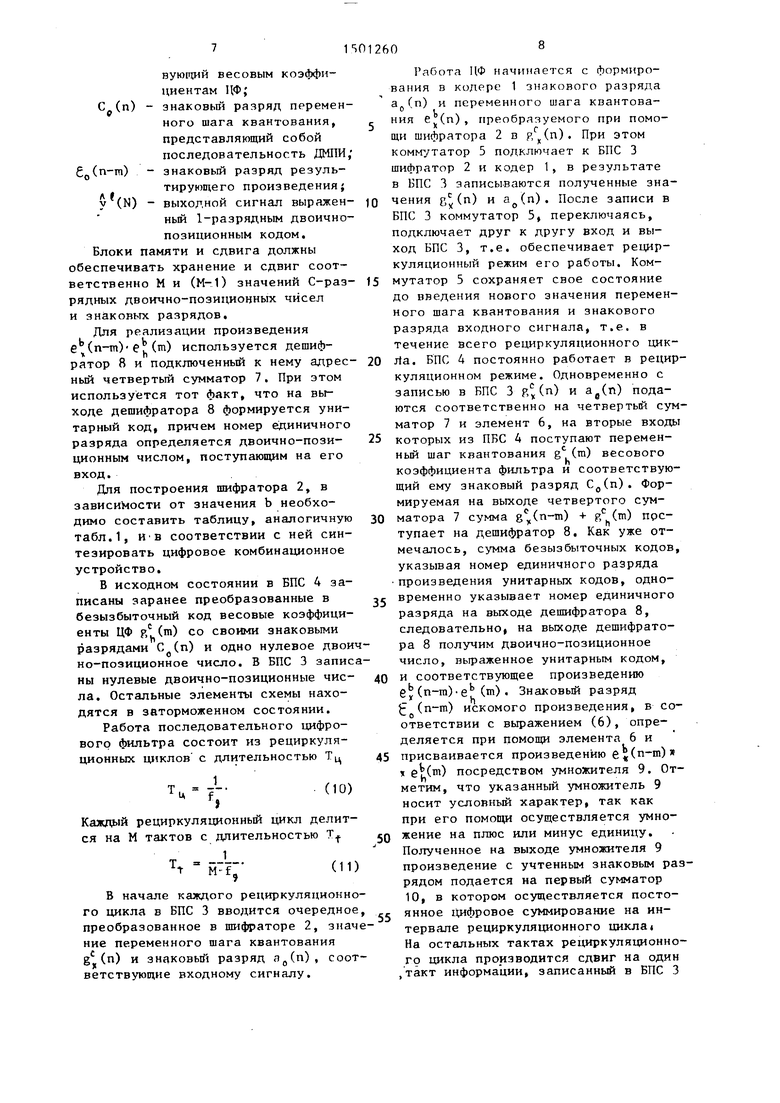

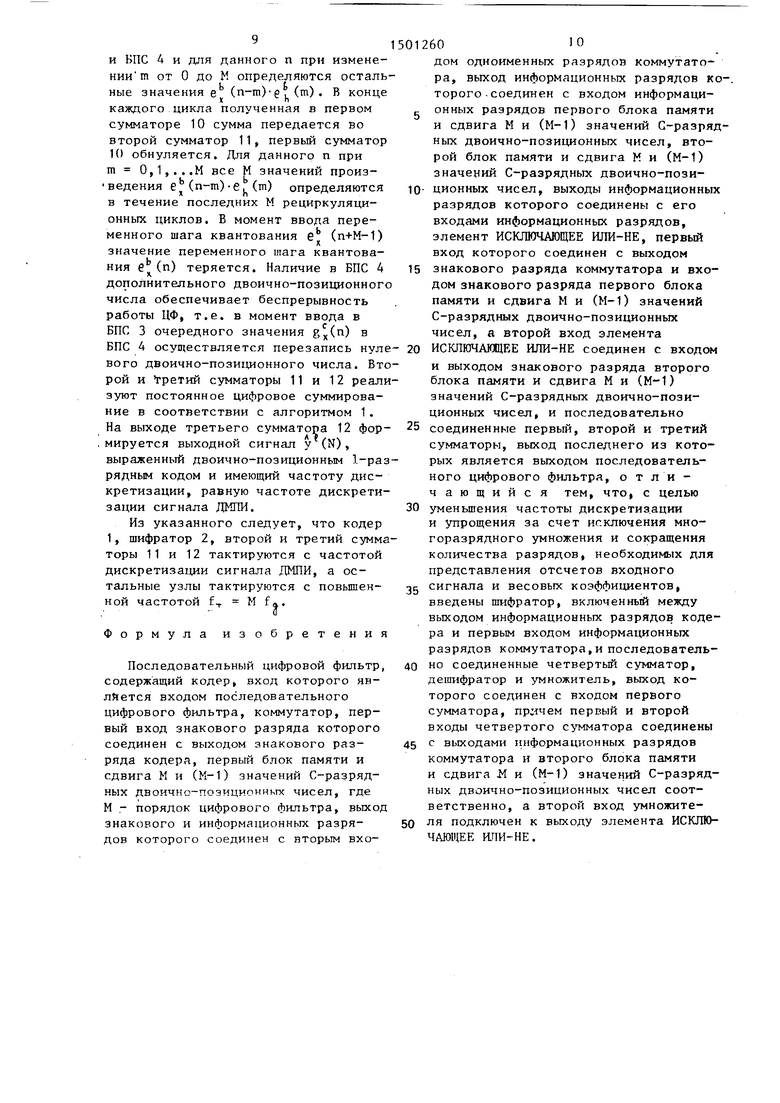

Произведение е, (n-m) eg(in) может принимать 2Ь-1 значений, указанных в табл.2. В табл.2 приводятся также

все возможные значения g (n-ni)- Р, (п),

,,

где С - количество разрядов.

Из табл.2 видно, что номер кодовой комбинации р, (п-т) + R(m) соответствует номеру единичного разряда произведения е(п-т) е(т). Полученный результат не является неожи- жанным, так как безызбыточный код соответствует номеру единичного разряда сомножителей, а следовательно, сумма безызбыточных кодов, в соответствии (7), указывает номер единичного разряда произведения сомножителей. В общем случае количество разрядов безызбыточного кода можно определить, воспользовавшись следующим вьфажением:

(),

(9)

где функция определяет ближайшее наибольшее целое число. В случае ДМПИ, как правило, , следовательно, величина b может принимать значение два или три.

На структурной электрической схеме последовательного цифрового фильтра приведены следующие обозначения:

x(t) - входной аналоговый сигнал j

е (п) - переменньп, выраженный Ь-разрядн1.1М двоично-по- зиционньгм кодом шаг квантования, формируемый при преобразовании сигнала x(t) в сигнал ЛМПИ; Й(п) - преобразованный в безызбыточный код переменны шаг квантования б(п); а (п) - знаковый разряд переменного шага квантования 6х(),представляющий собой выходной сигнал ДЬШИ

р, (ш) - предварительно преобра- зованньп в безызбыточный код переменный шаг ккантопания, соответствуюг1 1й весовым коэффициентам ЦФ;

Ср(п) - знаковый разряд переменного шага квантования, представляющий собой последовательность ДМПИ д(п-т) - знаковый разряд результирующего произведения{ у (N) - выходной сигнал выраженный 1-разрядным двоично позиционным кодом, Блоки памяти и сдвига должны обеспечивать хранение и сдвиг соответственно М и (М-1) значений С-раз рядных двоично-позиционных чисел и знаковых разрядов.

Для реализации произведения е (n-m) е (in) используется дешиф п

ратор о и подключенный к нему адресный четвертый сумматор 7, При этом используется тот факт, что на выходе дешифратора 8 формируется унитарный код, причем номер единичного разряда определяется двоично-позиционным числом, поступающим на его вход.

Для построения шифратора 2, в зависимости от значения b необходимо составить таблицу, аналогичную табл,1, И в соответствии с ней синтезировать цифровое комбинационное устройство,

В исходном состоянии в БПС 4 записаны заранее преобразованные в безызбыточный код весовые коэффициенты ЦФ P, u(i) со своими знаковыми разрядами С(п) и одно нулевое двоино-позиционное число, В БПС 3 записны нулевые двоично-позиционные числа. Остальные элементы схемы находятся в заторможенном состоянии.

Работа последовательного цифрового фильтра состоит из рециркуляционных циклов с длительностью Т

1

(10)

Каждый рециркуляционный цикл делится на М тактов с длительностью Т

1

M-f,

(11)

В начале каждого рециркуляционного цикла в БПС 3 вводится очередное, преобразованное в шифраторе 2, значение переменного шага квантования gj, (п) и знаковый разряд ад(п), соответствующие входному сигналу.

Габота ЦФ начинается с формирования в кодере 1 знакового разряда ) и переменного шага квантования е(п), нреобрязуемого при помощи шифратора 2 в р,(п). При этом коммутатор 5 подключает к БПС 3 шифратор 2 и кодер 1, в результате в БПС 3 записываются полученные зна- чения Су(п) и а(п). После записи в БПС 3 коммутатор 5, переключаясь, подключает друг к другу вход и выход БПС 3, т,е, обеспечивает рециркуляционный режим его работы, Ком- мутатор 5 сохраняет свое состояние до введения нового значения переменного шага квантования и знакового разряда входного сигнала, т.е. в течение всего рециркуляционного цик- Jta, БПС 4 постоянно работает в рециркуляционном режиме. Одновременно с записью в БПС 3 р, (п) и ) подаются соответственно на четвертый сумматор 7 и элемент 6, на вторые входы которых из ПБС 4 поступают переменный шаг квантования g (га) весового коэффициента фильтра и соответствующий ему знаковый разряд C(n), Формируемая на выходе четвертого сумматера 7 сумма g(n-m) + g (m) прс- тупает на дешифратор 8, Как уже отмечалось, сумма безызбыточных кодов, указывая номер единичного разряда произведения унитарных кодов, одновременно указывает номер единичного разряда на выходе дешифратора 8, следовательно, на выходе дешифратора 8 получим двоично-позиционное число, ньфаженное унитарным кодом,

и соответствующее произведению е (п-га)-е (tn) . Знаковый разряд (п-га) искомого произведения, в соответствии с выражением (6), определяется при помощи элемента 6 и

присваивается произведению e() и еКт) посредством умножителя 9. Отметим, что указанный умножитель 9 носит условный характер, так как при его помощи осуществляется умножение на плюс или минус единицу. Полученное на выходе умножителя 9 произведение с учтенным знаковым разрядом подается на первый сумматор 10, в котором осуществляется постоянное Цифровое суммирование на интервале рециркуляционного цикла На остальных тактах рециркуляционного цикла производится сдвиг на один ,такт информации, записанный в БПС 3

1

и БПС А и для данного п при изменении m от О до М определяются остальные значения е (п-т)-р(т). В конце

Xп

каждого цикла полученная в первом сумматоре 10 сумма передается во второй сумматор 11, первый сумматор 10 обнуляется. Для данного п при m 0,1,...М все М значений произведения е(n-m)-е(т) определяются в течение последних М рециркуляционных циклов. В момент ввода переменного шага квантования е (п+М-1) значение переменного шага квантования е(п) теряется. Наличие в БПС 4 дополнительного двоично-позиционного числа обеспечивает беспрерывность работы ЦФ, т.е. в момент ввода в БПС 3 очередного значения g(n) в БПС 4 осуп1ествляется перезапись нулевого двоично-позиционного числа. Второй и третий сумматоры 11 и 12 реализуют постоянное цифровое суммирование в соответствии с алгоритмом 1. На выходе третьего сумматора 12 формируется выходной сигнал у (N), выраженный двоично-позиционным 1-разрядным кодом и имеющий частоту дискретизации, равную частоте дискретизации сигнала ДМПИ.

Из указанного следует, что кодер 1, шифратор 2, второй и третий сумматоры 11 и 12 тактируются с частотой дискретизации сигнала ДМПИ, а остальные узлы тактируются с повьппенной частотой f. М «.

- б

Формула изобретения

Последовательный цифровой фильтр, содержащий кодер, вход которого яв- йется входом последовательного цифрового фильтра, коммутатор, первый вход знакового разряда которого соединен с выходом знакового разряда кодера, первый блок памяти и сдвига М и (К-1) значений С-разряд- ных двоично-позиционных чисел, где М - порядок цифрового фильтра, выход знакового и информационных разрядов которого соединен с вторым вхо0126010

дом одноименных разрядов коммутатора, выход информационных разрядов которого -соединен с входом информаци- g онных разрядов первого блока памяти и сдвига М и (М-1) значений С-разряд- ных двоично-позиционных чисел, второй блок памяти и сдвига М и (М-1) значений С-разрядных двоично-пози- 10- ционных чисел, выходы информационных разрядов которого соединены с его входами информационных разрядов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый вход которого соединен с выходом 15 знакового разряда коммутатора и входом знакового разряда первого блока памяти и сдвига М и (М-1) значений С-разрядных двоично-позиционных чисел, а второй вход элемента

20 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ соединен с входом

и выходом знакового разряда второго блока памяти и сдвига М и (М-1) значений С-разрядньгх двоично-позиционных чисел, и последовательно

25 соединенные первый, второй и третий сумматоры, выход последнего из которых является выходом последовательного цифрового фильтра, отличающийся тем, что, с целью

30 уменьшения частоты дискретиз.ации и упрощения за счет исключения многоразрядного умножения и сокращения количества разрядов, необходимых для представления отсчетов входного

35 сигнала и весовых коэффициентов, введены шифратор, включенный между выходом информационных разрядов кодера и первым входом информационных разрядов коммутатора,и последователь40 но соединенные четвертый сумматор, дешифратор и умножитель, выход которого соединен с входом первого сумматора, прлчем первый и второй входы четвертого сумматора соединены

45 с выходами информационных разрядов коммутатора и второго блока памяти и сдвига К и (М-1) значений С-разрядных двоично-позиционных чисел соответственно, а второй вход умножите0 ля подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ И.ПИ-НЕ.

Редактор М.Товтин

Составитель С.Музычук Техред М.Ходанич

Заказ 4890/55

Тираж 88А

ВНИИ11И Государственнрго комитета по изобретениям и открытиям при ГК11Т СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Таблица 2

Корректор Т.Палий

Подписное

Авторы

Даты

1989-08-15—Публикация

1987-10-13—Подача