1

Изобретение относится к автоматике и вычислительной технике и может найти применение в управляющих системах и гибридных вычислительных устройствах для вычисления в следящем режиме логарифмической функции 1ц (.1 + х) от аналогового сигнала с представлением результата в цифровой форме.

Целью изобретения является повышение быстродействия и расширение частотного диапазона обрабатьюа емых сигналов.

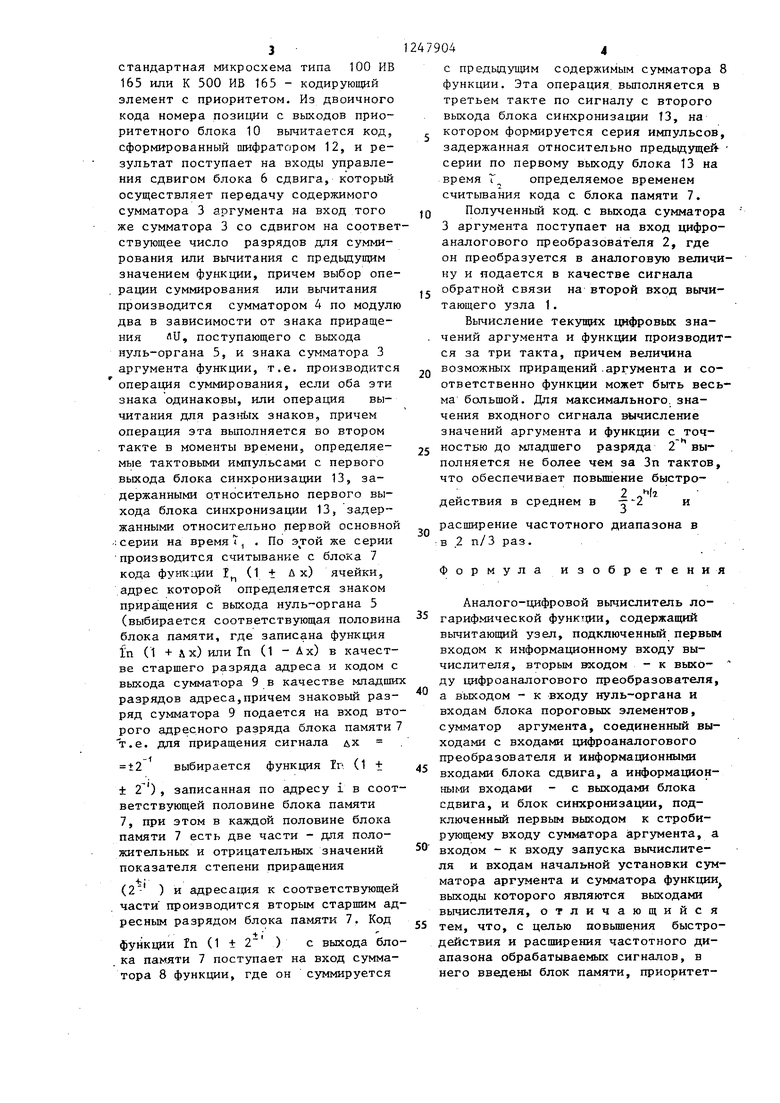

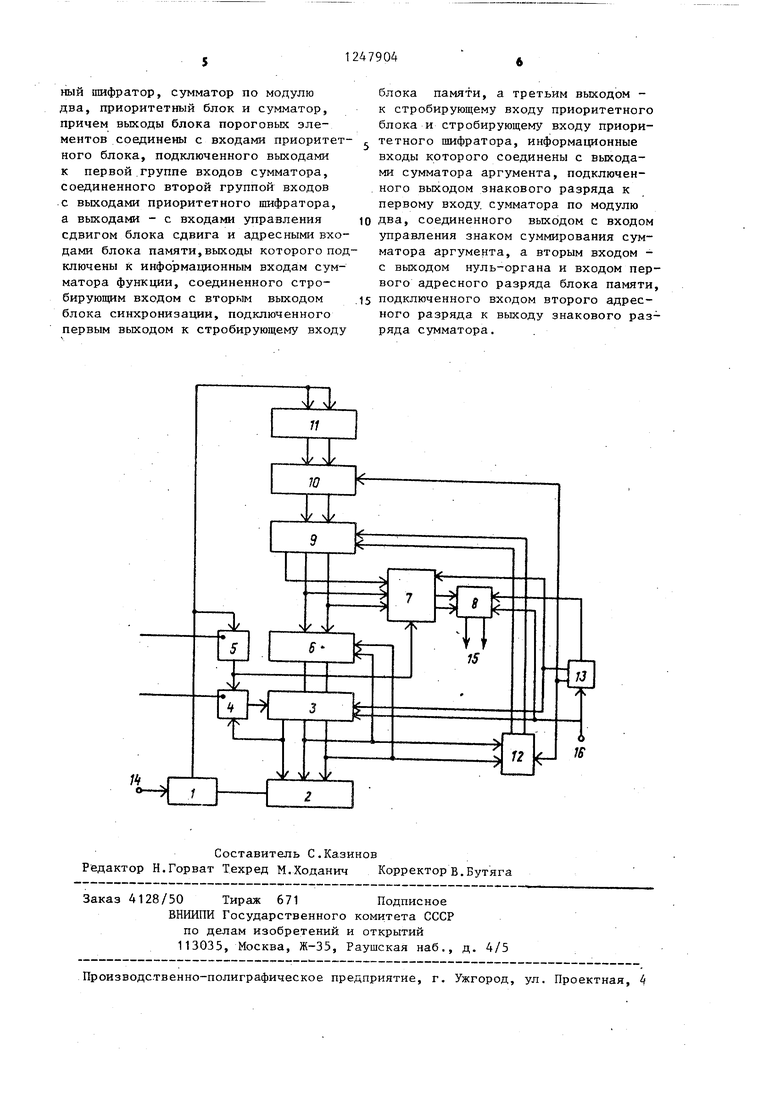

На чертеже изображена блок-схема аналого-цифрового вычислителя лога- рифмической функции.

Аналого-цифровой вычислитель логарифмической функции содержит вычитающий узел 1, цифроаналоговый преобра;зователь 2, сумматор 3 аргумента, сумматор по модулю два 4,нуль орган 5, блок 6 сдвига, блок 7 памяти, сумматор 8 функции, сумматор 9, приоритетный блок 10, блок 11 пороговых элементов, приоритетный пшфратор 12, блок 13 синхронизации, информа- ционньй вход 14, выходы 15 вычислителя и вход 16 запуска.

Вычислитель работает следующим образом.

Перед началом работы на вход 16 подается сигнал, которьй обнуляет сумматор 8 функции и устанавливает код 1 в сумматор 3 аргумента, т.е. п разрядов (где п - разрядность преобразователя 2) младший и п разрядов старшей части сумматора 3 обнуляются, а в мпадший разряд целой части этого сумматора заносится единица. Таким образом, для нулевого значения аргумента х О сумматор 3 аргумента устанавливается в единичное значение, так как вычисляется функция 1 (1-х) для /X/ 1. Блок 7 памяти содержит 4 п слов для выбранной разрядности устройства п,причем в первой половине (странице) блока 7 памяти записаны коды функции in (1 + х) для значений аргумента

X 2 ,, 2,..., п, а во второй половине этого блока записа ны коды функции In (1 - х) для тех же значений аргумента. Адресация к той же или иной половине блока памяти осуществляется сигналом с выхода нуль-органа 5 (первый адресный разряд блока 7), а адресация внутри каждой половины блока 7 происходит

1

- 5

25

2479042

по сигналам с выхода знакового разряда сумматбра 9 (второй адресный разряд блока 7) и с остальных выходов сумматора 9 (младпше разряды адреса блока 7).

Сигнал, поступающий по входу 16, запускает блок 13 синхронизации, который вьщает три серии и и fflyльcoв основная серия - по третьему выходу, задержанная на время (t) переходного процесса в приоритетном блоке 10, кодирующем элементе 12 и сумматоре 9 - по первому выходу и вторая, задержанная на время (Г ) переходного процесса в сумматоре 3 аргумента и блоке 7 памяти - по второму выходу блока 13.

Напряжение ( Д U) рассогласования (между входным напряжением аналогово- 20 го сигнала (1+х) по входу 14 и напря- жени-ем. обратной связи с выхода циф- роаналогового преобразователя 2 с выхода вычитающего узла 1 подается на вход нуль-органа 5 и входы блока 11 пороговых элементов. Пороговые элементы блока 11 срабатывают при достижении напряжением рассогласования значений порогов, на которые настроены соответствующие пороговые элементы (например, по двоичному закону: 1,2, 4,..., 2 условных единиц младшего разряда 2 сумматора 8 функции). В первом такте приоритетный блок 10 в момент времени, оп35 редепяемые тактовыми импульсами с третьего выхода блока синхронизации, определяет старший по весу пороговьш элемент блока 11 из числа сработавших и выдает сигнал на соответству40 ющие выходы, где формируется номер позиции (разряда) в котором находится единица в позиционном коде старшего сработавшего порогового элемента блока 11. Этот позиционный дво45 ичный код представляет собой приращения входного сигнала, округленные до значения, кратного степени двойки, т.е. представляют собой одну единицу в соответствующем разряде ко50 да (позиционньй код). В этом же такте шифратор 12 определяет аналогичным образом номер старшей единицы в коде сумматора 3 аргумента, т.е. производится выделение старшей едини55 ЦЫ из кода старших п разрядов числа в сумматоре 3 аргумента и двоичное кодирование его номера. В качестве шифратора 12 может использоваться

30

стандартная микросхема типа 100 ИВ 165 или К 500 ИВ 165 - кодирующий элемент с приоритетом. Из двоичного кода номера позиции с выходов приоритетного блока 10 вычитается код, сформированный шифратором 12, и результат поступает на входы управления сдвигом блока 6 сдвига, который осуществляет передачу содержимого сумматора 3 аргумента на вход того же сумматора 3 со сдвигом на соответствующее число разрядов для суммирования или вычитания с предьщущим значением функции, причем выбор опе- рации суммирования или вычитания производится сумматором 4 по модулю два в зависимости от знака приращения яи, поступающего с выхода нуль-органа 5, и знака сумматора 3 аргумента функции, т.е. производится операция суммирования, если оба эти знака одинаковы, или операция вычитания для разн4)1х знаков, причем операция эта выполняется во втором такте в моменты времени, определяемые тактовыми импульсами с первого выхода блока синхронизации 13, задержанными относительно первого выхода блока синхронизации 13, задержанными относительно первой основной Серии на время Т . По же серии производится считывание с блока 7 кода функдаи 1 (1 + Дх) ячейки, адрес которой определяется знаком прира щения с выхода нуль-органа 5 (выбирается соответствующая половина блока памяти, где записана функция In (1 + &х) или In (1 - Ах) в качестве старшего разряда адреса и кодом с выхода сумматора 9 в качестве младших разрядов адреса,причем знаковый разряд сумматора 9 подается на вход второго адресного разряда блока памяти 7 т.е. для приращения сигнала дх

t2 выбирается функция 1г (1 +

± 2) , записанная по адресу i в соответствующей половине блока памяти 7, при этом в каждой половине блока памяти 7 есть две части - для положительных и отрицательных значений показателя степени приращения

(2- ) и адресация к соответствующей части производится вторым старшим адресным разрядом блока памяти 7. Код

функции In (1 ± ) с выхода блока памяти 7 поступает на вход сумматора 8 функции, где он суммируется

479044

с предьщущим содержимым сумматора 8 функции. Эта операция, выполняется в третьем такте по сигналу с второго выхода блока синхронизации 13, на , котором формируется серия импульсов, задержанная относительно предыдущей- серии по первому выходу блока 13 на время Г определяемое временем считьшания кода с блока памяти 7.

jQ Полученный код. с выхода сумматора 3 аргумента поступает на вход цифро- аналогового преобразователя 2, где он преобразуется в аналоговую величину и подается в качестве сигнала

и обратной связи на второй вход вычитающего узла 1.

Вычисление текущих цифровых зна- . чений аргумента и функ1Д1И производится за три такта, причем величина

2Q возможных приращений .аргумента и соответственно функции может быть весьма большой. Для максимального, значения входного сигнала вычисление значений аргумента и функции с точ25 ностью до младшего разряда 2 выполняется не более чем за Зп тактов, что обеспечивает повышение быстро30

2 (а действия в среднем в -2 и

расширение частотного диапазона в

: в .2 п/3 раз.

Формула изобретени

Аналого-цифровой вычислитель ло- гарифмической функтщи, содержащий вычитающий узел, подключенный первым входом к информационному входу вычислителя, вторым входом - к выходу цифроаналогового преобразователя, а выходом - к входу нуль-органа и входам блока пороговых элементов, сумматор аргумента, соединенный выходами с входами цифроаналогового преобразователя и информационными входами блока сдвига, а информационными входами - с выходами блока сдвига, и блок синхронизации, подключенный первым выходом к строби- рующему входу сумматора аргумента, а

входом - к входу запуска вычислителя и входам начальной установки сумматора аргумента и сумматора функции выходы которого являются выходами вычислителя, отличающийся тем, что, с целью повьш)ения быстродействия и расширения частотного диапазона обрабатываемых сигналов, в него введены блок памяти, приоритетный шифратор, сумматор по модулю два, приоритетный блок и сумматор, причем выходы блока пороговых элементов соединены с входами приоритетного блока, подключенного выходами к первой.группе входов сумматора, соединенного второй группой входов .с выходами приоритетного шифратора, а выходами - с входами управления сдвигом блока сдвига и адресными входами блока памяти,выходы которого под ключены к информационным входам сумматора функции, соединенного стро- бирующим входом с вторым выходом блока синхронизации, подключенного первым выходом к стробирующему входу

Составитель С.Казинов Редактор Н.Горват Техред М.Ходанич Корректор В.Бутяга

Заказ 4128/50 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

блока памяти, а третьим выходом - к стробирующему входу приоритетного блока и стробирующему входу приоритетного шифратора, информационные входы которого соединены с выходами сумматора аргумента, подключенного выходом знакового разряда к первому входу, сумматора по модулю

два, соединенного выходом с входом управления знаком суммирования сумматора аргумента, а вторым входом - с выходом нуль-органа и входом первого адресного разряда блока памяти,

подключенного входом второго адресного разряда к выходу знакового разряда сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Аналого-цифровое устройство для возведения в куб | 1985 |

|

SU1251113A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

Изобретение относится к области автоматики и вычислительной техники. Вычислитель содержит вьтчитающий узел, цифроаналоговый преобразователь,сумматор аргумента, сумматор по модулю два, нуль-орган, блок сдвига,блок памяти, сумматор функции, сумматор, приоритетный блок, блок пороговых эле- ме;нтов, приоритетный шифратор и блок синхронизации. Повьппение быстродействия и расширение частотного диапазона обрабатываемых сигналов достигается на основе использования переменного шага уравновешивания входного аналогового сигнала, что позволяет обеспечить вычисление значений аргумента и функции с точностью до младшего разряда 2 (п-разрядность вычислителя) за время не более 3 п тактов работы вычислителя. 1 ил. с $ (Л 1ЧЭ J СО

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU955110A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Введение в кибернетическую технику | |||

| Обработка физической информации | |||

| Под общей редакцией Б.Н.Малиновского, Киев: Наукова думка, 1979, с.166- 168, рис | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-27—Подача