Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и синтеза частот.

Цель изобретения - повышение быстродействия и надежности работы.

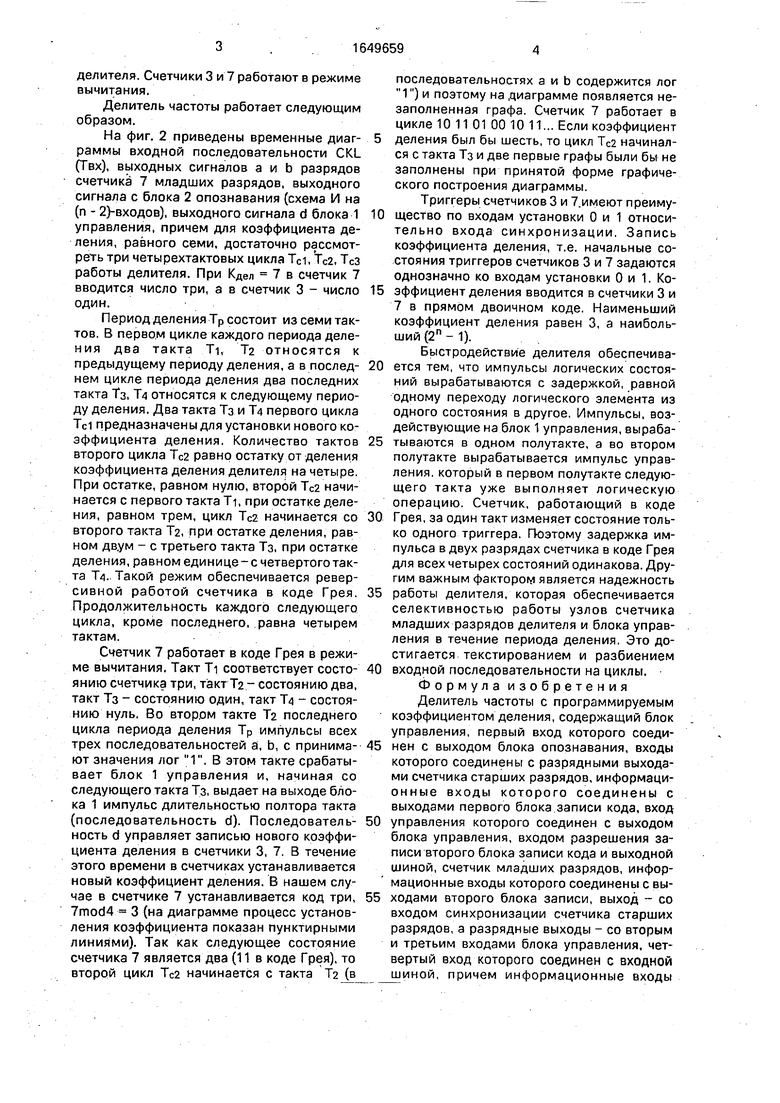

На фиг. 1 показана структурная схема делителя частоты; на фиг. 2 - временные диаграммы, поясняющие работу делителя.

Делитель частоты содержит блок 1 управления, блок 2 опознавания, счетчик 3 старших разрядов, первый и второй блоки 4 и 5 записи кода, выходную шину 6, счетчик 7 младших разрядов, входную шину 8, кодовые шины 9, 10 и 11 старших разрядов, преобразователь 12 двоичного кода в код Грея, кодовые шины 13 и 14 младших разрядов.

Первый вход блока 1 управления соединен с выходом блока 2 опознавания,второй и третий входы - с разрядными выходами счетчика 7 младших разрядов, четвертый вход - с входной шиной 8 и входом еинхро- низации счетчика 7 младших разрядов, а

выход - с-выходной шиной 6 и входами разрешения записи первого и второго блоков 4 и 5 записи кода. Входы блока 2 опознавания соединены с разрядными выходами счетчика 3 старших разрядов, вход синхронизации которого соединен с выходом счетчика 7 младших разрядов, а информационные входы - с выходами первого блока 4 записи кода, информационные входы которо/о соединены с кодовыми шинами 9, 10 и 11 старших разрядов.

Информационные входы счетчика 7 младших разрядов соединены с выходами второго блока 5 записи кода, информационные входы которого соединены с выходами преобразователя 12 двоичного кода в код Грея, входы которого соединены с кодовыми шинами 13 и 14 младших разрядов.

В рассматриваемом случае счетчик 7 - двухразрядный счетчик в коде Грея, счетчик 3 - трехразрядный двоичный счегчик, либо (п - 2)-разрядный где п - число разрядов

(Л

С

о

4 Ю О

ел чэ

делителя. Счетчики 3 и 7 работают в режиме вычитания.

Делитель частоты работает следующим образом.

На фиг. 2 приведены временные диаг- раммы входной последовательности CKL (Твх), выходных сигналов а и b разрядов счетчика 7 младших разрядов, выходного сигнала с блока 2 опознавания (схема И на (п - 2)-входов), выходного сигнала d блока 1 управления, причем для коэффициента деления, равного семи, достаточно рассмотреть три четырехтактовых цикла Тс1, ТС2, Тсз работы делителя. При Кдел 7 в счетчик 7 вводится число три, а в счетчик 3 - число один.

Период деления Тр состоит из семи тактов. В первом цикле каждого периода деле- ния два такта Ti, T2 относятся к предыдущему периоду деления, а в послед- нем цикле периода деления два последних такта Тз, Т4 относятся к следующему периоду деления. Два такта Тз и J4 первого цикла ТС1 предназначены для установки нового коэффициента деления. Количество тактов второго цикла ТС2 равно остатку от деления коэффициента деления делителя на четыре. При остатке, равном нулю, второй ТС2 начинается с первого такта TI, при остатке деления, равном трем, цикл ТС2 начинается со второго такта J2, при остатке деления, равном двум - с третьего такта Тз, при остатке деления, равном единице-с четвертого такта Тз. Такой режим обеспечивается реверсивной работой счетчика в коде Грея. Продолжительность каждого следующего цикла, кроме последнего, равна четырем тактам.

Счетчик 7 работает в коде Грея в режиме вычитания. Такт Ti соответствует состо- янию счетчика три, такт Т2 - состоянию два, такт Тз - состоянию один, такт Т4 - состоянию нуль. Во втором такте Т2 последнего цикла периода деления Тр импульсы всех трех последовательностей а, Ь, с принима- ют значения лог 1. В этом такте срабатывает блок 1 управления и, начиная со следующего такта Тз, выдает на выходе блока 1 импульс длительностью полтора такта (последовательность d). Последователь- ность d управляет записью нового коэффициента деления в счетчики 3, 7. В течение этого времени в счетчиках устанавливается новый коэффициент деления. В нашем случае в счетчике 7 устанавливается код три, 7mod4 3 (на диаграмме процесс установления коэффициента показан пунктирными линиями). Так как следующее состояние счетчика 7 является два (11 в коде Грея), то второй цикл ТС2 начинается с такта Т2 (в

последовательностях а и b содержится лог 1) и поэтому на диаграмме появляется незаполненная графа. Счетчик 7 работает в цикле 10 11 01 00 10 11... Если коэффициент деления был бы шесть, то цикл ТС2 начинался с такта Тз и две первые графы были бы не заполнены при принятой форме графического построения диаграммы.

Триггеры счетчиков 3 и 7.имеют преимущество по входам установки 0 и 1 относительно входа синхронизации. Запись коэффициента деления, т.е. начальные состояния триггеров счетчиков 3 и 7 задаются однозначно ко входам установки 0 и 1. Коэффициент деления вводится в счетчики 3 и 7 в прямом двоичном коде. Наименьший коэффициент деления равен 3, а наибольший (2 - 1).

Быстродействие делителя обеспечивается тем, что импульсы логических состояний вырабатываются с задержкой, равной одному переходу логического элемента из одного состояния в другое. Импульсы, воздействующие на блок 1 управления, вырабатываются в одном полутакте, а во втором полутакте вырабатывается импульс управления, который в первом полутакте следующего такта уже выполняет логическую операцию. Счетчик, работающий в коде Грея, за один такт изменяет состояние только одного триггера. Поэтому задержка импульса в двух разрядах счетчика в коде Грея для всех четырех состояний одинакова. Другим важным фактором является надежность работы делителя, которая обеспечивается селективностью работы узлов счетчика младших разрядов делителя и блока управления в течение периода деления. Это достигается текстированием и разбиением входной последовательности на циклы.

Формула изобретения

Делитель частоты с программируемым коэффициентом деления, содержащий блок управления, первый вход которого соединен с выходом блока опознавания, входы которого соединены с разрядными выходами счетчика старших разрядов, информаци- онные входы которого соединены с выходами первого блока записи кода, вход управления которого соединен с выходом блока управления, входом разрешения записи второго блока записи кода и выходной шиной, счетчик младших разрядов, информационные входы которого соединены с выходами второго блока записи, выход - со входом синхронизации счетчика старших разрядов, а разрядные выходы - со вторым и третьим входами блока управления, четвертый вход которого соединен с входной шиной, причем информационные входы

первого блока записи кода соединены с кодовыми шинами старших разрядов, отличающийся тем, что, с целью повышения быстродействия и надежности, в него введен преобразователь двоичного кода в код Грея, входы которого соединены с кодовыми шинами младших разрядов, а выходы - с информационными входами второго блока записи кода,- при этом счетчик младших разрядов выполнен двухразрядным счетчиком в коде Грея, вход синхронизации которого соединен с входной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1088136A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Устройство для вычисления скользящего среднего | 1985 |

|

SU1247895A2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и синтеза частот. Цель изобретения - повышение быстродействия и надежное и работы. Делитель частоты содержит блок 1 управления, блок 2 опознавания, счетчик 3 старших разрядов, первый и второй блоки 4 и 5 записи кода, выходную шину 6, счетчик 7 младших разрядов, входную шину 8, кодовые шины 9, 10 и 11 старших разрядов, преобразователь 12двоичного кода в код Грея, кодовые шины 13и 14 младших разрядов. 2 ил.

Фиг.1

Тс,

.Л

6Тсг

Тс,

Г Г Ъ

Т

ъ т2 73 ;;

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU668094A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1987-12-22—Подача