I I I

Гг I

12

tpue.i

: 31508

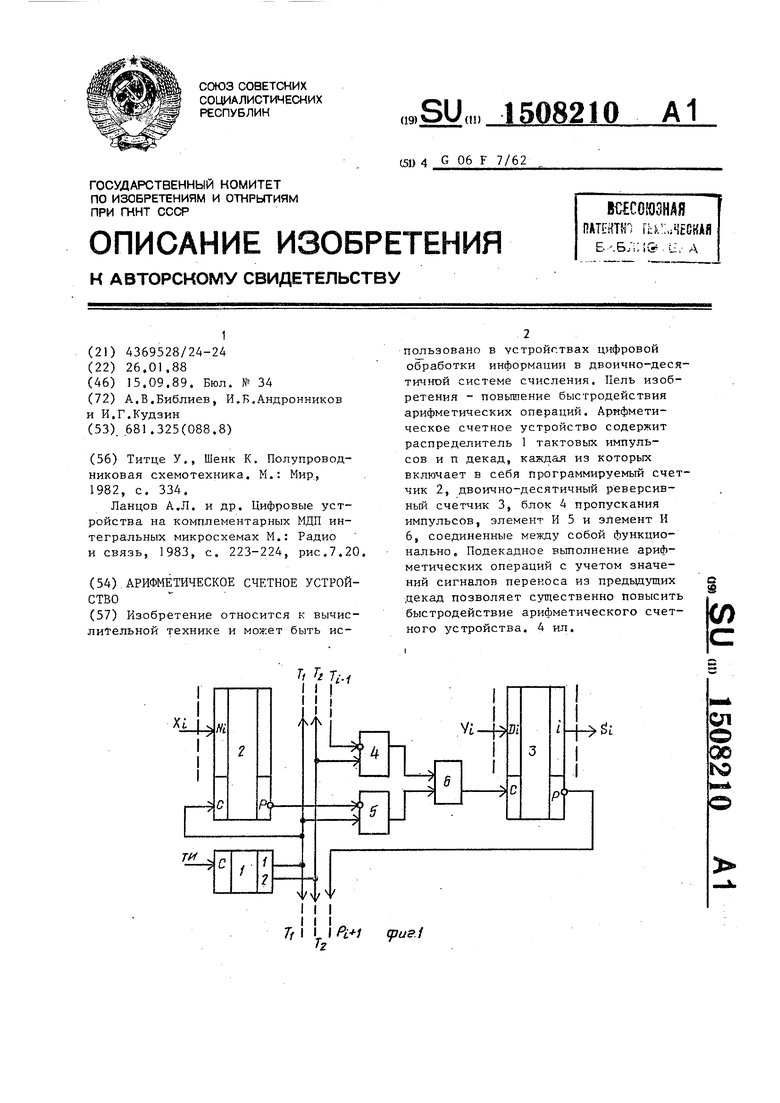

Изобретение относится к вычислительной технике и может быть, использовано в устройствах цифровой обра- ботки информации в двоично-десятич- иой системе счисления, ,

Цель изобретения - повышение быстродействия арифметических операций.

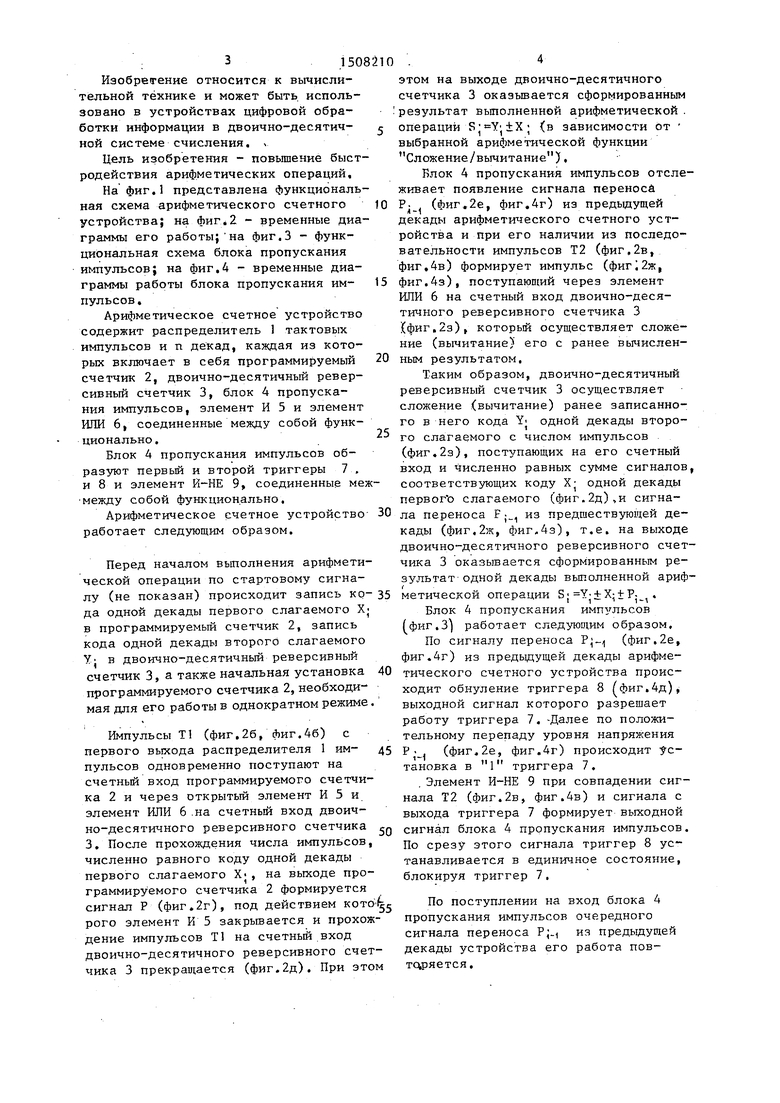

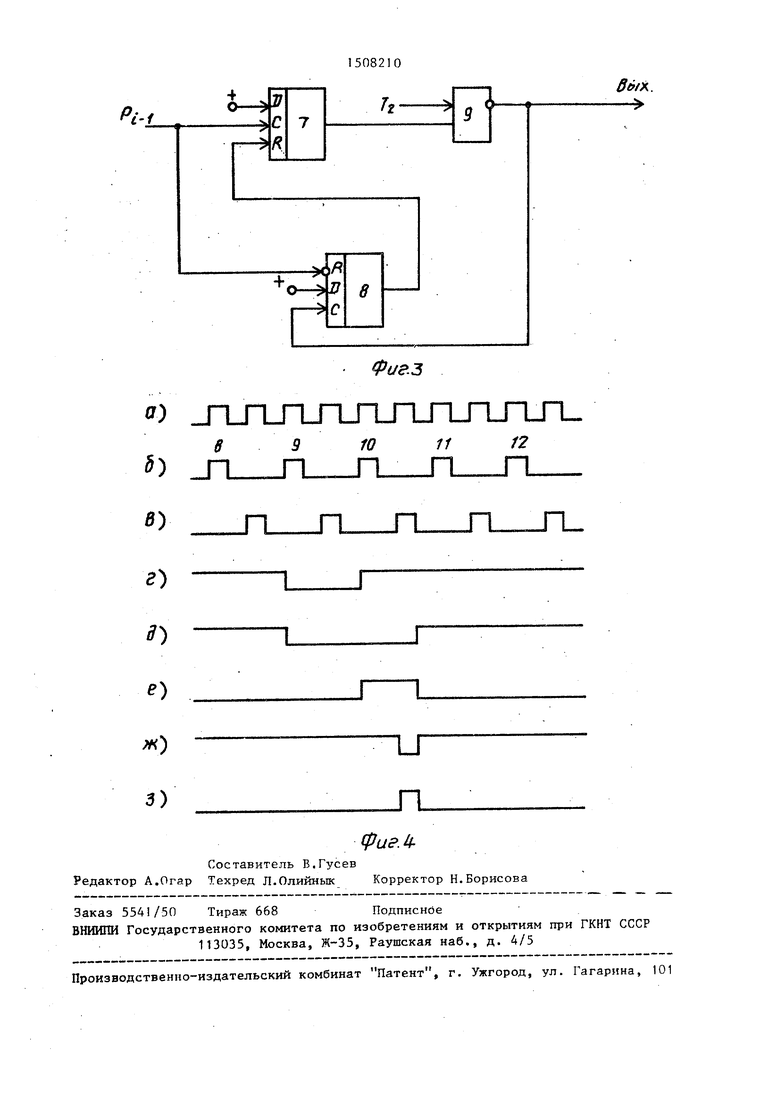

На фиг.1 представлена функциональная схема арифметического счетного устройства; на - временные диаграммы его работы; на фиг.З - функциональная схема блока пропускания импульсов; на фиг,4 - временные диаграммы работы блока пропускания им- пульсов.

Арифметическое счетное устройство содержит распределитель 1 тактовых импульсов и п декад, каждая из которых включает в себя программируемый счетчик 2, двоично-десятичный реверсивный счетчик 3, блок 4 пропускания импульсов, элемент И 5 и элемент ИЛИ 6, соединенные между собой функционально .Блок 4 пропускания импульсов образуют первьм и второй триггеры 7 . и 8 и элемент И-НЕ 9, соединенные меж между собой функционально.

Арифметическое счетное устройство работает следующим образом.

Перед началом выполнения арифметической операции по стартовому сигналу (не показан) происходит запись ко- да одной декады первого слагаемого Xj в программируемый счетчик 2, запись кода одной декады второго слагаемого Y в двоично-десятичный реверсивный счетчик 3, а также начальная установка программируемого счетчика 2, необходимая для его работы в однократном режиме

Импульсы Т1 (фиг,26, фиг.46) с первого вькода распределителя 1 им- пульсов одновременно поступают на счетный вход программируемого счетчика 2 и через открытый элемент И 5 и элемент ИЛИ 6 .на счетный вход двоично-десятичного реверсивного счетчика 3, После прохождения числа импульсов, численно равного коду одной декады первого слагаемого Х- , на выходе программируемого счетчика 2 формируется сигнал Р (фиг.2г), под действием кото рого элемент И 5 закрывается и прохождение импульсов Т1 на счетный.вход двоично-десятичного реверсивного счетчика 3 прекращается (фиг.2д). При это

этом на выходе двоично-десятичного счетчика 3 оказьшается сформированным результат выполненной арифметической операций ±Х ; (в зависимости от выбранной арифметической функции Сложение/вычитание),

Блок 4 пропускания импульсов отслеживает появление сигнала переноса Р (фиг.2е, фиг.4г) из предыдущей декады арифметического счетного устройства и при его наличии из последовательности импульсов Т2 (фиг,2в, фиг,4в) формирует импульс (фиг)2ж, фиг,4з), поступающий через элемент ИЛИ 6 на счетный вход двоично-десятичного реверсивного счетчика 3 (фиг,2з), который осуществляет сложение (вычитание) его с ранее вычисленным результатом.

Таким образом, двоично-десятичный реверсивный счетчик 3 осуществляет сложение (вычитание) ранее записанного в него кода Yj одной декады второго слагаемого с числом импульсов (фиг,2з), поступающих на его счетный вход и численно равных сумме сигналов соответствующих коду X одной декады первогЪ слагаемого (фиг.2д),и сигнала переноса Fj из предшествующей декады (фиг,2ж, фиг,4з), т.е, на выходе двоично-десятичного реверсивного счетчика 3 оказывается сформированным результат одной декады вьтолненной ариф {

метической операции Sj Y ±X;±P- ,

Блок 4 пропускания импульсов (фиг,3) работает след ующим образом.

По сигналу переноса Р;--,| (фиг,2е, фиг.4г) из предыдущей декады арифметического счетного устройства происходит обнуление триггера 8 /фиг,4д), выходной сигнал которого разрешает работу триггера 7, -Далее по положительному перепаду уровня напряжения Р,) (фиг.2е, фиг.4г) происходит установка в 1 триггера 7,

, Элемент И-НЕ 9 при совпадении сигнала Т2 (фиг.2в, фиг,4в) и сигнала с выхода триггера 7 формирует выходной сигнал блока 4 пропускания импульсов, По срезу этого сигнала триггер 8 устанавливается в единичное состояние, блокируя триггер 7,

По поступлении на вход блока 4 пропускания импульсов очередного сигнала переноса Р., из предыдущей декады устройства его работа пов- тодяется,

150

Таким образом, введение в ариф- метическое счетное устройство блока пропускания одиночных импульсов, блока сложения и распределителя импульсов позволяет проводить подекадное выполнение арифметических операций в двоично-десятичной системе счисления с учетом значений сигналов переноса из предыдущих декад, что при числе двоично-десятичных декад более трех дает возможность существенно повысить быстродействие арифметического счетного устройства, работающего в двоично-десятичной системе счисле- ния.

Формула изобретения

1, Арифметическое счетное устрой-- ство, содержащее вход тактовой частоты и п декад , где п - число декад входной информации, каждая из которых состоит из программируемого счетчика, установочные входы которого соединены соответственно с информационными входами i-й декады первого слагаемого устройства, где ,2,3,...,п, выход переноса программируемого счетчика соединен с первым входом элемента И, второй.вход которого соединен с счетным входом программируемого счетчика, и двоично-десятичного реверсивного счетчика, установочные входы которого соединены соответственно с информационными входами i-й декады второго слагаемого устройства, а разрядные выходы двоично-десятичного реверсивного счетчика являются информационными входами i-й декады устройства, отличающееся

5

0

0

О6

тем, что, с целью повышения быстродействия вьтолнения арифметических операций, в устройство введен распределитель тактовых импульсов, а в каждую из п декад устройства введены блок пропускания импульсов и элемент ИЛИ, причем выходы блока пропускания импульсов и элемента И соединены с . входами элемента lUlPi, выход которого соединен со: счетным входом двоично-десятичного реверсивного счетчика, управляющий вход блока пропускания и импульсов i-й декады соединен с выходом переноса двоично-десятичного реверсивного счетчика (i-l)-й декады, вход тактовых импульсов устройства соединен с входом распределителя импульсов, первый выход которого соединен с вторыми входами элементов И, а второй выход распределителя импульсов соединен с информационными входами блоков пропускания импульсов в каждой из п декад .устройства.

2, Устройство по п, 1, о т л и - чающееся тем, что блок пропускания импульсов содержит первый и второй триггеры и элемент К-НЕ, причем тактовый вход первого триггера соединен с входом установки в О второго триггера и является управляющим входом блока, выход перво1-о триггера соединен с первым входом эле- элемента , второй вход которого является информационным входом блока, выход элемента И-НЕ соединен с выходом блока, и с тактовым входом i второго триггера, -выход которого сое- Q динен с входом установки в О первого триггера.

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое счетное устройство | 1989 |

|

SU1628063A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Отсчетное устройство | 1974 |

|

SU548858A1 |

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Рентгеноабсорционный анализатор серы в нефти и жидких нефтепродуктах | 1988 |

|

SU1689817A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки информации в двоично-десятичной системе счисления. Цель изобретения - повышение быстродействия арифметических операций. Арифметическое счетное устройство содержит распределитель 1 тактовых импульсов и N декад, каждая из которых включает в себя программируемый счетчик 2, двоично-десятичный реверсивный счетчик 3, блок 4 пропускания импульсов, элемент И 5 и элемент И 6, соединенные между собой функционально. Подекадное выполнение арифметических операций с учетом значений сигналов переноса из предыдущих декад позволяет существенно повысить быстродействие арифметического счетного устройства. 4 ил.

О JOTTJlJnjnjnJlJlJTJnj-LrLrL

ж

JT

,

t-.2

R

o-

nJTJTJnJ TinJTJlJl-.

12

П

Л.

5

n

r

n

//

n

6)

IT

n

ж)

3)

Составитель Б.Гусев Редактор А.Огар Техред Л.Олийнык Корректор Н.Борисова

Заказ 5541/50 Тираж 668Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

h

.

-

Фиг.З

r

n

//

n

nTL

FL

и

n

игЛ

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| Способ искусственного получения акустического резонанса | 1922 |

|

SU334A1 |

| Ланцов А,Л | |||

| и др | |||

| Цифровые устройства на комплементарных МДП интегральных микросхемах М.: Радио и связь, 1983, с | |||

| Способ исправления пайкой сломанных алюминиевых предметов | 1921 |

|

SU223A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-26—Подача