Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей. . Известен преобразователь двоичного кода в двоично-десятичный код градусов, минут и секунд, содержащий входной регистр, генератор импульсов, двоичный счетчик, элемент И, дешифраторы, блок элементов И, блок элементов ИЛИ и группу двоично-десятичных счетчиков l Недостаток известного преобразователя состоит в его относительно низком быстродействии. Наиболее близким решением к изобретению по технической сущности, и схемному решению является преобразователь двоичного кода в двоично-десятичный масштабированный код, содержащий вход- ной регистр, информационные входы которого соединены с входами преобразователя. In двоично-десятичных счетчиков, где Ум - число тетрад выходного кода. Уу элементов ИЛИ, (УЯ-1) элементов задержзси, распределитель импульсов, генератор импульсов, элемент И, первый вход которого соединен с выходом генератора импульсов, а выход - с тактовым входом распределителя импульсов, А1 групп элементов И, первые входы которых соединены с выходами входного регистра, вторые входы - с группой выходов распределителя импульсов, а выходы элементов И группы - со входами соответствуюших элементов ИЛИ; выход Л-го (l 1-Mi) элемента ИЛИ связан со счетным входом 4 -fo двоично-десятичного счетчика, выход переполнения которого через -i -и элемент задержки соединен с входом (i+l)-ro элемента ИЛИ. Кроме того, этот преобразователь содержит шифратор эквивалентов и десятичный счетчик 12.. Недоста -ок этого преобразователя заключается в его относительно низком быстродействии. Целью изобретения является повышениз быстродействия.

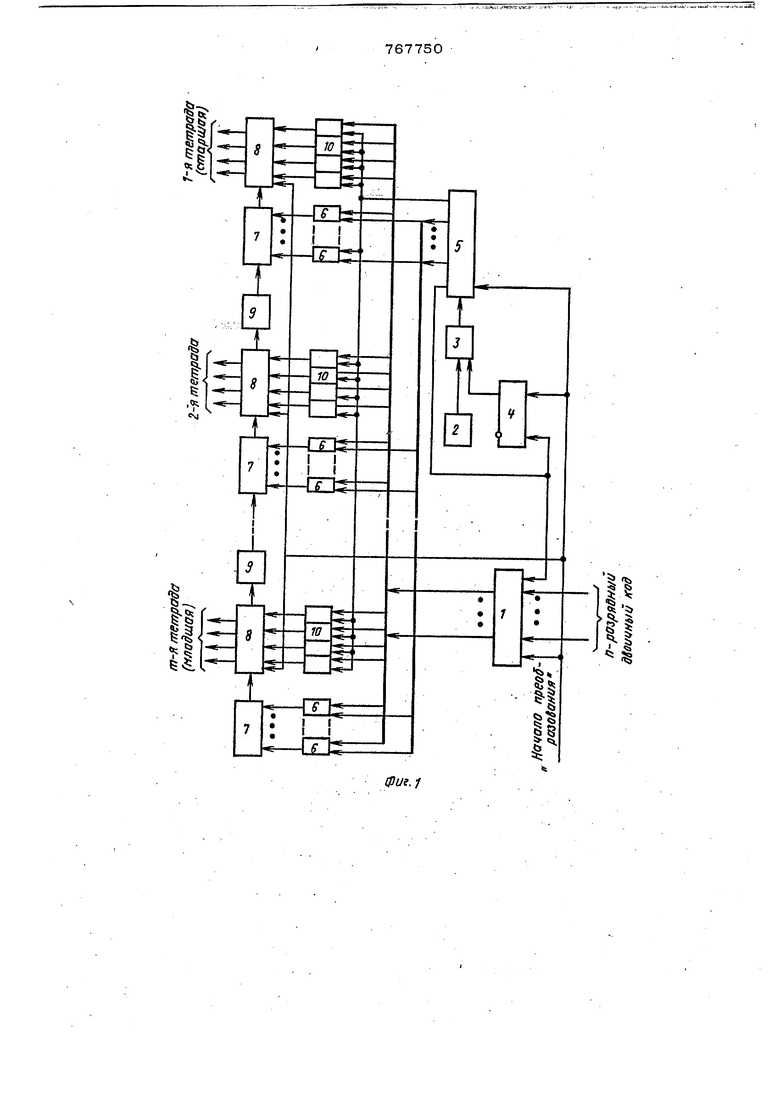

Поставленная цель досгигается за счет того, что в преобразователь цвоичного кода в двоично-десятичный масшта-. бированный код, содержащий входной регистр, информационные входы которого соединены с входами преобразователя, УУ цвоично-десятичных счетчиков, где W - число тетрад выходного кода, Vvi элементов ИЛИ, (Vvi-1) элементов задержки, распределитель импульсов, генератор импульсов, элемент И, первый вход которого соединен с выходом генератора импульсов, а выход - с тактовым входом распределителя импульсов, Wi групп элементов И, первые входы которых соединены с выходами входного регистра, вто«вые входы - с группой, выходов распределителя импульсов, а выходы элементов И группы - со входами соответствующих элементов ИЛИ, выход 1-го (1 1- элемента ИЛИ соединен со счётным входом. л -го двоично-дбсят гчного счетчика, выход переполнения которого через 1 -и элемент задержки связан с входом (1+1)-го элемента ИЛИ, дополнительно вютючены триггер управления и Vv дополнительных групп элементов И, первые вкоды которых соединены с первым выходом распределителя импульсов, вторые входы - с соответствующими выходами входного регистра, а выходы элементов И дополнительных групп подключены к установочным входам соответствующих двоично-десятичных счетчиков. Второй выход распределителя импульсов соединен со входом установки в нуль входного-регистра и со входом установки в нуль триггера управления,- единичный выход которого соединен со вторьпч входом элемента И, вход триггера управления - с входом запуска распределителя импульсов и управляющим входом преобразователя, входом записи входного регистра и входами сброса двоичнодесятичных- счетчиков. . На фиг. 1 изображена структурная схема предложенного преобразователя; на . фиг. 2, . а-о и фиг. 3, а,б представлены -временные диаграммы, поясняющие его работу.

Преобразователь содержит входной регистр 1, входами подютюченный к входам .преобразователя, генератор 2 импульсов, соединённый к первому ;входу элемента И 3, к второму входу которого подключен триггер 4 управления. Единичный ;. триггера 4 управления соединеи со BKOjfOM распределителя 5 тпугпульсОв, вхоч дом записи входного регистра 1, а neg-677504

вый вход триггера 4 управления подключен ко входу входного регистра 1 и выходу распределителя 5 импульсов, группа выходов которого соединена с первыми

5 входами МП групп элементов И 6, вторые входы которых подключены к соответствующим разрядам входного регистра 1. Выходы щ групп элементов И 6 подключены к первым входам pvi элементов ИЛИ

(О 7, которые выходами соединены с входами Wi двоично-десятичных счетчиков 8, а вторыми входами - с выходами (уц-1) элементов 9 задержки во всех тетрадах, кроме младшей; уу, вторых групп элемен 5 тов И 10 первыми входами подключены к соответствующим разрядам входного регистра 1, вторыми входами - к выходу распределителя 5 импульсов, а выходами - к установочным входам уи двоично20 десятичных счетчиков 8. Единичный вход триггера 4 управления, кроме того, соединен со входом сброса двоично-десятичных счетчиков и с управлжощим входом преобразователя..25 Преобразователь работает следующим образом.

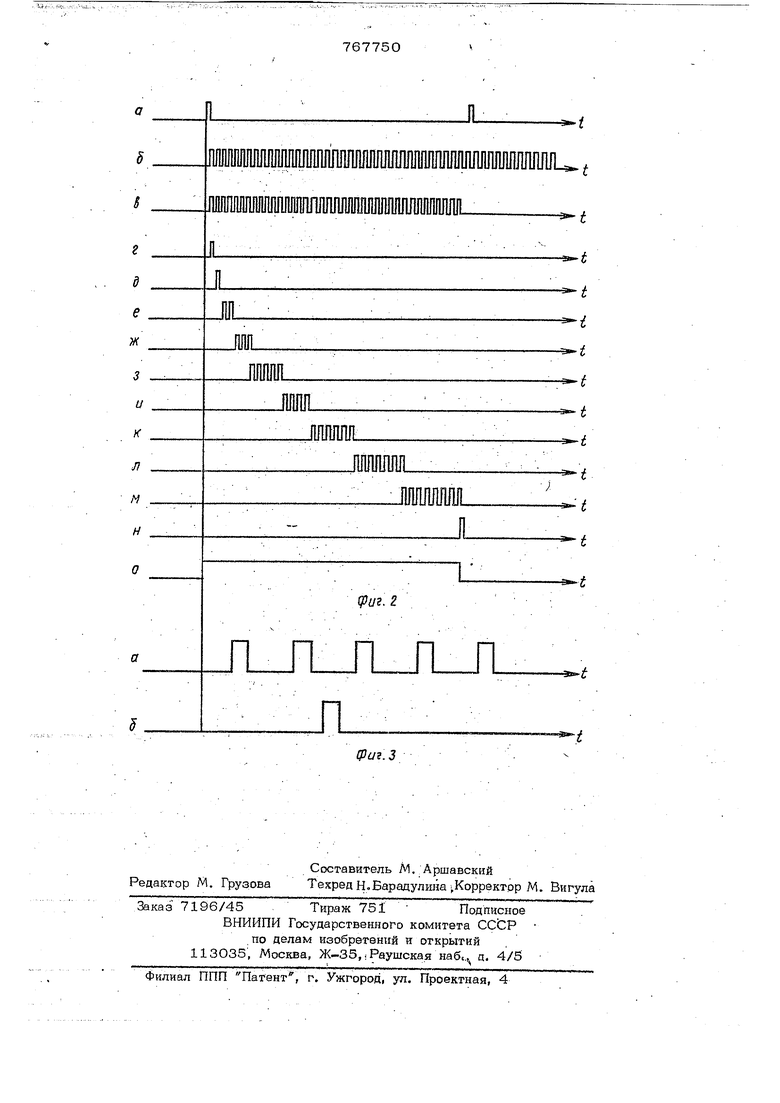

По сигналу на управляющем входе преобразователя (см. фиг. 1 и фиг. 2,а)

30 информация с информационных входов записывается во входной регистр 1. Этим же сигналом устанавливаются в исходное положение двоично-десятичные счетчики 8 и распределитель 5 импульсов, уста35 навлнвается в единичное состояние

триггер 4 управления (см. фиг. 2, о), . который разрешает прохождение импульсов для генератора 2 тактовых импульсов (см. фиг. 2,6) через элемент И 3

40 (см. фиг. 2,в) в распределитель 5 им пульсоЕ1.

Далее работа преобразователя осущест вляется в два этапа.. В течение первого

этапа с первого выхода распределителя 45 5 импульсов выдается один импульс, с помощью которого осуществляется запись кодов, соответствующих определенным разрядам входного регистра 1 (соответствие кодов разрядами входного регистJQ ра 1 будет пояснено на примерах 1 и 2), через группы элеменгой И 10 в hi двоично-десятичные счетчики 8 (коды, не требующие сигналов переноса при суммировании, например: 0101+0010,ОНО + О01 и т. д.). - Таким образом, часть информации из двоииюго кода на входном регистре 1 преобразуете. Б двоично-десятичный масштабированный код преобразуемого

числа. На этом заканчивается первый атап преобразования.

В течение второго этапа из распределителя 5 импульсов на первые входы Wi групп элементов И 6 поступают сфор- мированные пакеты из 1,2,3 . . .или 9 импульсов (см. фиг. 2, м-д). На вторые входы УК групп элементов И 6 поступает информация с соответствующих разрядов входного регистра 1 (соответствие разрядов входного регистра 1 определенным пакетам будет пояснено на примерах 1 и 2). В зависимости от того, какие из разрядов входного,регистра 1 находятся в единичном сйстоянин, срабатывают те или иные элементы И 6 группы и соответствующие им пакеты (-СМ. фиг. 2, д-и) через элементы ИЛИ 7 поступают на счетные входы Уи двоично-десятичных счетчиков 8, суммируясь с информацией, записанной в wi двоичнодесятичных счетчиках в результате первого этапа преобразования.

Если в результате считывания очередного пакета, импульсов на втором этапе преобразования возникают сигналы переноса , в следующий счетчик, то для правильного счета импульсов в следующей тетраде сигнал переноса задерживается на. одной из (Vvbl) элементов 9 задержки таким образом (см. фиг. 3,6), чтобы он укладвшался между импульсами ; (см. фиг. 3,а). По завершении цикласо второго выхода распределителя 5 импуль- сов поступает импульс, который устанавливает в нулевое состояние .триггер 4 управления и входной регистр 1 останавливая таким образом работу преобразователя. На этом заканчивается второй этап преобразования.- - . .

За один цикл распределителя 5 импуль сов в результате двух этапов преобразования в УИ двоично-десятичных счетчиках 8 сформируется искомый двоично-дёсятичный код, который поступает на выходные тины преобразователя. Следующим импул сом Начало преобразования устанавливаются в исходное состояние всё Vn двоично-десятичных счетчиков 8, распределитель 5 импульсов, во входной регист з 1 записывается новое двоичное число, триггер 4 управления устанавливается в единичное Состояние и цикл повторяется.

Длительность цикла распределителя 5 импульсов определяет быстродействие

преобразователя, которое может быть определено по следующей формуле: ..

4-V (.q, VQ,P2-... а где t рр - время преобразования;

первое слагаемое - длительность первого этапа преобразования, второе слагаемое - длительность второго этапа преобразования;

t|- - длительность периода импульсов тактового генератора; Q-i - количество пакетов, содержащих j - импульсов; р- - пакет из j импульсов, поступающих по одному из выходов распределителя 5 импульсов;

j - 1,2 ... 9.

Точность преобразования определяется разрядностью (И ) входного двоичного . кода и количеством двоично-десятичных счетчиков (Ул) с учетом (lifVY -йИ).

Пример 1. В таблице 1 показано соответствие разрядов входного регисра 1 кодам, записываемым в Vvi двоичнодесятичные счетчики через Уп групп элементов И 1О, в результате первого этапа преобразования (коды подчеркнуты) и через Уу1 групп элементов И б - в результате второго этапа, преобразования (неподчеркнутые коды) Для слуная Н-«-100,И - 15, 4, где И- десятичное число, в которое преобразуется двоичный код; и - разрядность двоичного кода; - число тетрад выходного кода; В- - вес соответствующего i -го разряда двоичного кода, определяется следующим выражением: . :-

D- oh-l

iCi-) - 2 ,

где Vi - число двоичных разрядов; -t-n -и двоичный разряд при (1,2 . . , . . И ), где - старший разряд; Vl - младший разряд, В вес десятичного числа N , соответствующего 1 двоичному разряду, определяется следующим выраже- . нием:-Л.

i(10) 2i

Br- представление кода тетрады в десятичной системе счисления; В ,..- представление кода тетрады в двоичной система счисления. Коэффициенты а определяются из таблицы 1 следующим образом. .

Сначала из табл. 1 выбираются значения, которые преобразуются в двоичнодесятичный, код числа N в результате первого этапа преобразования, т. е. непосредственным занесением на Ум двоично7 7677598

десятичные счетчики 8 через группы эле-i, (например, в четвертой тетраде две

ментов И 10. Это коды, не треб5тощиепятерки), то коэффициент а «к

переносов при суммировании ( в табл. 1(а З). Если ни в одном из столбцов

они подчеркнуты).(10) ® ФР- Равных ;j, то а «,0 (ни

Затем из значений, не попавши;;: в одном из столбцов нет четверок,

вый этап, определяются коэффициентыт. е. а О).

ал для второго этапа преобразования..Из приведенного примера (см. табл.1

Если котя бы в одном столбе. , ,и фиг. 2, д-м) получим а «1; а s: 1;

соответствующем определенной тетраде, а, а 1; а. - О; ag а 2; а/ О; а- si;

имеется к - одинаковых цифр, равных о о 1; а ««1.

I . .Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1975 |

|

SU720424A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1974 |

|

SU603985A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1974 |

|

SU549801A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU842784A1 |

Таким образом, из приведенного при-, мера следуе.т, что распределитель импульсов должен сформировать следующие сигналы: один импульс для первого этапа преобразования (см, фиг. 2, г); пакеты импульсов для второго этапа преобразования в .составе (см. фиг. 2, д-м); по

одному импульсу - 1 пакет, по два 1, по три - 1, по пять - 2, по семь -1, по восемь - 1, по девять -т1.

Пример 2. В табл. 2 показанЬ соответствие разрядов входного регистра 1 двоично-десятичному коду числа N 6,2832 (2Ю ;иа16)Ы 5.

Коэффициенты а для примера 2 следующие: а2, «2; а,2; U-2; .

Использование изобретения по сравнению с существующими дает следующие ; преимущества: возможность индикации измеряемых параметров в различных единицах измерения (например, в %, градусах, радианах, в натуральных единицах и др.); получить достаточное быстродействие преобразователя при незначитель- ных затратах оборудованля.

Время преобразования заявляемого преобразователя для приведенного примера 1 (N-100, , VI s:13, мкс) равно tj,,l + 1 (1,1 + 1.2 + 1.3 + + 0,4 + 2,5 + 0,6,+ 1,7 + 1. 8 + 1.9); 42 МКС.

Время преобразования преобразователя 2 определяется по формуле

tnp-09 -bf.-Vl:qHH:5:l-17N KC.

Таким образом, видно, что быстродействие заявляемого устройства выше, чем у известного, в 2,8 раз,

Ф о р м у л а и 3 о б ре те ни я

Преобразователь рвоичного кода в двоично-десятичный масштабированный код, содержащий входной регистр, инфор-, мационные входы которого соединены с входами преобразователя, ки двоичнодесятичных счетчикой, где кц -число тетрад выходного кода, hi элементов .ИЛИ, (Vfl-l) элементов задержки, распределитель импульсов, генератор импульсов, элемент И, первый вход которого соединен с выходом генератора импульсов, а выход - с тактовым входом распределителя импульсов, УМ групп элементов И, . первые входы которых соединены с выходами входного регистра, вторые входы -с группой выходов распределителя импульсов, а выходы элементов И груп-/ пы соединены со входами соответствующих элементов ИЛИ, выход -i -го () элемента ИЛИ соединен со счетным входом 4 -го двоично-десятичного счетчика, выход переполнения которого через i -и элемент задерноси соединен

с входом (4+1) -го элемента ИЛИ, отличающийся тем, что, с целью увеличения быстродействия, в него введен триггер управления и уи допол5 нительных групп элементов И, первые входы которых соединены с первым выходом распределителя импульсов, вторые входы соединены с соотвётствуюшсми . выходами входного регистра, а выходы 10 элементов И дополнительных групп соединены с установочными входами соответствующих двоично-десятичных счетчиков, второй выход распределителя импульсов соединен со входом установки 3 в нуль входного регистра и со входом установки в нуль триггера управления, единичный выход которого соединен со вторым входом элемента И, единичный вход триггера управления соединен с 0 входом запуска распределителя импульсов и управляющим входом преобразователя.,;.. , ....

Источники информации, : принятые во внимание при экспертизе 5- 1. Авторское свидетельство СССР № 521-564, кл. Q 06 F ,5/02, 1976.:

JUUUlll

a

t

.t

Авторы

Даты

1980-09-30—Публикация

1978-12-20—Подача