Фиг.1

Изобретение относится к вычислительной технике и может быть использовано и устройствах обработки информации в двоично-десятичной системе счисления.

Цель изобретения - повышение надежности работы стройства.

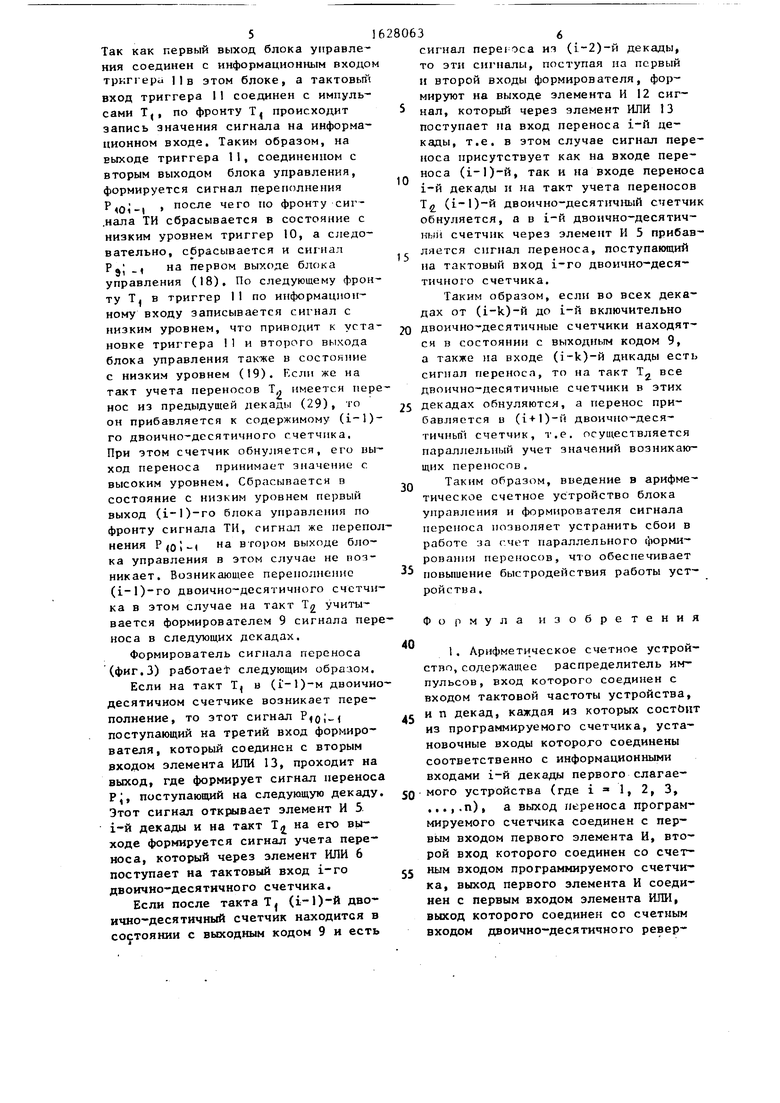

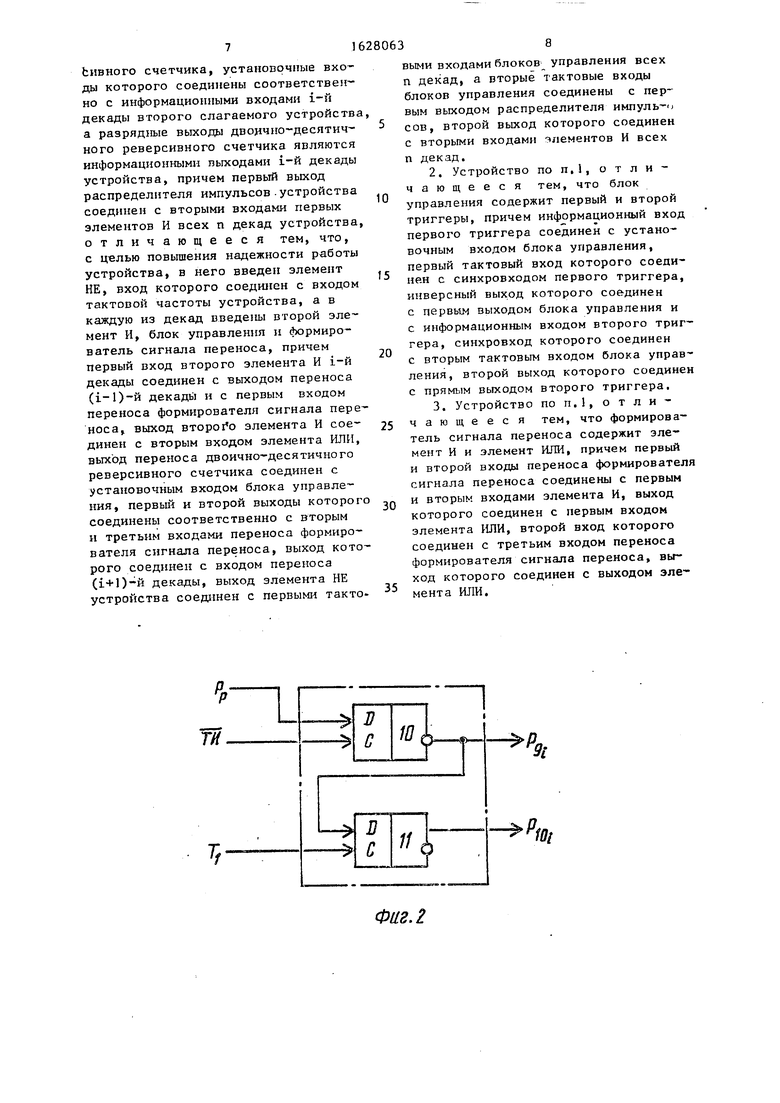

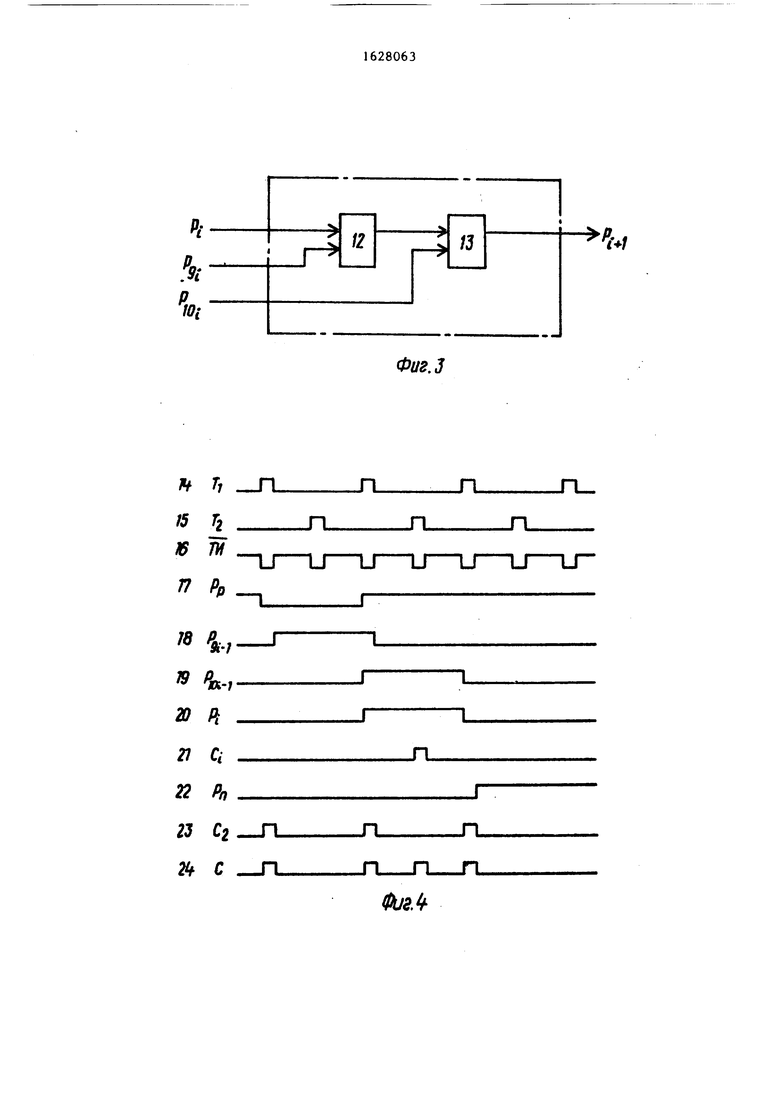

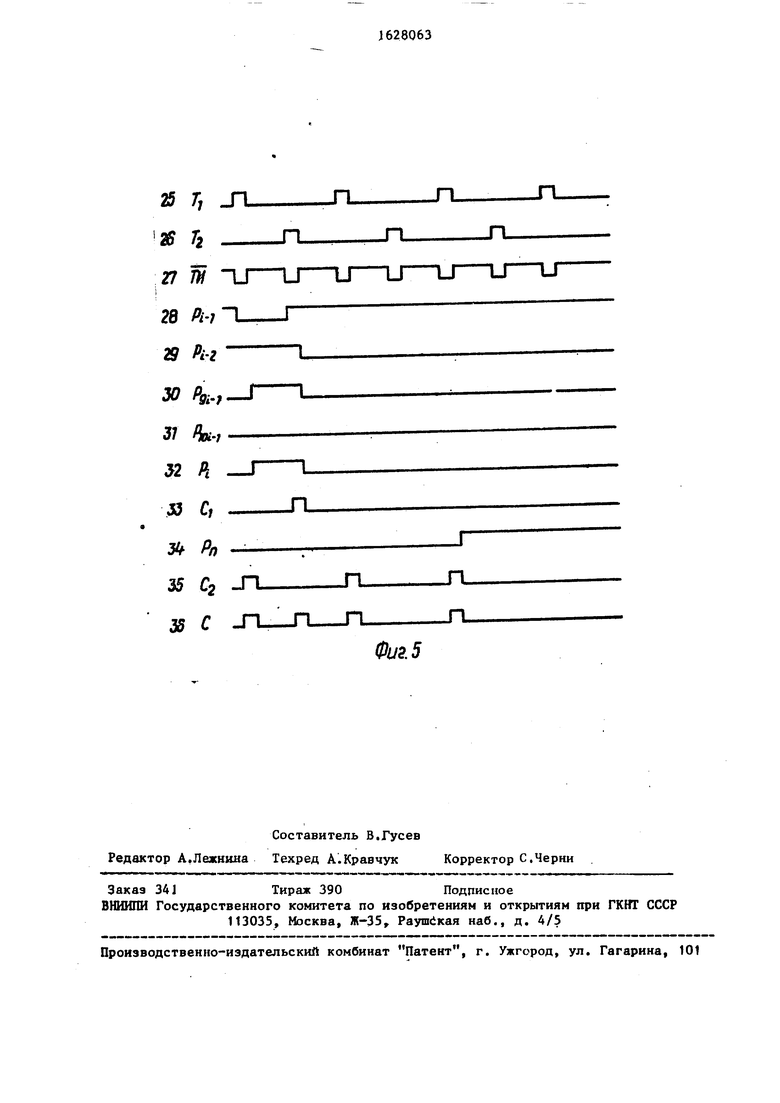

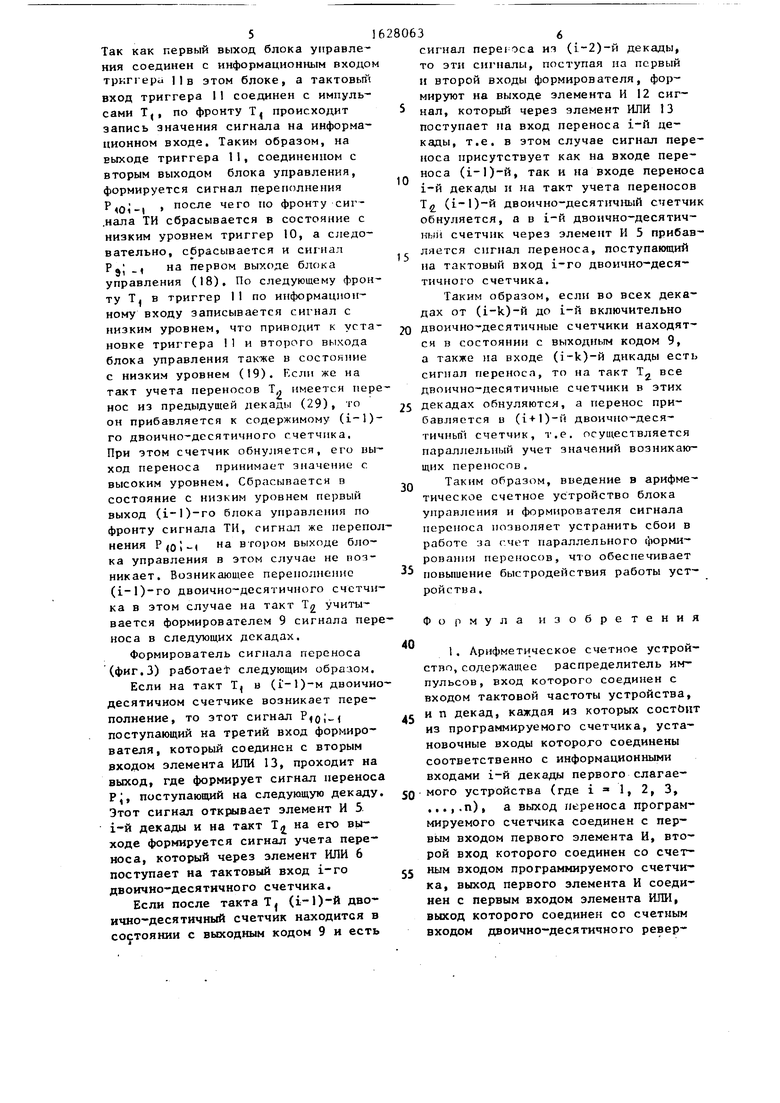

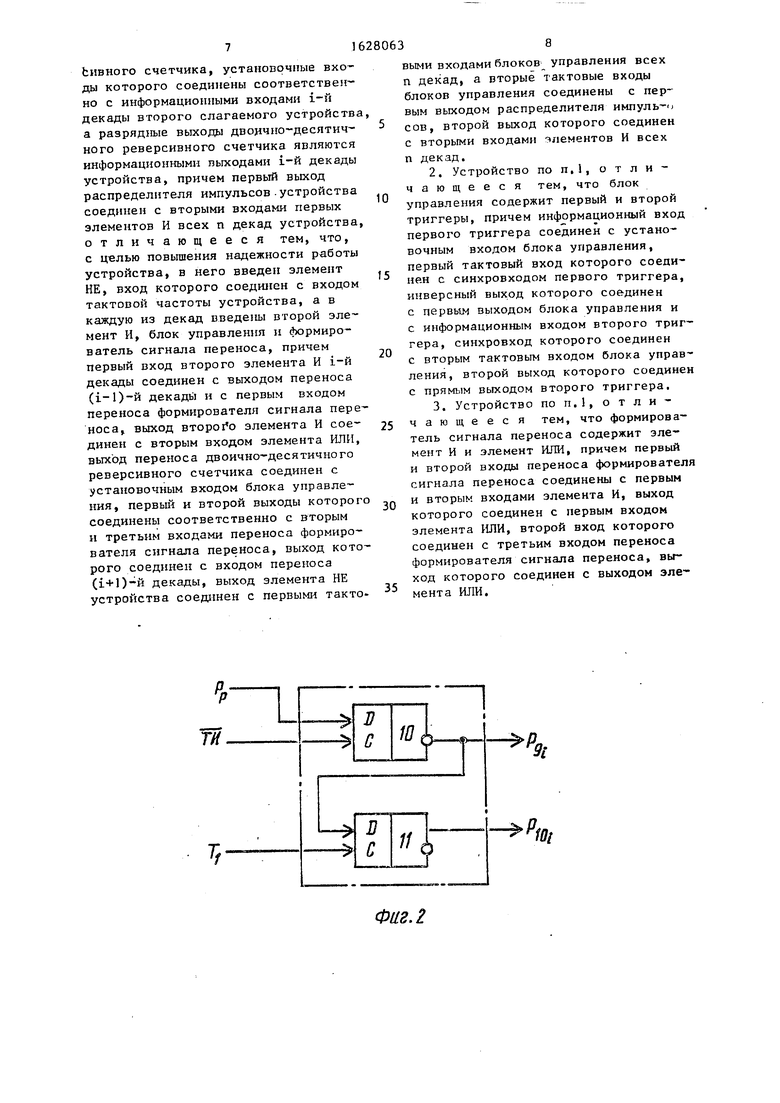

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема формирователя сигнала переноса; на фиг.А и 5 - временные диаграммы работы устройства.

Арифметическое счетное устройство содержит распределитель 1 импульсов программируемый счетчик 2, двоично- десятичный реверсивный счетчик 3, элементы И 4 и 5, элемент ИЛИ 6, элемент НЕ 7, блок 8 управления и формирователь 9 сигнала переноса, соединенные между собой функционально.

Блок 8 управления включает первый и второй триггеры 10 и 11, соединенные между собой функционально.

Формирователь 9 сигнала переноса выполнен на элементе И 12 и элементе ИЛИ 13, соединенных между собой функ цнонально.

На фиг.А и 5 обозначены сигналы 1А-36.

Арифметическое счетное устройство работает следующим образом.

Перед началом выполнения арифметической операции по стартовому сигналу (не показан) происходят запись кода одной декады первого слагаемого XJ в программируемый счетчик 2, за- пись кода одной декады второго слагаемого У - в двоично-десятичный счетчик 3, а также начальная установка программируемого счетчика 2, необходимая для его работы в однократном режиме.

Импульсы I (1А и 25) с первого выхода распределителя 1 импульсов одновременно поступают на счетный вход программируемого счетчика 2 и через элемент И А и элемент ИЛИ 6 на тактовый вход двоично-десятичного счетчика 3. После прохождения числа импульсов, численно равного коду одной декады первого слагаемого Х, на выходе программируемого счетчика 2 формируется сигнал Рп (22 и ЗА), под действием которого элемент И А закрывается, и прохождение импупьсов

JQ jj

0

5

Q

40 Д5

35

0

5

t на тактовый вход двоично-десятичного счетчика 3 прекращается. При этом на выходе двоично-десятичного счетчика 3 оказывается сформированным результат выполненной арифметической операции S У J i X j в зависимости от выбранной арифметической операции - сложение (вычитание). Элемент И 5 отслеживает появление сигнала переноса PJ (20) из предыдущей декады арифметического счетного устройства и при его наличии из последовательности импульсов Т 2. (15 и 26) формирует импульс С (21 и 33), поступающий через элемент ИЛИ 6 на тактовый вход двоично-десятичного счетчика 3, который производит сложение (вычитание) его с ранее вычисленным результатом.

Таким образом, двоично-десятичный счетчик 3 производит сложение (вычита ние) ранее записанного в него кода У{ одной декады второго слагаемого с числом импульсов (2А и 36), численно равным сумме сигналов, соответствующих коду X J одной декады первого слагаемого (23 и 35), и сигнала переноса Pj из предшествующей декады (21 и 38), т.е. на выходе двоично- десятичного счетчика 3 оказывается сформированным результат выполненной арифметической операции для одной декады s ; У; ± х; ± Р- .

Блок управления (фиг.2) работает следующим образом.

При достижении двоично-десятичным счетчиком некоторой декады состояния с выходным кодом 9 его выход переноса принимает значение сигнала с низким уровнем (17 и 18). Этот сигнал поступает на информационный вход триггера 10 блока управления этой декады, после чего по положительному перепаду сигнала ТИ (16 и 27), поступающему на тактовый вход триггера 10, происходит запись сигнала на информационном входе триггера 10, на инверсном выходе которого, соединенном с первым выходом блока управления, формируется сигнал (18 и 30). Далееj если на такт учета переносов Тг в рассматриваемой декаде не производилось суммирование переноса из предшествующей декады, по фронту сигнала двоично- десятичный счетчик переполняется и выход переноса этбго счетчика принимает значение высокого уровня (17).

Так как первый выход блока управления соединен с информационным входо триггера 1|в этом блоке, а тактовый вход триггера 11 соединен с импульсами Т,, по фронту Т i происходит запись значения сигнала на информационном входе. Таким образом, на выходе триггера 11, соединенном с вторым выходом блока управления, формируется сигнал переполнения

4O1-I

после чего по фронту сиг

.нала ТИ сбрасывается в состояние с низким уровнем триггер 10, а следовательно, сбрасывается и сигнал Pjj , на первом выходе блока управления (18), По следующему фронту Т в триггер II по информационному входу записывается сигнал с низким уровнем, что приводит к установке триггера 1 и второго выхода блока управления также в состояние с низким уровнем (19). Если же на такт учета переносов Т имеется перенос из предыдущей декады (29), то он прибавляется к содержимому (i-1)- го двоично-десятичного счетчика. При этом счетчик обнуляется, его БЫ- ход переноса принимает значение с высоким уровнем. Сбрасывается в состояние с низким уровнем первый выход (i-l)-ro блока управления по фронту сигнала ТИ, сигнал же переполнения PIQ,, на втором выходе блока управления в этом случае не поз- никает. Возникающее переполнение (i-l)-ro двоично-десятичного счетчика в этом случае на такт Т учитывается формирователем 9 сигнала переноса в следующих декадах.

Формирователь сигнала переноса (фиг.З) работает следующим образом.

Если на такт Т, в (1-1)-м двоично десятичном счетчике возникает переполнение, то этот сигнал P«oi-i поступающий на третий вход формирователя, который соединен с вторым входом элемента ИЛИ 13, проходит на выход, где формирует сигнал переноса Р;, поступающий на следующую декаду. Этот сигнал открывает элемент И 5 i-й декады и на такт Т на его выходе формируется сигнал учета переноса, который через элемент ИЛИ 6 поступает на тактовый вход i-го двоично-десятичного счетчика.

Если после такта Т (1-1)-й двоично-десятичный счетчик находится в состоянии с выходным кодом 9 и есть

0

5

0

сигнал nepeioca из (1-2)-й декады, то эти сигналы, поступая на первый и второй входы формирователя, формируют на выходе элемента И 12 сигнал, который через элемент ИЛИ 13 поступает на вход переноса i-й декады, т.е. в этом случае сигнал переноса присутствует как на входе переноса (1-1)-й, так и на входе переноса i-й декады и на такт учета переносов Т (i-l)-fi двоично-десятичный спетчик обнуляется, а в i-й двоично-десятичный счетчик через элемент И 5 прибавляется сигнал переноса, поступающий на тактовый вход 1-го двоично-десятичного счетчика.

Таким образом, если во всех декадах от (i-k)-fl до i-й включительно

Q двоично-десятичные счетчики находятся в состоянии с выходным кодом 9, а также на входе (i-k)-fi днкады есть сигнал переноса, то на такт Тг все двоично-десятичные счетчики в этих

5 декадах обнуляются, а перенос прибавляется в (i-H)-ti двоично-десятичный счетчик, т.е. осуществляется параллельный учет значений возникающих переносов.

Таким образом, введение в арифметическое счетное устройство блока управления и формирователя сигнала переноса позволяет устранить сбои в работе за гчет параллельного формирования переносов, что обеспечивает повышение быстродействия работы устройства .

5

Формула изобретения

Q

0

1. Арифметическое счетное устройство, содержащее распределитель импульсов, вход которого соединен с входом тактовой частоты устройства, с и п декад, каждая из которых состоит из программируемого счетчика, установочные входы которого соединены соответственно с информационными входами i-й декады первого слагаемого устройства (где i 1, 2, 3, .,.,.п), а выход переноса программируемого счетчика соединен с первым входом первого элемента И, второй вход которого соединен со счетным входом программируемого счетчика, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен со счетным входом двоично-десятичного реверЬнвного счетчика, установочные входы которого соединены соответственно с информационными входами 1-й декады второго слагаемого устройств а разрядные выходы двоично-десятичного реверсивного счетчика являются информационными выходами 1-й декады устройства, причем первый выход распределителя импульсов.устройства соединен с вторыми входами первых элементов И всех п декад устройства отличающееся тем, что, с целью повышения надежности работы устройства, в него введен элемент НЕ, вход которого соединен с входом тактовой частоты устройства, а в каждую из декад введены второй элемент И, блок управления и формирователь сигнала переноса, причем первый вход второго элемента И 1-й декады соединен с выходом переноса (1-1)-й декады и с первым входом переноса формирователя сигнала переноса, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход переноса двоично-десятичного реверсивного счетчика соединен с установочным входом блока управления, первый и второй выходы которого соединены соответственно с вторым и третьим входами переноса формирователя сигнала переноса, выход которого соединен с входом переноса (1+1)-й декады, выход элемента НЕ устройства соединен с первыми такто0

5

0

5

0

5

выми входами блоков управления всех п декад, а вторые тактовые входы блоков управления соединены с первым выходом распределителя импуль-о сов, второй выход которого соединен с вторыми входами элементов И всех п декад.

2.Устройство по п,1, отличающееся тем, что блок управления содержит первый и второй триггеры, причем информационный вход первого триггера соединен с установочным входом блока управления, первый тактовый вход которого соединен с синхровходом первого триггера, инверсный выход которого соединен

с первым выходом блока управления и с информационным входом второго триггера, синхровход которого соединен с вторым тактовым входом блока управления, второй выход которого соединен с прямым выходом второго триггера.

3.Устройство по п.1, о т л и - чающееся тем, что формирователь сигнала переноса содержит элемент И и элемент ИЛИ, причем первый

и второй входы переноса формирователя сигнала переноса соединены с первым и вторым входами элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с третьим входом переноса формирователя сигнала переноса, выход которого соединен с выходом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое счетное устройство | 1988 |

|

SU1508210A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Двоично-десятичное арифметическое устройство | 1976 |

|

SU731436A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Распределитель импульсов | 1986 |

|

SU1370770A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

Изобретение относится к вычислительной технике и может быть ис//-И й П- дио ОЙиссЪЪШ пользовано в устройствах обработки информации в двоично-десятичной системе счиления. Цель изобретения - повышение надежности работы устройства. Арифметическое счетное устройство содержит распределитель 1 импульсов, программируемый счетчик 2, двоично-десятичный реверсивный счетчик 3, два элемента И 4, 5, элемент ИЛИ 6, элемент НЕ 7, блок 8 управления и формирователь 9 сигнала пере- носл,соединенные между собой функционально. Параллельное формирование переносов в устройстве позволяет устранить сбои в работе,,повышая его надежность. 2 з.п. ф-лы, 5 ил. S (Л 05 ьэ 00 о 05 00

Фаг. 2

TI П

15r2

КТИ

.,-г

9Рк.,

20Pi

21С

22Р«

23C2 JT

Фиг.З

JT

п

л

п.

п

п

п

-TL

ФигА

Рд„

fc-, Я С, Рд

Л.

| Ланцов А.Л | |||

| и др | |||

| Цифровые устройства на комплементарных МДП- интегральных микросхемах | |||

| М.: Радио и связь, 1983, а | |||

| Фотореле для аппарата, служащего для передачи на расстояние изображений | 1920 |

|

SU224A1 |

| Арифметическое счетное устройство | 1988 |

|

SU1508210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-15—Публикация

1989-01-02—Подача