С71

О

9° ю

СП

3150

Изобретение относится к вычислительной технике и мозкет быть исполь- зованр при построении надежных микропроцессорных систем,

Цель изобретения - повышение достоверности контроля.

На фиг.1 приведена схема устройства для контроля хода программ; на фиг,2 - схема блока формирования сигнатур;, на фиг.З - пример конкретного выполнения блока формирования сигнатур; на фиг.4 - схема формирователя контрольного кода; на - пример конкретного вьшолнения блока сумматоров по модулю два; на фиг.6 - схема алгоритма; на фиг,7 - таблица, поясняющая логику работы формирователя контрольного кода.

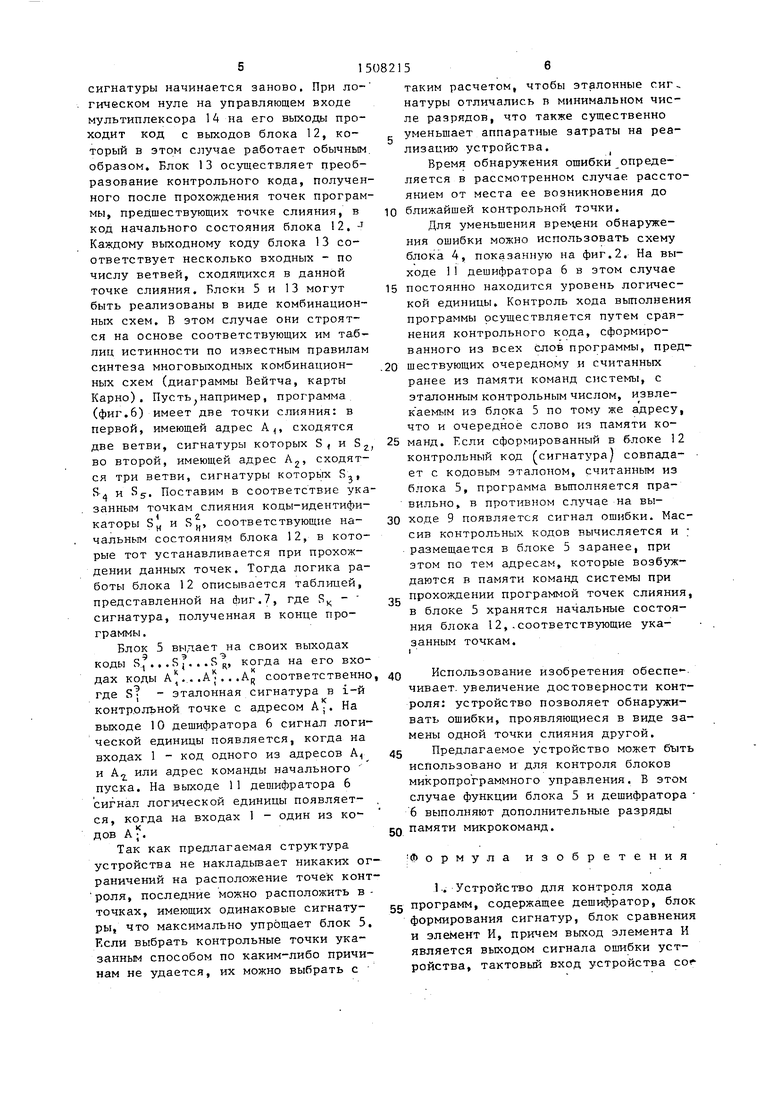

Устройство содержит (фиг.1) груп- пу адресных входов 1, группу инфор-. мационных входов 2, тактовый вход 3, блок 4 формирования сигнатур, блок 5 памяти, дешифратор 6, блок 7 сравнения, элемент И 8 и вьрсод 9 сигна- ла ошибки. Дешифратор 6 имеет пер- вьй 10 и второй 11, выходы.

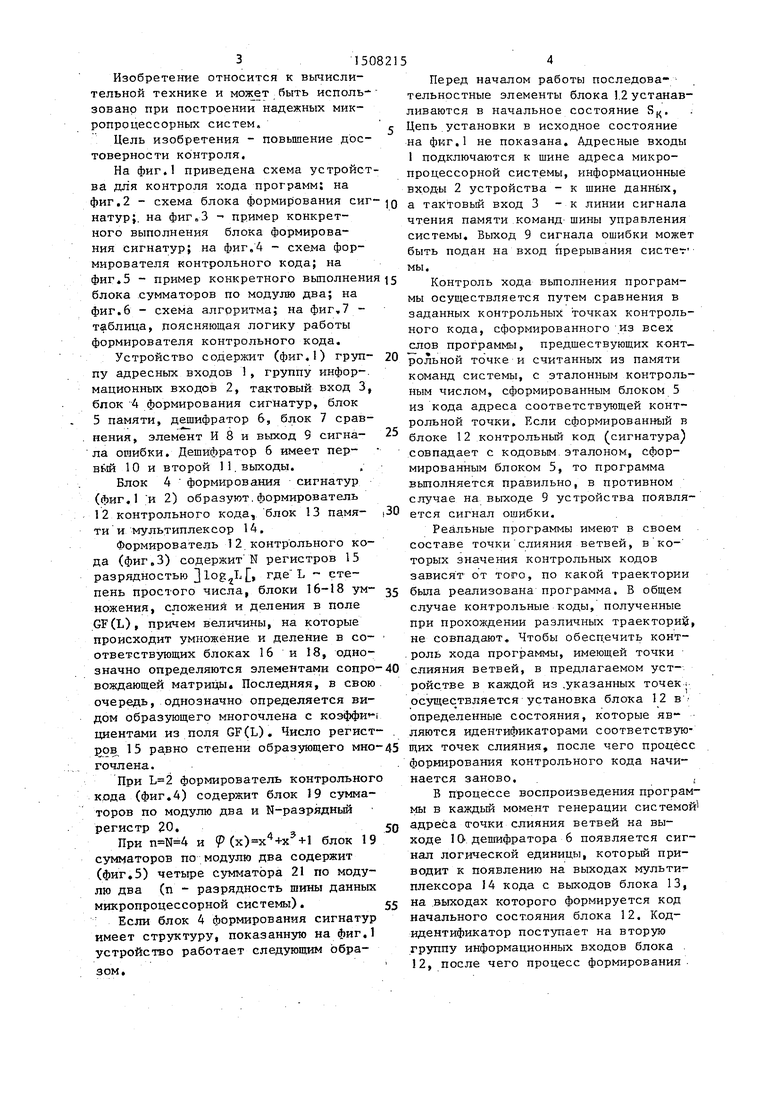

Блок 4 формирования сигнатур (фиг.1 и 2) образуют.формирователь 12 контрольного кода, блок 13 памя- ти и мультиплексор 14.

Формирователь 12 контрольного кода (фиг.З) содержит N регистров 15 разрядностью 3log,jI- где L - степень простого числа, блоки 16-18 ум- иожения, сложений и деления в поле GF(L), причем величины, на которые происходит умножение и деление в со- ответствующих блоках 16 и 18, однозначно определяются элементами сопровождающей матрицы. Последняя, в свою очередь, однозначно определяется видом образующего многочлена с козффи г циентами из поля GF(L). Число регист- gpB 15 ра.вно степени образующего многочлена.

При формирователь контрольного кода (фиг.4) содержит блок 19 сумматоров по модулю два и N-разрядный регистр 20.

При и 9 (х)х - -х +1 блок 19 сумматоров по модулю два содержит (фиг.З) четыре сумматора 21 по модулю два (п - разрядность шины данных микропроцессорной системы). : Если блок 4 формирования сигнатур имеет структуру, показаннзт на фиг.1 устройство работает следующим образом.

54

Перед началом работы последова- тельностные элементы блока 1.2 устанавливаются в начальное состояние S, Цепь установки в исходное состояние на фкг.1 не показана. Адресные входы 1 подключаются к шине адреса микропроцессорной системы, информационные входы 2 устройства - к шине данных, а тактовый вход 3 - к линии сигнала чтения памяти.команд- шины управления системы. Выход 9 сигнала ошибки может быть подан на вход прерывания систет мы.

Контроль хода выполнения программы осуществляется путем сравнения в заданных контрольных точках контрольного кода, сформированного из всех слов программы, предшествующих контрольной точке и считанных из памяти команд системы, с эталонным контрольным числом, сформированным блоком 5 из кода адреса соответствующей контрольной точки. Если сформированный в блоке 12 контрольньй код (сигнатура) совпадает с кодовым эталоном, сформированным блоком 5, то программа вьтолняется правильно, в противном случае на выходе 9 устройства появляется сигнал ошибки.

Реальные программы имеют в своем составе точки слияния ветвей, в ко- торых значения контрольных кодов зависят от тО Го, по какой траектории была реализована программа, В общем случае контрольные коды, полученные при прохождении различных траекторий не совпадают. Чтобы обесп.ечить конт- .роль хода программы, имеющей точки слияния ветвей, в предлагаемом устройстве в каждой из .указанных точек - осуществляется установка блока 12 в определенные состояния, которые яв- ляются идентификаторами соответствующих точек слияния, после чего процесс формирования контрольного кода начинается заново.

В процессе воспроизведения программы в каждый момент генерации системой адреса сточки слияния ветвей на выходе 10 дешифратора 6 появляется сигнал логической единицы, который приводит к появлению на выходах мультиплексора 14 кода с выходов блока 13, на выходах которого формируется код начального состояния блока 12. Код- идентификатор поступает на вторую группу информационных входов блока , 12, после чего процесс формирования

515082

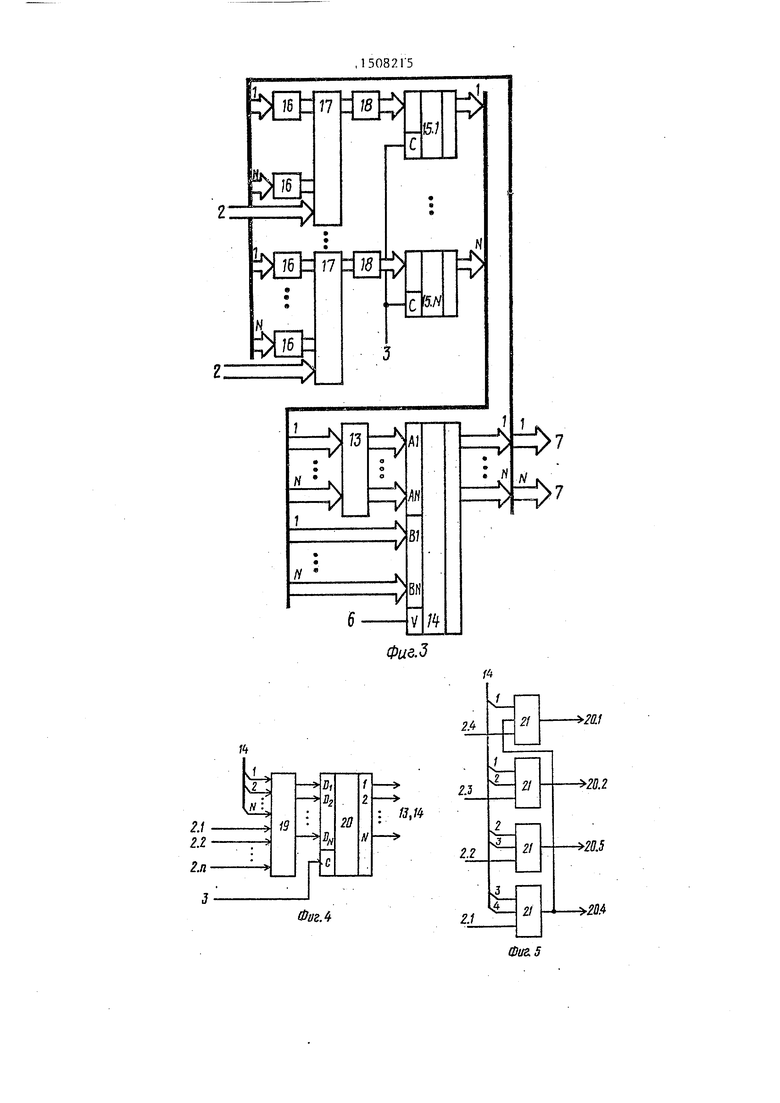

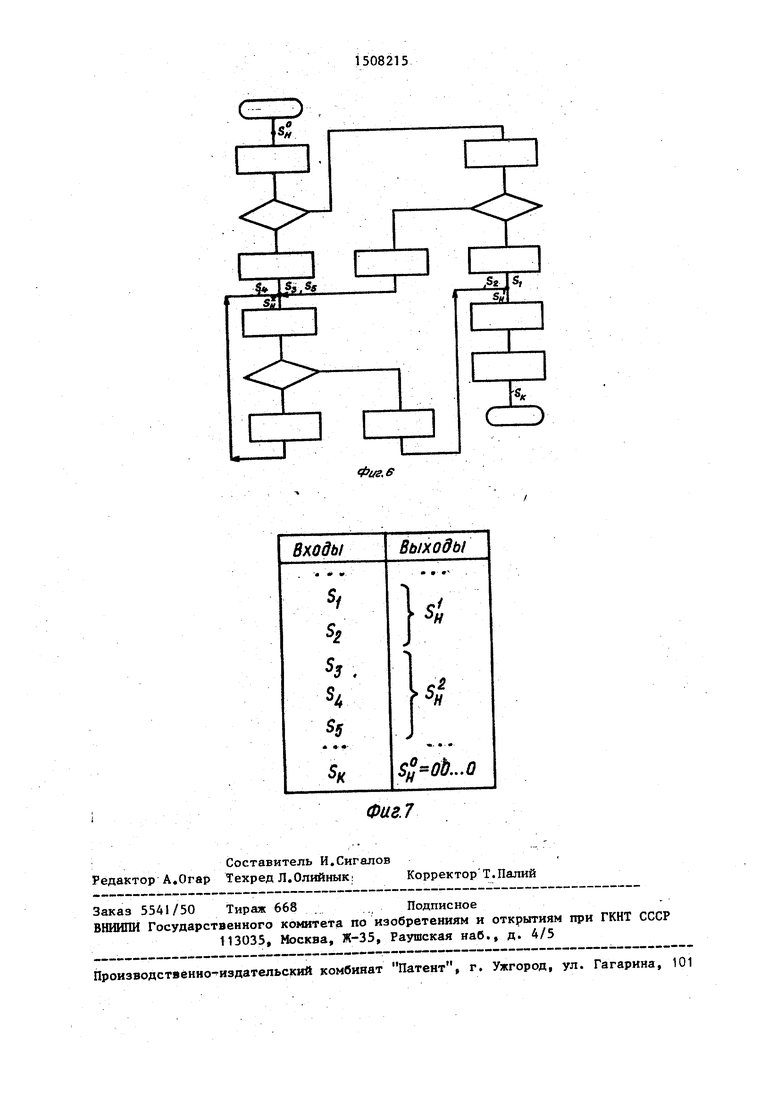

сигнатуры начинается заново. При ло- гическом нуле на управляющем входе мультиплексора 14 на его выходы проходит код с выходов блока 12, который в этом случае работает обычным, образом. Блок 13 осуществляет преобразование контрольного кода, полученного после прохождения точек программы, предшествующих точке слияния, в ю код начального состояния блока 12. - Каждому выходному коду блока 13 соответствует несколько входных - по числу ветвей, сходящихся в данной точке слияния. Блоки 5 и 13 могут 15 быть реализованы в виде комбинационных схем, Б этом случае они строятся на основе соответствующих им таблиц истинности по известным правилам синтеза многовыходных комбинацион- 20 ных схем (диаграммы Вейтча, карты Карно), Пусть например, программа (фиг,6) имеет две точки слияния: в первой, имеющей адрес А,, сходятся две ветви, сигнатуры которых S, и S 25 во второй, имеющей адрес А2, сходятся три ветви, сигнатуры которых Sj, S- и Sg.. Поставим в соответствие указанным точкам слияния коды-идентифи1 L

каторы S1 и S , соответствующие на- 30 чальным состояниям блока 12, в которые тот устанавливается при прохождении данных точек. Тогда логика работы блока 12 описывается таблиц.ей, представленной на фиг.7, где S - 35 сигнатура, полученная в конце программы.

Блок 5 выдает на своих выходах коды s ,, . sf. , .S, когда на его входах коды А. . .А.. .А соответственно, 40 где S - эталонная сигнатура в i-й

IК

контрольной точке с адресом А;. На выходе 10 дешифратора 6 сигнал логической единицы появляется, когда на входах 1 - код одного из адресов А 45 и А или адрес команды начального пуска. На выходе 11 дешифратора 6 игнал логической единицы появляет- , я, когда на входах 1 - один из ко ов А.50

Так как предлагаемая структура стройства не накладьгоает никаких оганичений на расположение точек конт- оля, последние можно расположить в- очках, имеющих одинаковые сигнату- 55 ы, что максимально упрощает блок 5, сли выбрать контрольные точки указанным способом по каким-либо причиам не удается, их можно выбрать с

156

таким расчетом, чтобы эталонные сиг,, натуры отличались в минимальном числе разрядов, что также существенно уменьшает аппаратные затраты на реализацию устройства.

Время обнаружения ошибки определяется в рассмотренном случае расстоянием от места ее возникновения до ближайшей контрольной точки.

Для уменьшения вренени обнаружения ошибки можно использовать схему блока 4, показанную на фиг,2. На выходе 11 дешифратора 6 в зтом случае постоянно находится уровень логической единицы. Контроль хода выполнения программы осуществляется путем сравнения контрольного кода, сформированного из всех слов программы, предшествующих очередному и считанных ранее из памяти команд системы, с эталонным контрольным числом, извле- к аемым из блока 5 по тому же адресу, что и очередное слово из памяти команд. Если сформированный в блоке 12 контрольный код (сигнатура) совпада- ет с кодовым эталоном, считанным из блока 5, программа выполняется правильно, в противном случае на выходе 9 появляется сигнал ошибки. Массив контрольных кодов вычисляется и ; размещается в блоке 5 заранее, при этом по тем адресам, которые возбуждаются в памяти команд системы при прохождении программой точек слияния, в блоке 5 хранятся начальные состояния блока 12,-соответствующие указанным точкам. I

Использование изобретения обеспе - чивает. увеличение достоверности контроля: устройство позволяет обнаруживать ошибки, проявляющиеся в виде замены одной точки слияния другой.

Предлагаемое устройство может быть использовано и для контроля блоков микропрограммного управления. В этом случае функции блока 5 и дешифратора 6 выполняют дополнительные разряды памяти микрокоманд.

Формула изобретения

1., Устройство для контроля хода программ, содержащее дешифратор, блок формирования сигнатур, блок сравнения и элемент И, причем выход элемента И является выходом сигнала ошибки устройства, тактовый вход устройства

единен с. тактовым входом блока формирования,сигнатур и первым входом элемента И, информационный выход блока формирования.сигнатур соединен с первым .входом блока сравнения, выход которого соединен с вторым входом элемента И, группа информационных входов устройства соединена с группой информационных входов блока формирования сигнатур, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введен блок йамяти, причем адресные входы устройства соединены с информационными входами дешифратора, и адресными входами блока памяти, выходы которого соединены с вторьм входом блока сравнения, первый и второй выходы дешифратора соединены соответственно с входом модифи- iкации сигнатуры блока формирования ;сигнатур и с третьим входом элемен- та И.

2. Устройство по п. 1, о т л и - ч ающее с я тем, что блок формирования сигнатур содержит формиров атель контрольного кода, узел памяти и мультиплексор, группа выходов которого соединена с. первой группой, информационных входов формирователя контрольного кода, вторая группа информационных входов которого образует группу информационных входов блока, группа выходов формирователя контрольного кода соединена с группой адресных входов узла памяти,

первой группой информационных входов мультиплексора и является группой выходов блока, вторая группа информационных входов мультиплексора соеди - нена с группой выходов узла памяти,

тактовый вход формирователя контроль- .ного кода и управляющий вход мульти- .плексора образуют соответственно тактовый вход и вход модификации сигнатуры блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода микропрограмм | 1990 |

|

SU1728865A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1997 |

|

RU2127447C1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем. Цель изобретения - повышение достоверности контроля. Устройство содержит блок 4 формирования сигнатуры, блок 5 памяти, дешифратор 6, блок 7 сравнения и элемент И 8. Устройство позволяет обнаруживать ошибки, проявляющиеся в виде замены одной точки слияния другой. 1 з.п. ф-лы, 7 ил.

(рив.2

ЫЗ

П

№

5й

17

N.

№

18

-Л V

-т/

PS (тУ

HS V

73

у

Ъ

Фие,3

CUD

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1300479, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-15—Публикация

1987-12-17—Подача