оо ел

00

ел

Ј

31

Изобретение относится к автоматике и вычислительной технике, и может быть использовано в аппаратуре автоматизированного контроля и диагностирования цифровых узлов.

Целью изобретения является увеличение глубины контроля.

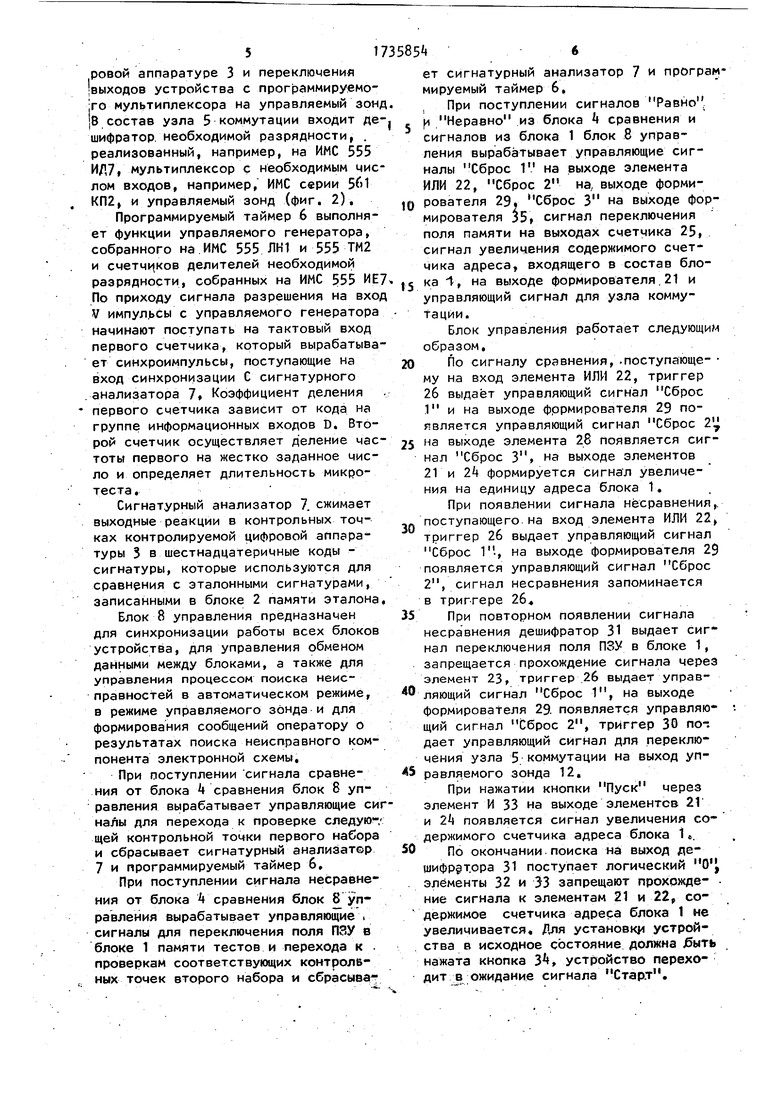

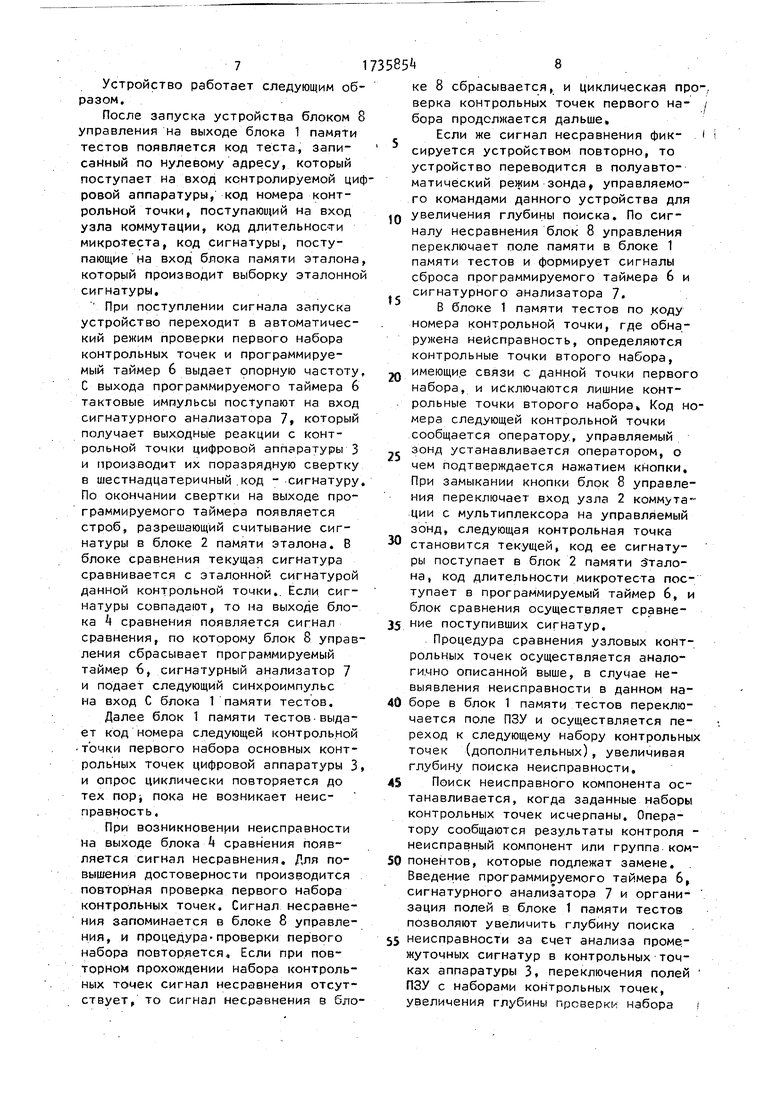

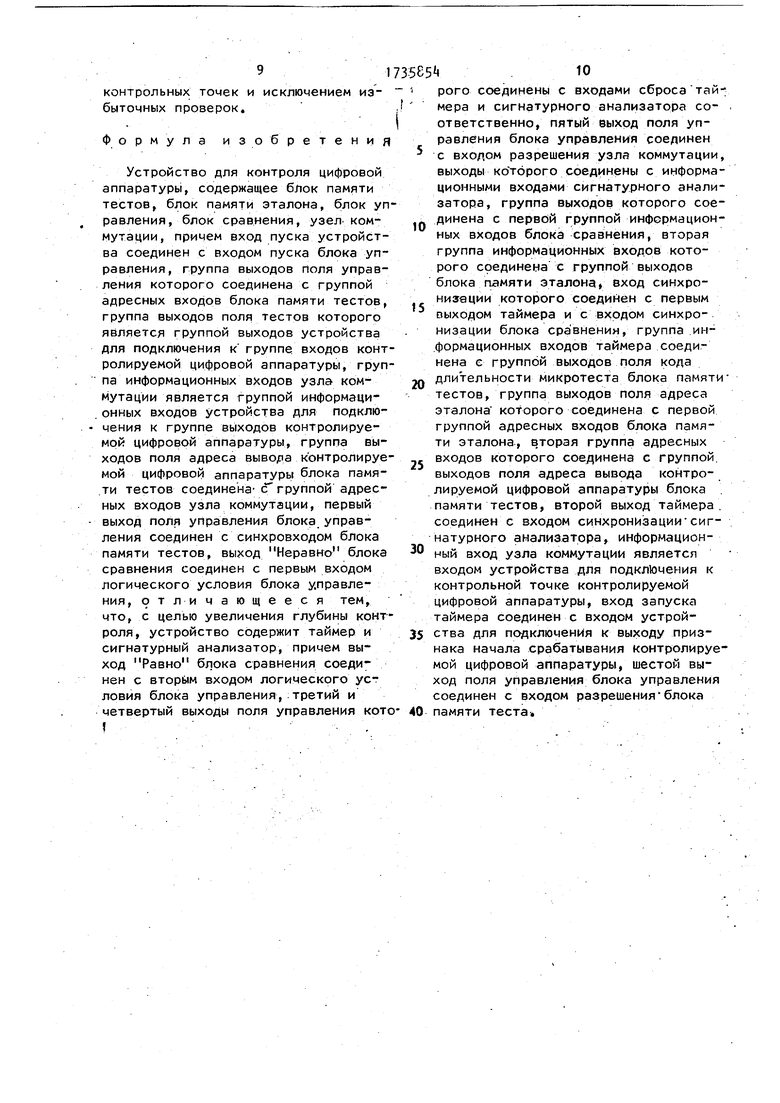

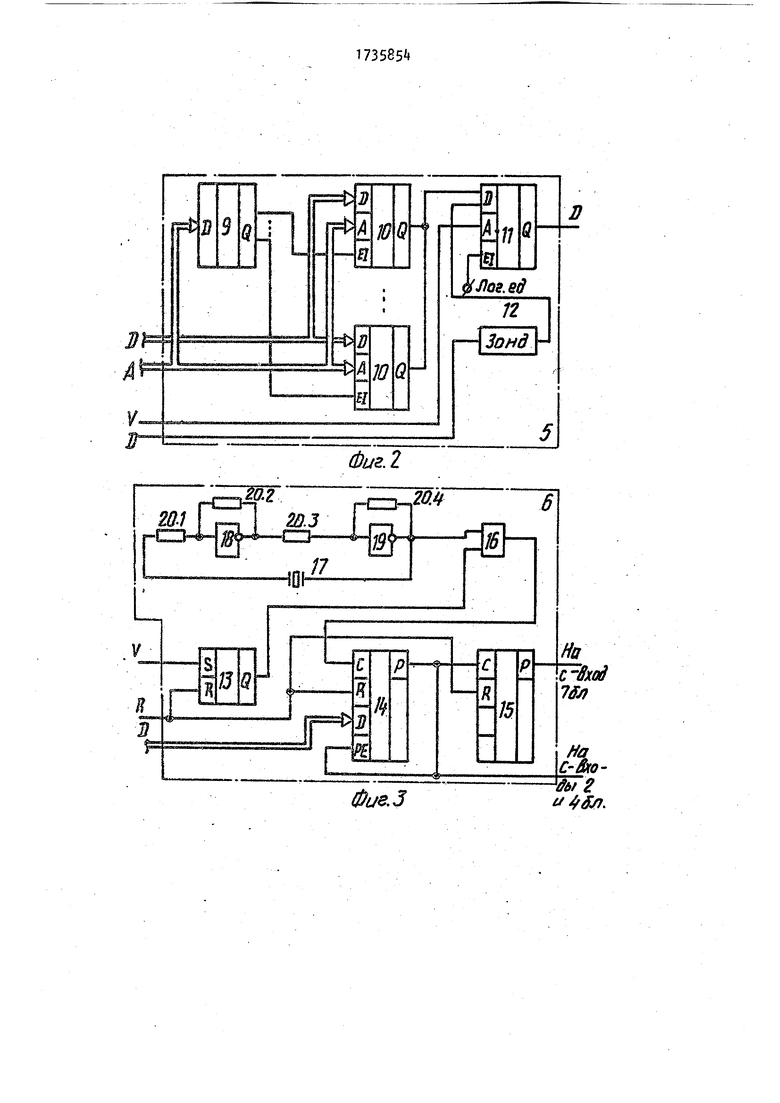

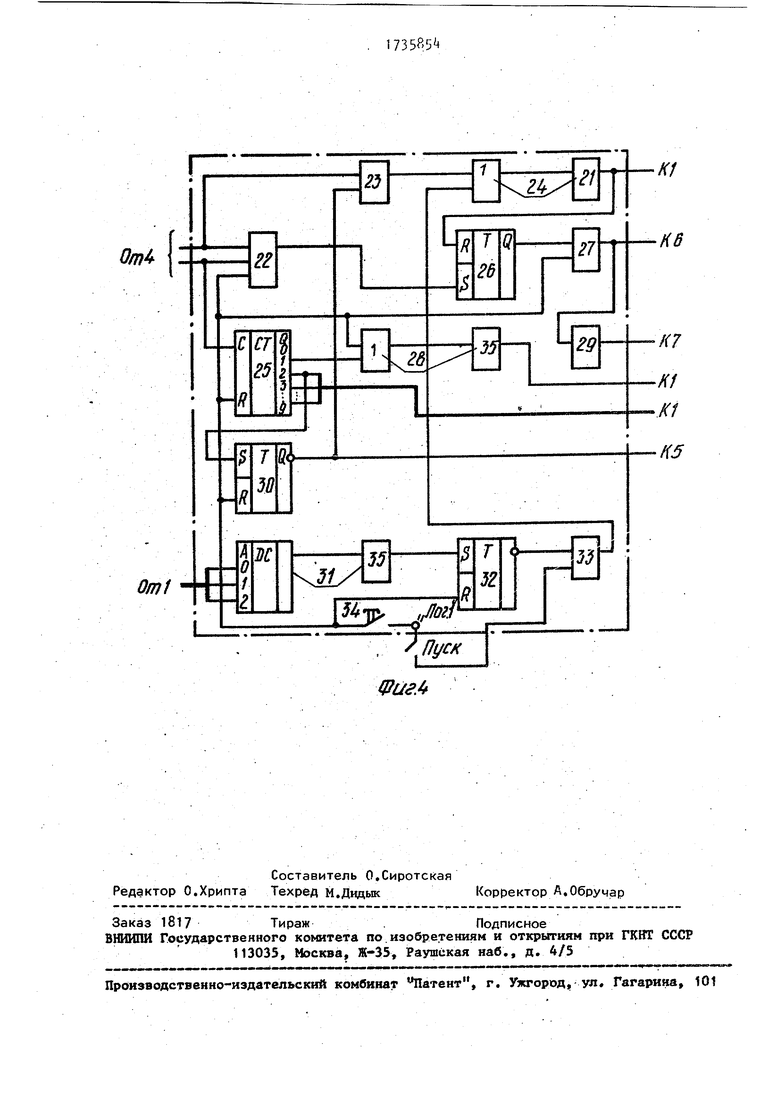

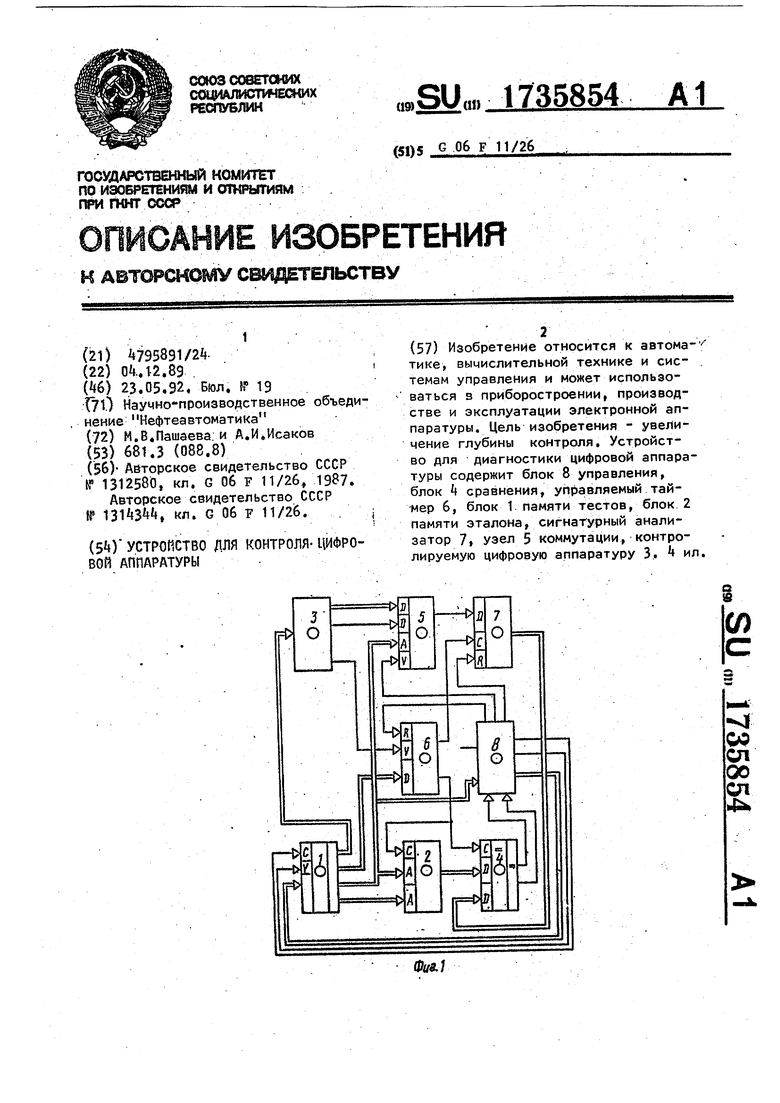

На фиг.1 показано устройство для контроляi на фиг.2 - узел коммутации на Фиг.З программируемый таймер; на фиг. - блок управления.

Устройство содержит блок 1 памяти тестов, блок 2 памяти эталона 2,контролируемую цифровую аппаратуру 3, блок А сравнения, узел i 5 коммутации, программируемый таймер 6., сигнатурный анализатор 7., блок 8 управления.

Узэл 5 коммутации содержит дешифратор 9, группу коммутаторов 10, коммутатор 11, зонд 12,

Программируемый таймер содержит триггер 13, счетчики 14 и 15, элемен И 16, генератор 17 построенный на кварцевом резонаторе, элементах НЕ 18 и 19, резисторах 20,1.. .20,k.Блок управления содержит формирователь 21 импульса, элементы ИЛИ 22, элемент И 23, элемент ИЛИ 2k, счетчик 25, триггер 26, элементы ИЛИ 27 и 28, формирователь 29 импульса, триггер 30, дешифратор 31 триггер 32, элемент И 33, кнопку 3 сброса, формирователь 35 импульса.

Блок 1 памяти тестов представляет собой ПЗУ с расширенным набором полей памяти 1 { 2..., nl, тле содержатся поле тестов, поле адресов контрольных точек, поле адресов эталонных сигнатур, поле кода длительности микротеста. Поле адресов контрольных точек содержит адреса кодов наборов контрольных точек контролируемой цифровой аппаратуры 3. Первый набор содержит минимальное количество основных, наиболее важных, контрольных точек - выходов, контролируемой цифровой аппаратуры 3. Проверка первого набора определяет неисправный узел .цифровой аппаратуры 3. Второй набор контрольных точек содержит узловые контрольные точки для проверки каждого узла. Следующий набор содержит дополнительные контрольные точки второго набора и т.д. Переходы между контрольными точками определены в блоке 1 памяти тестов.

5

5

0

Таким образом, каждый набор контрольных точек увеличивает глубину локализации для выявления неисправно- го компонента контролируемой цифровой аппаратуры, являющегося источником неправильного функционирования.

Информация в блоке 1 памяти тестов записана следующим образом.

В хранятся коды тестовых последовательностей, коды длительности микротеста, коды номеров контрольных точек, например, при выявлении неисправности в первом наборе контрольных точек {N,}, по коду номера контрольной точки п вызываются коды теста, длительности микротеста, адрес эталонной сигнатуры, адрес контрольной точки.

При несравнении эталонной сигнатуры с текущей необходимо увеличить глубину локализации, для чего переключается поле памяти ПЗУ. От кода номера контрольной точки первого набора п; осуществляется переход к коду соответствующей ей первой контрольной точке второго набора njj, затем к коду второй контрольной точки второго набора nj2 и т.д,

n,e{N/}, nje{Nt},

nj,,

l)Z

)к

и т. д,

Таким образом, блок памяти тестов 1 совмещает функции блока памяти мо

дели контролируемой цифровой аппаратуры, блока анализа последовательности проверки, блока памяти тестов и длительности микротестов и позволяет провести гибкую процедуру диагностики, зависящую от промежуточных результатов проверок.

Блок 2 памяти эталона содержит эталонные сигнатуры для наборов контрольных точек контролируемой цифровой

аппаратуры. Эталонные сигнатуры в каждой контрольной точке используются для сравнения- с текущими сигнатурами, полученными непосредственно при контроле объекта.

Блок -4 сравнения служит для сравнения текущей сигнатуры контролируемой цифровой аппаратуры 3, поступающей на вход данных от сигнатурного анализатора 7 и эталонной сигнатуры,

поступающей на вход данных из блока 2 памяти эталона. Результаты сравнения поступают в блок Г управления .Узел 5 коммутации служит для подключения устройства контроля к цифровой аппаратуре 3 и переключения выходов устройства с программируемого мультиплексора на управляемый зон {В состав узла 5 коммутации входит дешифратор необходимой разрядности, реализованный, например, на ИМС 555 ИД7 мультиплексор с необходимым числом входов, например, ИМС серии 561 КП2, и управляемый зонд (фиг. 2),

Программируемый таймер 6 выполняет функции управляемого генератора, собранного на ИМС 555 ЛН1 и 555 ТМ2 и счетчиков делителей необходимой разрядности, собранных на ИМС 555 ИЕ По приходу сигнала разрешения на вхо V импульсы с управляемого генератора начинают поступать на тактовый вход первого счетчика, который вырабатывает синхроимпульсы, поступающие на вход синхронизации С сигнатурного анализатора 7 Коэффициент деления первого счетчика зависит от кода на группе информационных входов D. Второй счетчик осуществляет деление частоты первого на жестко заданное число и определяет длительность микротеста .

Сигнатурный анализатор 7. сжимает выходные реакции в контрольных точках контролируемой цифровой аппаратуры 3 в шестнадцатеричные коды - сигнатуры, которые используются для сравнения с эталонными сигнатурами, записанными в блоке 2 памяти эталона

Блок 8 управления предназначен для синхронизации работы всех блоков устройства, для управления обменом данными между блоками, а также для управления процессом поиска неисправностей в автоматическом режиме, в режиме управляемого зонда и для формирования сообщений оператору о результатах поиска неисправного компонента электронной схемы.

При поступлении сигнала сравнения от блока k сравнения блок 8 управления вырабатывает управляющие сигналы для перехода к проверке следую-/ щей контрольной точки первого набора и сбрасывает сигнатурный анализатор 7 и программируемый таймер 6,

При поступлении сигнала несравнения от блока 4 сравнения блок 8 управления вырабатывает управляющие . сигналы для переключения поля ПЗУ в блоке 1 памяти тестов и перехода к . проверкам соответствующих контролв- ных точек второго набора и сбрасыва

д.

73585 6

ет сигнатурный анализатор 7 и програм« 5

10

15

20

25

мируемый таймер 6,

При поступлении сигналов Равно и Неравно из блока k сравнения и сигналов из блока 1 блок 8 управления вырабатывает управляющие сигналы Сброс 1 на выходе элемента ИЛИ 22, Сброс 2 на, выходе формирователя 29. Сброс 3 на выходе формирователя 35 сигнал переключения поля памяти на выходах счетчика 25 сигнал увеличения содержимого счетчика адреса, входящего в состав блока Л, на выходе формирователя 21 и управляющий сигнал для узла коммутации.

Блок управления работает следующим образом.

По сигналу сравнения, .поступающе- му на вход элемента ИЛИ 22, триггер 26 выдаёт управляющий сигнал Сброс 1 и на выходе формирователя 29 по- гвляется управляющий сигнал Сброс 2 на выходе элемента 28 появляется сигнал Сброс 3, на выходе элементов 21 и 2k формируется сигнал увеличения на единицу адреса блока 1,

При появлении сигнала несравнения, ,« поступающего на вход элемента ИЛИ 22, триггер 26 выдает управляющий сигнал Сброс 1., на выходе формирователя 29 появляется управляющий сигнал Сброс 2, сигнал несравнения запоминается в триггере 26.,

При повторном появлении сигнала несравнения дешифратор 31 выдает сиг- нал переключения поля ПЗУ в блоке 1, запрещается прохождение сигнала через элемент 23, триггер 26 выдает управляющий сигнал Сброс 1, на выходе формирователя 29 появляется управляющий сигнал Сброс 2, триггер 30 по-. дает управляющий сигнал для переключения узла 5 коммутации на выход управляемого зонда 12,

При нажатии кнопки Пуск через элемент И 33 на выходе элементов 21 и 2k появляется сигнал увеличения содержимого счетчика адреса блока 1«

По окончании поиска на выход де- шифр§тора 31 поступает логический О элементы 32 и 33 запрещают прохожде- ние сигнала к элементам 21 и 22, содержимое счетчика адреса блока 1 не увеличивается. Для установки устройства в исходное состояние должна быть нажата кнопка , устройство переходит в ожидание сигнала Старт.

35

40

4S

SO

7

Устройство работает следующим образом.

После запуска устройства блоком 8 управления на выходе блока 1 памяти тестов появляется код теста, записанный по нулевому адресу, который поступает на вход контролируемой цифровой аппаратуры, код номера контрольной точки, поступающий на вход узла коммутации, код длительности микротеста, код сигнатуры, поступающие на вход блока памяти эталона который производит выборку эталонно сигнатуры.

При поступлении сигнала запуска устройство переходит в автоматический режим проверки первого набора контрольных точек и программируемый таймер 6 выдает опорную частоту С выхода программируемого таймера 6 тактовые импульсы поступают на вход сигнатурного анализатора 7 который получает выходные реакции с контрольной точки цифровой аппаратуры 3 и производит их поразрядную свертку в шестнадцатеричный код - сигнатуру По окончании свертки на выходе программируемого таймера появляется строб, разрешающий считывание CHI- натуры в блоке 2 памяти эталона. В блоке сравнения текущая сигнатура сравнивается с эталонной сигнатурой данной контрольной точки. Если CHI- натуры совпадают, то на выходе блока 4 сравнения появляется сигнал сравнения, по которому блок 8 управления сбрасывает программируемый таймер 6, сигнатурный анализатор 7 и подает следующий синхроимпульс на вход С блока 1 памяти тестов.

Далее блок 1 памяти тестов выдает код номера следующей контрольной точки первого набора основных контрольных точек цифровой аппаратуры 3 и опрос циклически повторяется до тех пор, пока не возникает неисправность.

При возникновении неисправности на выходе блока А сравнения появляется сигнал несравнения. Для повышения достоверности производится повторная проверка первого набора контрольных точек. Сигнал несравнения запоминается в блоке 8 управления, и процедура-проверки первого набора повторяется. Если при повторном прохождении набора контрольных точек сигнал несравнения отсутствует, то сигнал несравнения в бло15

ке 8 сбрасывается, и циклическая про-. верка контрольных точек первого на- / бора продолжается дальше.

Если же сигнал несравнения фик- i сируется устройством повторно, то устройство переводится в полуавтоматический режим зонда, управляемого командами данного устройства для

.Q увеличения глубины поиска. По сигналу несравнения блок 8 управления переключает поле памяти в блоке 1 памяти тестов и формирует сигналы сброса программируемого таймера 6 и сигнатурного анализатора 7.

В блоке 1 памяти тестов по коду номера контрольной точки, где обнаружена неисправность, определяются контрольные точки второго набора,

2« имеющие связи с данной точки первого набора, и исключаются лишние контрольные точки второго набораk Код номера следующей контрольной точки сообщается оператору, управляемый

j, зонд устанавливается оператором, о чем подтверждается нажатием кнопки. При замыкании кнопки блок 8 управления переключает вход узла 2 коммутации с мультиплексора на управляемый зонд, следующая контрольная точка

™ становится текущей, код ее сигнатуры поступает в блок 2 памяти Эталона, код длительности микротеста поступает в программируемый таймер 6, и блок сравнения осуществляет сравне35 ние поступивших сигнатур.

Процедура сравнения узловых контрольных точек осуществляется аналогично описанной выше, в случае невыявления неисправности в данном на40 боре в блок 1 памяти тестов переключается поле ПЗУ и осуществляется переход к следующему набору контрольных точек (дополнительных), увеличивая глубину поиска неисправности.

45 Поиск неисправного компонента останавливается, когда заданные наборы контрольных точек исчерпаны. Оператору сообщаются результаты контроля - неисправный компонент или группа ком50 понентов, которые подлежат замене. Введение программируемого таймера 6, сигнатурного анализатора 7 и органи- зация полей в блоке 1 памяти тестов позволяют увеличить глубину поиска

55 неисправности за счет анализа промежуточных сигнатур в контрольных точках аппаратуры 3, переключения полей ПЗУ с наборами контрольных точек, увеличения глубины проверка набора

контрольных точек и быточных проверок.

исключением иэФормула изобретения

Устройство для контроля цифровой аппаратуры, содержащее блок памяти тестов, блок памяти эталона, блок управления, блок сравнения, узел коммутации, причем вход пуска устройства соединен с входом пуска блока управления, группа выходов поля управления которого соединена с группой адресных входов блока памяти тестов, группа выходов поля тестов которого является группой выходов устройства для подключения к группе входов контролируемой цифровой аппаратуры, группа информационных входов узла коммутации является группой информационных входов устройства для подключения к группе выходов контролируемой цифровой аппаратуры, группа выходов поля адреса вывода контролируемой цифровой аппаратуры блока памяти тестов соединена- с группой адресных входов узла коммутации, первый

выход поля управления блока управления соединен с синхровходом блока памяти тестов, выход Неравно блока сравнения соединен с первым входом логического условия блока управления, отличающееся тем, что, с целью увеличения глубины контроля, устройство содержит таймер и сигнатурный анализатор, причем выход Равно блока сравнения соединен с вторым входом логического условия блока управления, третий и четвертый выходы поля управления кото- I

0

5

рого соединены с входами сброса таймера и сигнатурного анализатора со- , ответственно, пятый выход поля управления блока управления соединен с входом разрешения узла коммутации, выходы которого соединены с информационными входами сигнатурного анализатора, группа выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с группой выходов блока памяти эталона вход синхронизации которого соединен с первым выходом таймера и с входом синхронизации блока сравнения, группа информационных входов таймера соединена с группой выходов поля кода

длительности микротеста блока памяти тестов, группа выходов поля адреса эталона которого соединена с первой группой адресных входов блока памяти эталона, вторая группа адресных входов которого соединена с группой выходов поля адреса вывода контролируемой цифровой аппаратуры блока памяти тестов, второй выход таймера . соединен с входом синхронизации1сигнатурного анализатора, информационный вход узла коммутации является входом устройства для подключения к контрольной точке контролируемой цифровой аппаратуры, вход запуска таймера соединен с входом устрой5 ства для подключения к выходу признака начала срабатывания контролируемой цифровой аппаратуры, шестой выход поля управления блока управления соединен с входом разрешения блока

0 памяти теста.

5

0

От

Кб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Цифровой компаратор | 1987 |

|

SU1552136A1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

Изобретение относится к автома- / тике, вычислительной технике и системам управления и может использоваться в приборостроении, производстве и эксплуатации электронной аппаратуры. Цель изобретения - увеличение глубины контроля. Устройство для диагностики цифровой аппаратуры содержит блок 8 управления, блок А сравнения, управляемый таймер 6, блок 1 памяти тестов, блок 2 памяти эталона, сигнатурный анализатор 7 узел S коммутации, контролируемую цифровую аппаратуру 3. ил.

M

K1

К5

ФигА

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( УСТРОЙСТВО ДЛЯ КОНТРОЛЯ- ЦИФРОВОЙ АППАРАТУРЫ | |||

Авторы

Даты

1992-05-23—Публикация

1989-12-04—Подача