Изобретение относится к вычислительной технике и мСжет быть использовано для построения оперативных энергозависимых (с батарейным питанием) запоминающих устройств с наращиваемой информационной структурой и контролем адреса

Целью изобретения является повыше-, ние надежности и уменьшение потребляемой мощности устройства,,

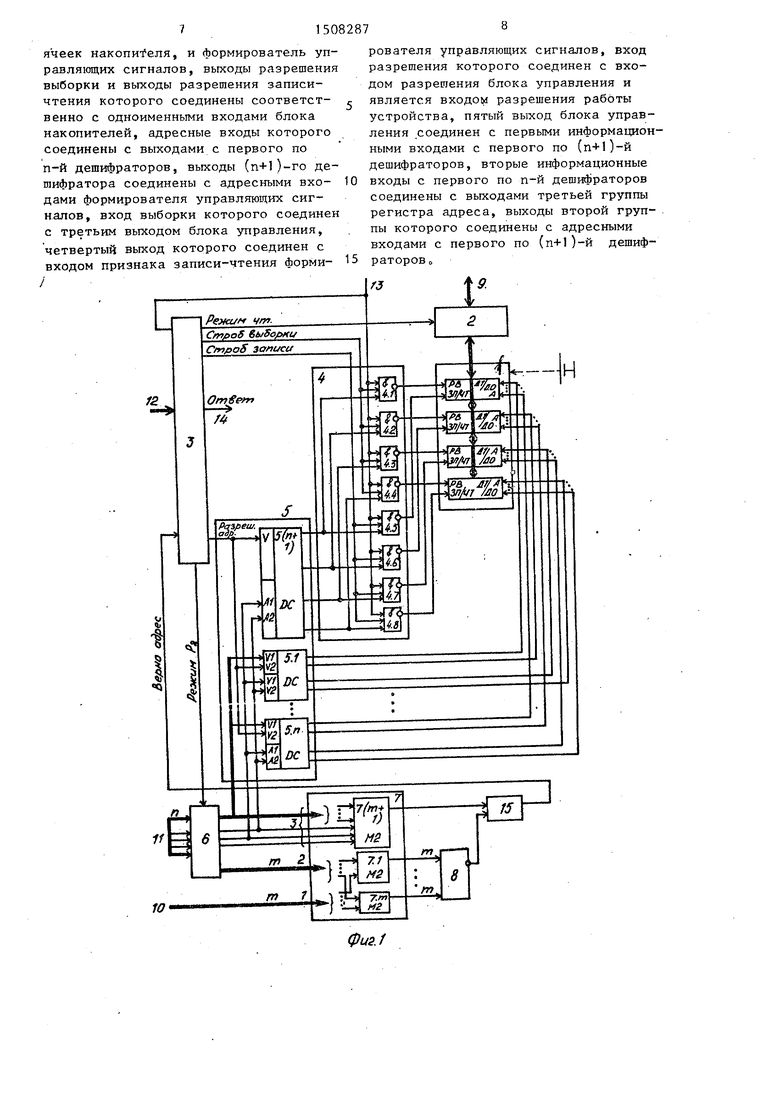

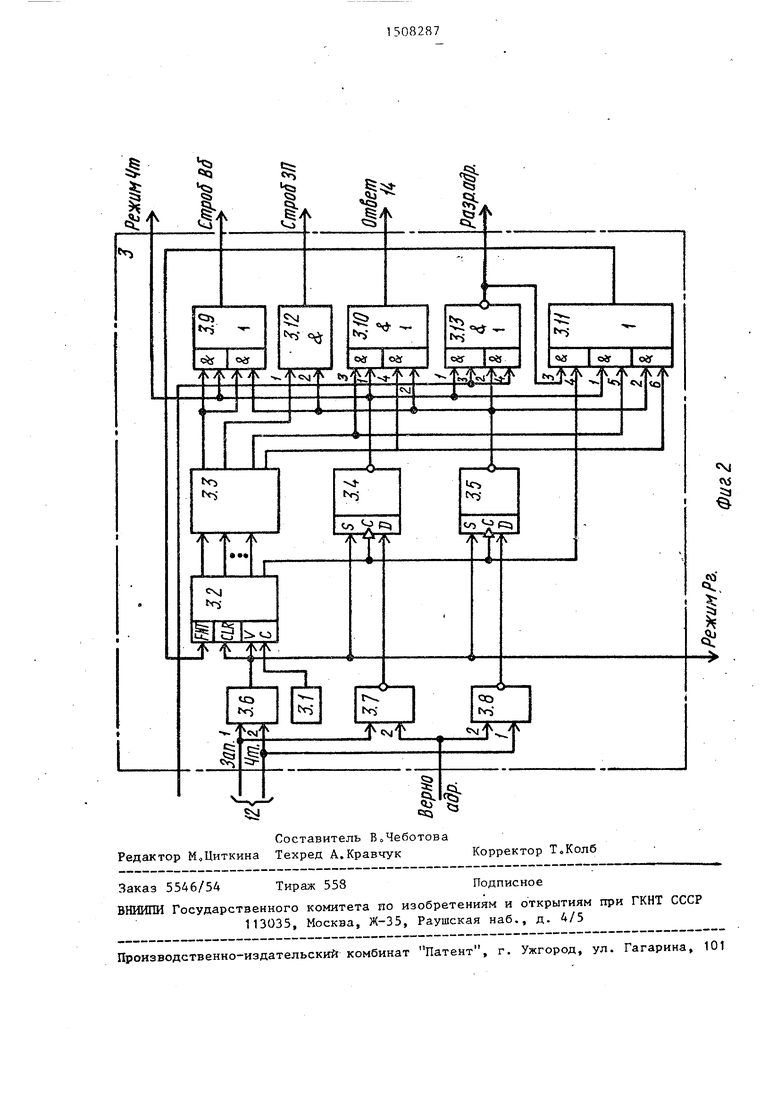

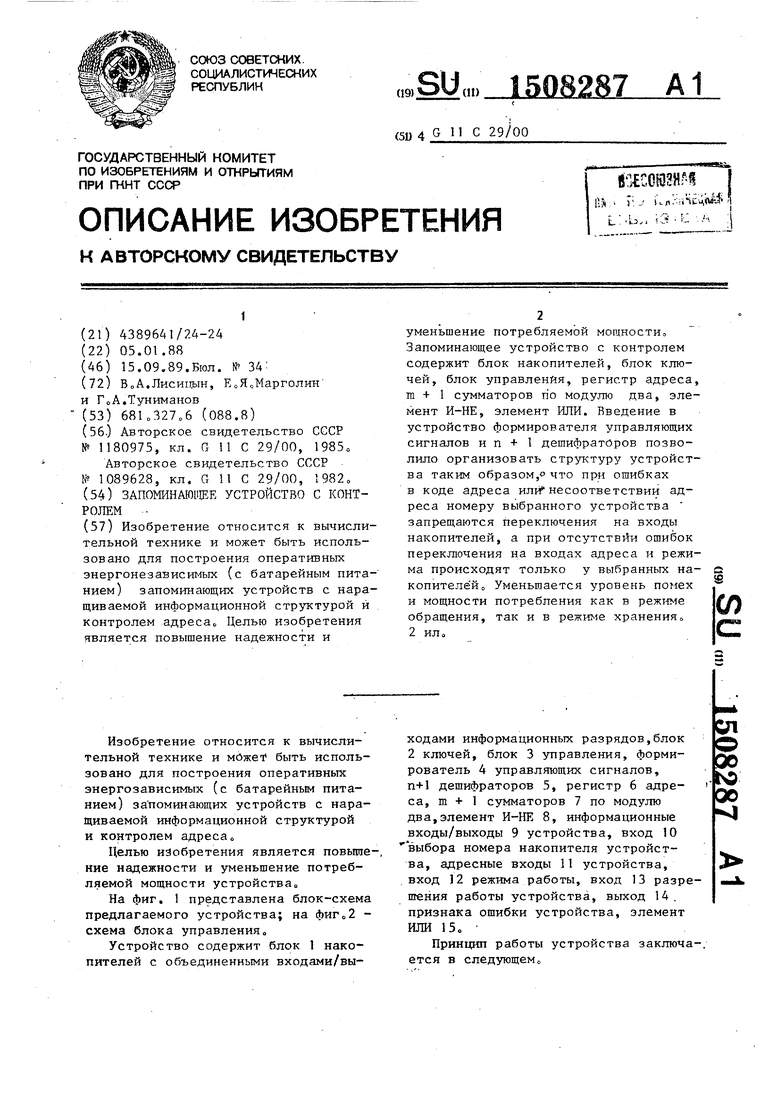

На фиг, 1 представлена блок-схема предлагаемого устройства; на фиг„2 - схема блока управления о

Устройство содержит блок 1 накопителей с объединенньми входами/выходами информационных разрядов,блок 2 ключей, блок 3 управления, формирователь 4 управляющих сигналов, п+1 дешифраторов 5, регистр 6 адре- са, m + 1 сумматоров 7 по модулю два,элемент И-НЕ 8, информационные входы/выходы 9 устройства, вход 10 выбора номера накопителя устройства, адресные входы 11 устройства, вход 12 режима работы, вход 13 разрешения работы устройства, выход 14. признака ошибки устройства, элемент ИЛИ 15о

Принцип работы устройства заключа-. ется в следующем

;д х

ND Х Ч

315082

При подаче на один нз входов шины 12 сигналов Запись или Чтение в регистре 6 адреса фиксируется по сигналу блока 3 Режим Рг код адре- са с шины „ В блоке 3 по сигналам Запись (Чтение) происходит сняр тие блокировки с распределителя 3.2, триггеров Зо4, 3.5 (установленных предварительно в состояние 1 потен- циалом, соответствующим отсутствию сигналов Запись, Чтение) и разрешается прохождение синхроимпульсов генератора 3.1 через синхровход распределителя 3.2 Так как триггеры 3.4, Зо5 находились в состоянии 1, то потенциалом с выхода элемента Зо13 разрешается формирование, элементов 3.11 сигнала прерьгоания работы распределителя 3,2 по первому же импульсу генератора Зо1, поступившему в распределитель и вызвавшему переключение на его выходе, соединенном с синхровходом триггеров 3.4,3о5 Если к этому моменту на информационных входах триггеров сформировался сигнал исправности адреса, то он запишется в триггер 3«4 или 3.5 (в зависимости от режима Чтение или Запись), при этом прерывание снимает- ся, так как триггер 3.4 или 3.5 пе,-

реключается из 1

О , и распределитель продолжает работу Если в коде адреса ошибка или адрес не соответствует номеру выбранного устройст- ва, то дальнейшее переключение распределителя 3.2 и формирование синхросигнала формирователем 3.3 не производится о Отсутствие переключений распределителя в этом случае являет- ся дополнительным фактором снижения уровня помех о

Сигнал исправности адреса вьфаба- тывается в сумматорах 7 и элементах И-НЕ 8, ИЛИ 15, при этом предполага- ется, что суммарное время задержки в этом блоке и элементах 8, 3„7,3о8 И-НЕ и элементе ИЛИ 15 меньше времени между передними фронтами сигналов Запись, Чтение и сигналов адреса

В т+1 сумматорах 7 производится свертка сумматором 7о1 по модулю два кода адреса с контрольным разрядом и поразрядное сравнение группы разрядов кода адреса с кодом номера уст- ройства в сумматорах 7.I,..,7т (селекция адреса). Элементами 8 и 15 вырабатьшается окончательно сигнал исправности адреса.

с Ю 152030

25

3540

45 . JQ

Сигнал на входе 13 устанавливают с некоторой задержкой после включения питания для того, чтобы избежать несанкционированных переключений в режимных и адресных входах накопителей 1 о При отсутствии или снижении основного питания сигнал на входе 13 имеет нулевой уровень, что обеспечивает поддержание блокирующих потенциалов на режимных входах накопителей (при снижении и отсутствии питания) и постоянство потенциала на адресных входах (при снижении питания). При отсутствии основного питания постоянство потенциалов на адресных входах обеспечивается резис- торными привязками. Благодаря этому потребление накопителей во время коммутации питания остается минимальным.

В режиме записи или чтения информации при наличии сигнала исправности адреса триггеры Зо5 или Зо4 переключаются и, так как на входе 13 устройства - разрешающий потенциал,формируют на выходе элемента сигнал разрешения адреса о При отсутствии сигнала исправности адреса не происходит переключение триггеров 3.4 или Зо5, сигнал разрешения адреса не вырабатывается, вследствие чего сигналы на выходах дешифраторов .5 отсутствуют и обращение к накопителям группы 1 не происходит о

При поступлении на первые управляющие входы дешифраторов 5 сигнала разрешения адреса на выходах дешифратора 5о(п+1) возникает сигнал, разрешающий формирование сигналов выборки и записи только для выбранного накопителя блока 1, На вькодах остальных дешифраторов 5, соответствующих входам адреса выбранного накопителя, формируется код адреса,аналогичный коду на вторых управляющих входах этих дешифраторов. На остальных выходах, соответствующих входам адреса невыбранных накопителей, дешифраторов 5о1,о.о,5оП, потенциал остается неизменным

В режиме записи сигналом с выхода блока 3 ключи блока 2 открыты на прием информации с шины 9о Стробы выборки и записи, сформированные формирователем ЗоЗ в соответствии с требуе- i мой временной диаграммой накопителей 1, поступают через элементы 3.9,3.12 на входы формирователя 4 управляющих сигналов и, так как на входе 13

разрешающий потенциал, в виде сигналов выборки и записи поступают на входы выбранного накопителя, на другие входы которого уже поступили коды информации и адреса.

В режиме чтения ключи блока 2 сигналом с блока 3 открыты на передачу. На входах разрешения выборки и записи/чтения выбранного накопителя 1 блоками 3 и 4 формируются соответствующие сигналы, и считываемая информация поступает на выходы 9,

После отработки цикла записи ипи чтения по сигналам с формирователя 3.3, поступающим через элемент 3„11 на вход прерьшания распределителя Зо2, происходит остановка работы распределителя 3.2. По сигналам формирователя ЗоЗ (в случае переключения триггеров Зо4, Зо5) элементом ЗоЮ вырабатывается сигнал ответа, который свидетельствует об исправности адреса и поступает на контрольный выход 14 устройства. При ошибках в коде адреса или его несоответствии номеру устройства сигнал ответа не вырабатывается о

Техническая эффективность предлагаемого устройства заключается в повышении надежности запоминающего устройства за счет уменьшения уровня помех и исключения обращений по ложным адресам благодаря запрету переключений адресных сигналов на адресны вькодах тех накопителей, обращение к KOTOfibiM не производится, и запрету прохождения кода адреса на входы накопителей при ошибках в адресе или его несоответствии коду номера устройства; облегчения режима работы блоков устройства благодаря распараллеливанию сигналов адреса, уменьшению емкостной нагрузки по адресным цепям; уменьшения вероятности искаже .ния информации в моменты коммутации питания за счет постоянства потенциалов на адресных и режимных входах в эти моменты времени; снижение потребляемой мощности происходит как в режиме обращения за счет уменьшения длительности фронта адресных сигналов, использования в качестве буферных схем адреса маломощных дешифраторов с относительно низким коэффициентом разветвления и невозможности переключения на входах невыбранных накопителей, так и в режиме хранения, а также при коммутации питания, за

счет постоянства потен1и алов на адресных и режимных входах накопителей,,

Кроме того, улучшаются временные характеристики устройства, такие как время выборки и цикл обращеттия за счет уменьшения длительности фронта адресных сигналов, а также увеличивается срок хра1;ения информации за счет уменьшения потребления в моменты коммутации питания о

Формула изобретения

0

5

0

5

0

5

Запоминающее устройство с контролем, содержащее блок накопителей, блок управления, регистр адреса т+ сумматоров по модулю два, (где m определяется по формуле q 2, q - количество накопителей), блок ключей, элемент ИЛИ и элемент И-НЕ,входы которого соединены с выходами с первого по т-й сумматоров по модулю два, первые входы которых соединены с выходами второй группы регистра адреса, вторые входы с первого по т-й сумматоров по модулю два являются входами выбора номера накопителя устройства, информационные входы и вход контрольного разряда регистра адреса являются адр есными входами устройства, выходы второй, третьей групп и контрольный разряд регистра адреса соединены с входами (in+l)-ro сумматора по модулю два, выход которого соединен с первым входом элемента ИЛИ, выход элемента И-НЕ соединен .с вторым входом элемента ИЛИ, выход которого соединен с входом признака корректности адреса блока управления, вход задания режима которого является входом задания режима устройства, первый и второй выходы блока управления соединены соответственно с входом управления регистра адреса и входом управления блока ключей, первые входы-выходы которого соединены с информационными входами- п выходами блока накопителей,вторые входы-выходы блока ключей являются информационными входами-выходами устройства, шестой выход блока управления является выходом признака ошиб- , ки устройства, отличающееся тем, что, с целью повьш1ения надежности и уменьшения потребляемой мощности устройства, в него введены п+1 дешифраторов, где п - количествд

1508287

ячеек накопителя, и формирователь управляющих сигналов, выходы разрешения выборки и выходы разрешения записи- чтения которого соединены соответственно с одноименными входами блока накопителей, адресные входы которого соединены с выходами с первого по п-й дешифраторов, выходы (п+1)-го деифратора соединены с адресными вхо- 10 ами формирователя управляющих сигналов, вход выборки которого соединен с третьим выходом блока управления, четвертый выход которого соединен с

входом признака записи-чтения форми- 15 раторов

рователя разрешен дом разр является устройст ления со ными вхо дешифрат входы с соединен регистра пы котор входами

8

раторов

рователя управляющих сигналов, вход разрешения которого соединен с входом разрешения блока управления и является входом разрешения работы устройства, пятый выход блока управления соединен с первыми информационными входами с первого по (п+П-й дешифраторов, вторые информационные входы с первого по п-й дешифраторов соединены с выходами третьей группы регистра адреса, выходы второй группы которого соединены с адресными входами с первого по (п+1)-й дешиф

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1125658A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Постоянное запоминающее устройство с контролем | 1988 |

|

SU1575240A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных энергонезависимых (с батарейным питанием) запоминающих устройств с наращиваемой информационной структурой и контролем адреса. Целью изобретения является повышение надежности и уменьшение потребляемой мощности. Запоминающее устройство с контролем содержит блок накопителей, блок ключей, блок управления, регистр адреса, M + 1 сумматоров по модулю два, элемент И-НЕ, элемент ИЛИ. Введение в устройство формирователя управляющих сигналов и N + 1 дешифраторов позволило организовать структуру устройства таким образом, что при ошибках в коде адреса или несоответствии адреса номеру выбранного устройства запрещаются переключения на входы накопителей, а при отсутствии ошибок переключения на входах адреса и режима происходят только у выбранных накопителей. Уменьшается уровень помех и мощности потребления как в режиме обращения, так и в режиме хранения. 2 ил.

| ) Авторское свидетельство СССР № 1180975, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-05—Подача