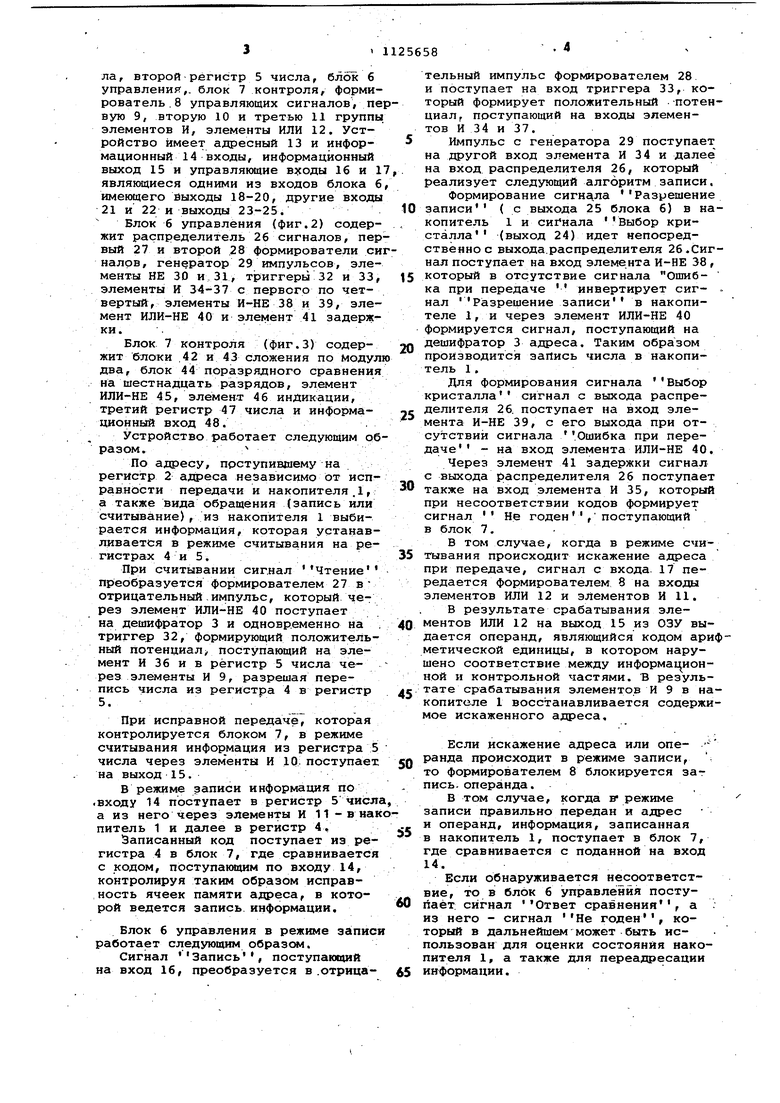

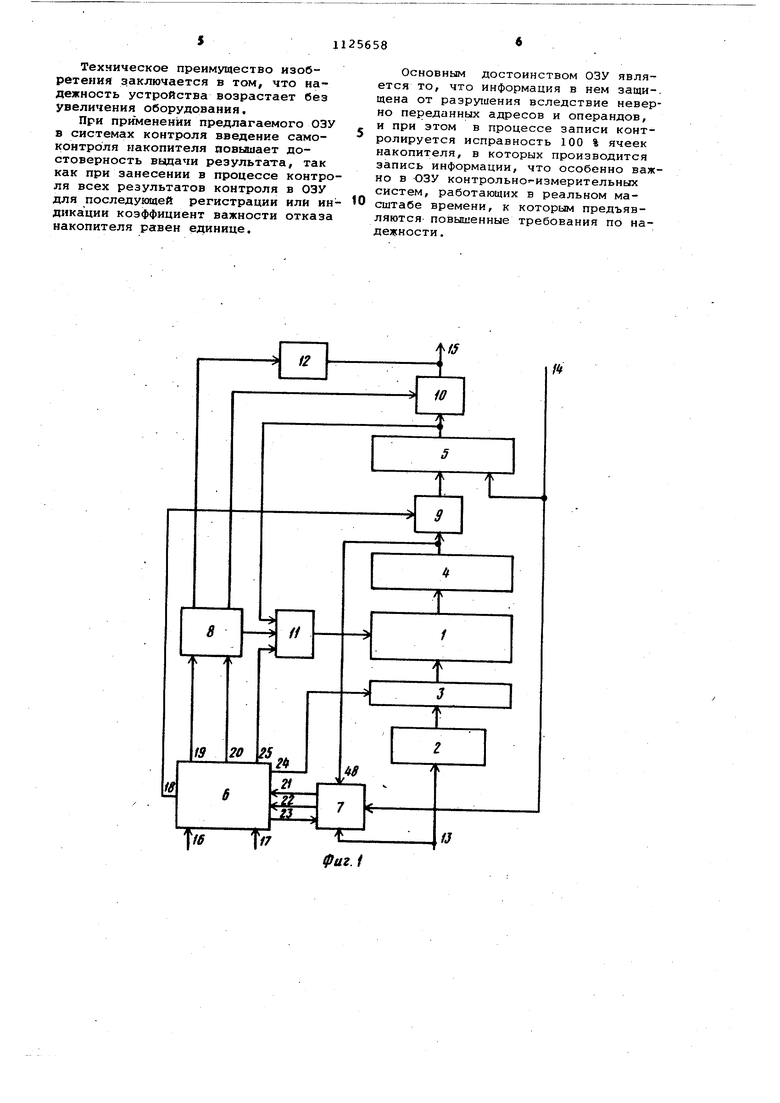

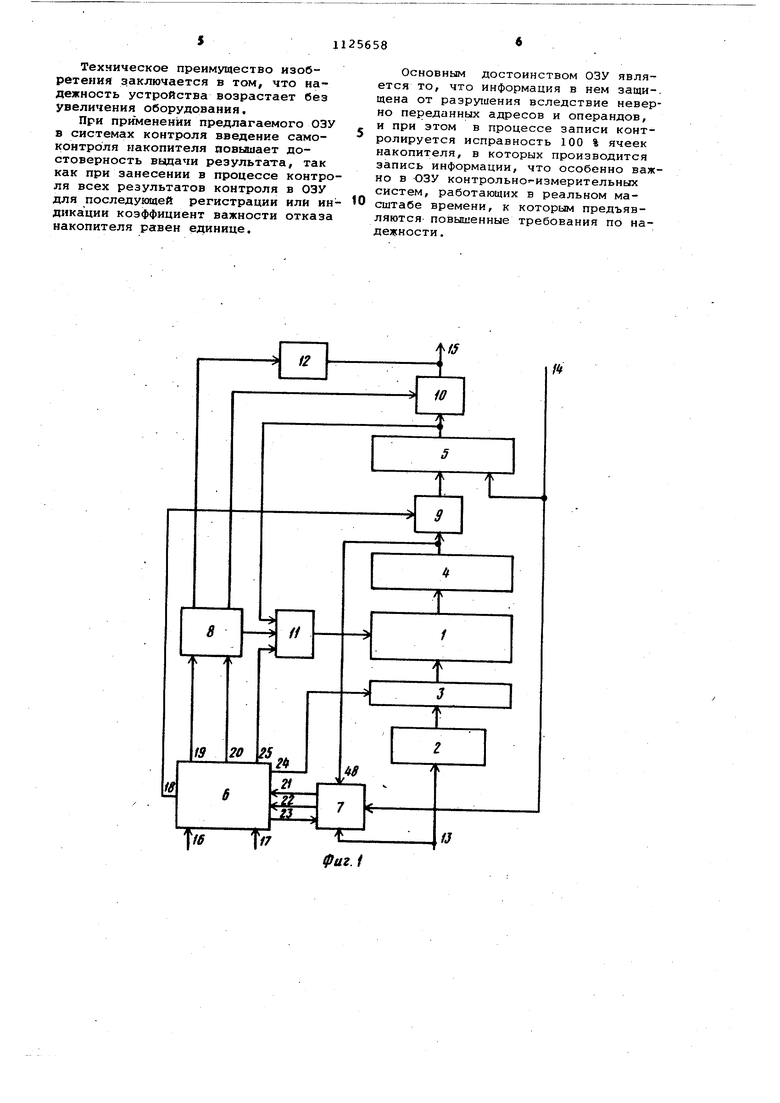

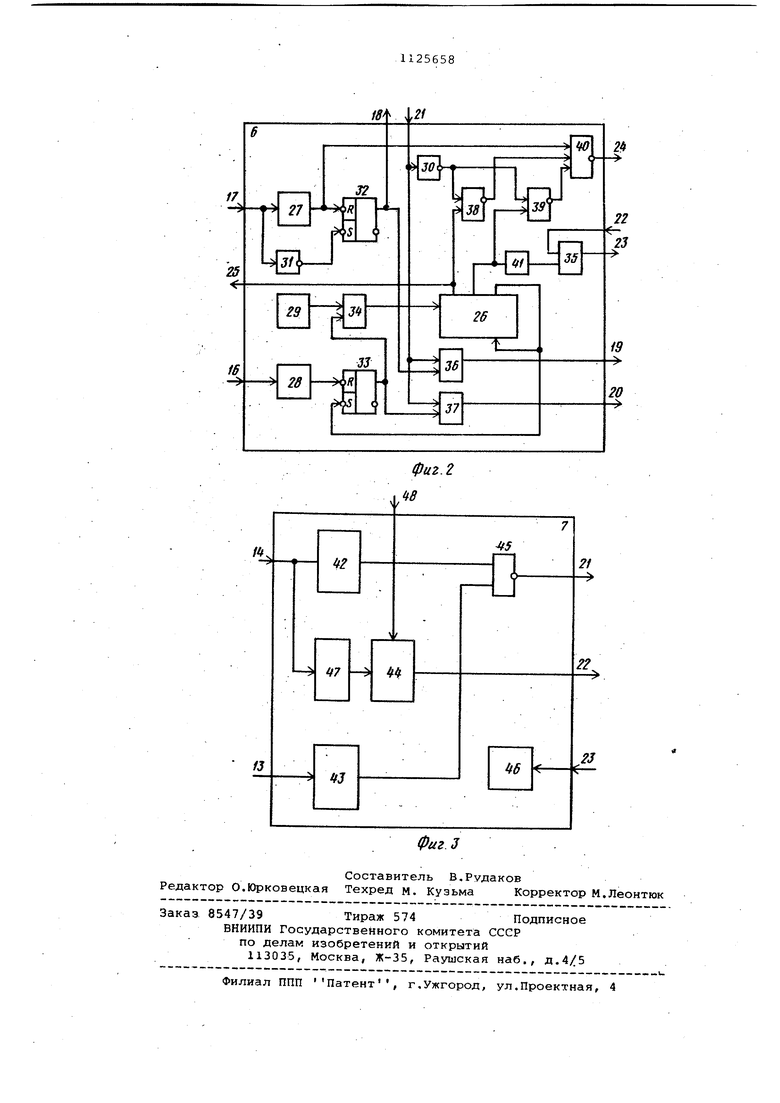

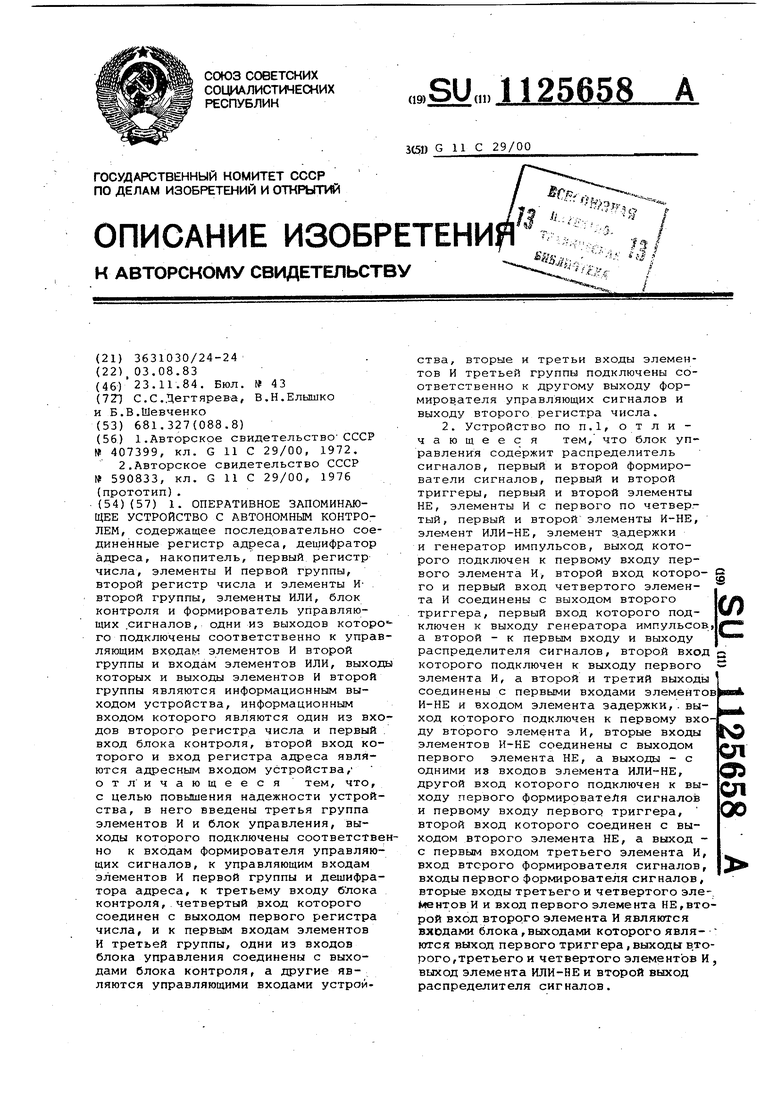

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Иэвестнр оперативное запоминакяцее устройство, содержащее накопитель . информации, адресный и числовой регистры, дешифратор адреса и усилители считывания, соединенные с накопителем и регистрами, блок контроля, регистры и логические элементы Однако в устройстве отсутствует защита информации от разрушений,вызванных неисправностями при передаче адресов и операндов. Наиболее близким к изобретению яв ляется оператив-ное запоминающее уст.ройство (ОЗУ) с защитой информации, содержащее накопитель, выходы которо го подключены к входам дополнительного регистра и регистра числа, а входы - к выходам дешифратора адреса, соединенного через регистр адреса с адресными шинами, блок обнаружения неисправностей, входы которого подключены к информационным и адресным шинамj блок коррекции режима, . входы которого подключены к выходу блока обнаружения неисправностей .и шинам записи и чтения, а выходы соответственно к входам элемента ИЛИ и первым входам элементов И, вторые входы одних элементов И соединены с выходами дополнительного регистра числа, а выходы - с входами формирователей записи, вторые входы других элементов И -соединены с выходами регистра числа, а выходы - с выходными шинами, соединенными с выходом элемента ИЛИ, входы дополнительного регистра подключены к выходам усилителей считывания С2 3. Однако в известном устройстве не производятся проверки исправности, на копителя и регистра числа, что снижа ет его надежность. Цель изобретения - повышение наде ности устройства. Поставленная цель достигается тем что в ОЗУ с автономным контролем, со держащее последовательно соединенные регистр адреса, дешифратор адреса, н копитель,, первый регистр числа, элементы И первой группы, второй регист числа и элементы И второй группы, эл менты ИЛИ, блок контроля и формирова тель управляющих сигналов, одни из выходов которого подключены соответственно к управляющим входам элементов И второй группы и входам элементов ИЛИ, выходы которых и выходы эле ментов И второй группы являются информационным выходом устройства, информационным входом которого являютс один из входов второго регистра числ и первый вход блока контроля, второй вход которого и вход регистра адреса являются адресным входом устройства, введены третья группа элементов И и блок управления, выходы которого подключены соответственно ; входам формирователя управляющих сигналов, . к управляющим входам элементов И первой группы и дешифратора адреса, к третьему входу блока контроля, четвертый вход которого соединен с выходом первого регистра числа, и к первым входам элементов И третьей группы, одни из входов блока управления соединены с выходами блок:а контроля, а другие являются управляющими входами устройства, вторые и третьи входы элементов И третьей группы подключены соответственно к другому выходу формирователя управляющих сигналов и выходу втррого регистра числа. Кроме того, блок управления содержит распределитель сигналов, первый и второй формирователи сигналов, первый и второй триггеры, первый и второй элементы НЕ, элементы И с первого по четвертый, первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, элемент задержки и генератор импульсов, выход которого подключен к первому входу первЪго элемента И, второй вход которого и первый вход четвертого элемента И соединены с выходом второт го триггера, первый вход которого подключен к выходу генератора импульсов, а второй - к первым входу и выходу распределителя сигналов, второй вход которого подключен к выходу первого элемента И, а второй и третий выходы соединены с первыми вхо-. Дс1ми элементов И-НЕ и входом элемента задержки, выход которого подключен к первому входу второго элемента И, вторые входы элементов И-НЕ соединены с выходом первого .элемента НЕ, а выходы - с одними из. входов элемента ИЛИ-НЕ, другой вход которо-. го подключен к выходу первого формирователя сигналов и первому входу I первого триггера, второй вход котрро го соединен с выходом второго элемента НЕ, а выход - с первым входом третьего элемента И, вход второго формирователя сигналов, входы первого - формирователя сигналов, вторые входы третьего и четвертого элементов И и вход первого элемента НЕ, второй вход второго элемента И являются входами блока, выходами которого являются выход первого триггера, выходы второго, третьего и четвертого элементов И, выход элемента ИЛИ-НЕ и второй выход распределителя сигналов. На фиг.1 представлена структурная схема предлагаемого устройства; иа фиг.2 и 3 - структурные схемы блока управления и блока контроля соответственно. Устройство содержит {фиг.1) накопитель 1, регистр 2 адреса, дешифратор : 3 адреса, первый регистр 4 числа, второй регистр 5 числа, блок б управления,, блок 7 контроля, форми рователь .8 управляющих сигналов, п вую 9, вторую 10 и третью 11 групп элементов И, элементы ИЛИ 12. Устройство имеет адресный 13 и информационный 14 входы, информационный выход 15 и управляющие взсоды 16 и являющиеся одними из входов блока имеющего выходы 18-20, другие входы 21 и 22 и выходы 23-25. Блок б управления (фиг.2) содер жит распределитель 26 сигналов, пер вый 27 и второй 28 формирователи си налрв, генератор 29 импульсов, элементы НЕ 3D и 31, триггеры 32 и 33 элементы И 34-37 с первого по четвертый, элементы И-НЕ 38 и 39, элемент ИЛИ-НЕ 40 и элемент 41 задержки. . ., . . Блок 7 контроля (фиг.З) содержит блоки ,42 и 43 сложения по Модул два, блок 44 поразрядного сравнения на шест надца ть ра эр ядов, элемен т ИЛИ-НЕ 45, элемент 46 индикации, третий регистр 47 числа и информационный вход 48. Устройство работает следующим об разом. По адресу, поступившему на регистр 2 адреса независимо от исправности передачи и накопителя .1, а также вида обращения (запись или считывание), из накопителя 1 выбирается информация, которая устанавливается в режиме считывания на регистрах 4 и 5. При считывании сигнал Чтение преобразуется формирователем 27 в/ отрицательный.импульс, который через элемент ИЛИ-НЕ 40 поступает на дешифратор 3 и одновременно на триггер 32, формирующий положительный потенциал поступающий на элемент И 36 и в регистр 5 числа через элементы И 9, разрешая перепись числа из регистра 4 в регистр 5. При исправной передаче, которая контролируется блоком 7f в режиме считывания информация из регистра 5 числа через элементы И 10 поступает на выход 15. В режиме записи информация по .входу 14 поступает в регистр 5 числ а из него через элементы И 11 - в на питель 1 и далее в регистр 4, Записанный код поступает из регистра 4 в блок 7, где сравнивается с кодом, поступающим по входу 14, контролируя таким образом исправность ячеек памяти адреса, в которой ведется запись информации. Блок 6 управления в режиме запис работает следующим образом. Сигнал Запись, поступающий на вход 16, преобразуется в .отрицательный импульс формирователем 28. и поступает на вход триггера 33, который формирует положительный -потенциал, поступающий на входы элементов И 34 и 37. Импульс с генератора 29 поступает на другой вход элемента И 34 и далее на вход распределителя 26, который реализует следующий алгоритм записи. Формирование сигна.ла Разрешение записи ( с выхода 25 блока б) в накопитель 1 и сигнала Выбор кристалла (выход 24) идет непосредственное выхода.распределителя 26.Сигнал поступает на вход элемента И-НЕ 38 , который в отсутствие сигнала Ошибинвертирует сигка при передаче I нал Разрешение записи в накопителе 1, и через элемент ИЛИ-НЕ 40 формируется сигнал, поступающий на дешифратор 3 адреса. Таким образом производителя запись числа в накопитель 1. Для формирования сигнала Выбор кристалла сигнал с выхода распределителя 26. поступает на вход элемента И-НЕ 39, с его выхода при отсутствий сигнала Ошибка при передаче - на вход элемента ИЛИ-НЕ 40. Через элемент 41 задержки сигнал с выхода распределителя 26 поступает также на вход элемента И 35, который при несоответствии кодов формирует сигнал Не годен, поступающий в блок 7. . В том случае, когда в режиме считывания происходит искажение адреса при передаче, сигнал с входа. 17 передается формирователем 8 на входы элементов ИЛИ 12 и элементов И 11. В результате срабатывания элементов ИЛИ 12 на выход 15 из ОЗУ выдается операнд, являющийся кодом арифметической единицы, в котором нарушено соответствие между информаг ионной и контрольной частями. В результате срабатывания элементов И 9 в накопителе 1 восстанавливается содержимое искаженного адреса. Если искажение адреса или one- ранда происходит в режиме записи, то формирователем 8 блокируется заг пись. операнда. Б том случае, когда в- режиме записи правильно передан и адрес и операнд, информация, записанная в накопитель 1, поступает в блок 7, где сравнивается с поданной на вход 14. Если обнаруживается несоответствие, то в блок б управления поступает; сигнал Ответ сравнения, а . из него - сигнал Не годен, который в дальнейшем может быть использован для оценки состояния накопителя 1, а также для переадресации информации.

Техническое преимущество изобретения заключается в том, что надежность устройства возрастает без увеличения оборудования.

При примененйи предлагаемого ОЗУ в системах контроля введение самоконтроля накопителя повьаиает достоверность выдачи результата, так как при занесении в процессе контроля всех результатов контроля в ОЗУ для последукицей регистрации или индикации коэффициент важности отказа накопителя равен единице.

Основным достоинством ОЗУ является то, что информация в нем защи-. щена от разрушения вследствие неверно переданных адресов и операндов, и при зтом в процессе записи контролируется исправность 100 % ячеек накопителя, в которых производится запись информации, что особенно важно в -ОЗУ контрольно-измерительных систем, работающих в реальном масштабе времени, к которым предъявляются- повышенные требования по надежности .

фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство для управления памятью | 1980 |

|

SU962963A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Запоминающее устройство с контролем информации при записи | 1985 |

|

SU1262574A2 |

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее последовательно соединенные регистр адреса, дешифратор адреса, накопитель, первый регистр числа, элементы И первой группы, второй регистр числа и элементы Ивторой группы, элементы ИЛИ, блок контроля и формирователь управляющих .сигналов, одни из выходов которо го подключены соответственно к управляющим входам элементов И второй группы и входам элементов ИЛИ, выходы которых и выходы элементов И второй группы являются информационным выходом устройства, информационным входом которого являются один из входов второго регистра числа и первый вход блока контроля, второй вход которого и вход регистра адреса являются адресным входом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены третья группа элементов И и блок управления, выходы которого подключены соответственно к входам формирователя управляющих сигналов, к управляющим входам элементов И первой группы и дешифратора адреса, к третьему входу блока контроля, четвертый вход которого соединен с выходом первого регистра числа, и к первым входам элементов И третьей группы, одни из входов блока управления соединены с выходами блока контроля, а другие являются управляющими входами устройства, вторые и третьи входы элементов И третьей группы подключены соответственно к другому выходу формирователя управляющих сигналов и выходу второго регистра числа. 2. Устройство ПОП.1, отличающееся тем, что блок управления содержит распределитель сигналов, первый и второй формирователи сигналов, первый и второй триггеры, первый и второй элементы НЕ, элементы И с первого по четвертый, первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, элемент задержки и генератор импульсов, выход которого подключен к первому входу первого элемента И, второй вход которо- с ш (Л го и первый вход четвертого элемента И соединены с выходом второго триггера, первый вход которого подключен к выходу генератора импульсов, а второй - к первым входу и выходу распределителя сигналов, второй вход д которого подключен к выходу первого 5 элемента И, а второй и третий выходы соединены с первыми входами элементов; И-НЕ и входом элемента задержки,. выход которого подключен к первому вхо ду второго элемента И, вторые входы элементов И-НЕ соединены с выходом первого элемента НЕ, а выходы - с одними из входов элемента ИЛИ-НЕ, другой вход которого подключен к выходу первого формирователя сигналов и первому входу первого триггера, второй вход которого соединен с выходом второго элемента НЕ, а выход с первым входом третьего элемента И, вход второго формирователя сигналов, входы первого формирователя сигналов, вторые входы третьего и четвертого эле-. Ментов И и вход первого элемента НЕ,второй вход второго элемента И являются входами блока, выходами которого явля- ются выход первого триггера,выходы в.торого,третьего и четвертого элементов И , выход элемента ИЛИ-НЕ и второй выход распределителя сигналов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-11-23—Публикация

1983-08-03—Подача