Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении репрограмми- руемых ПЗУ со стиранием информации.

Целью изобретения является расширение функциональных возможностей устройства за счет оперативной смены контрольных разрядов в циклах записи.

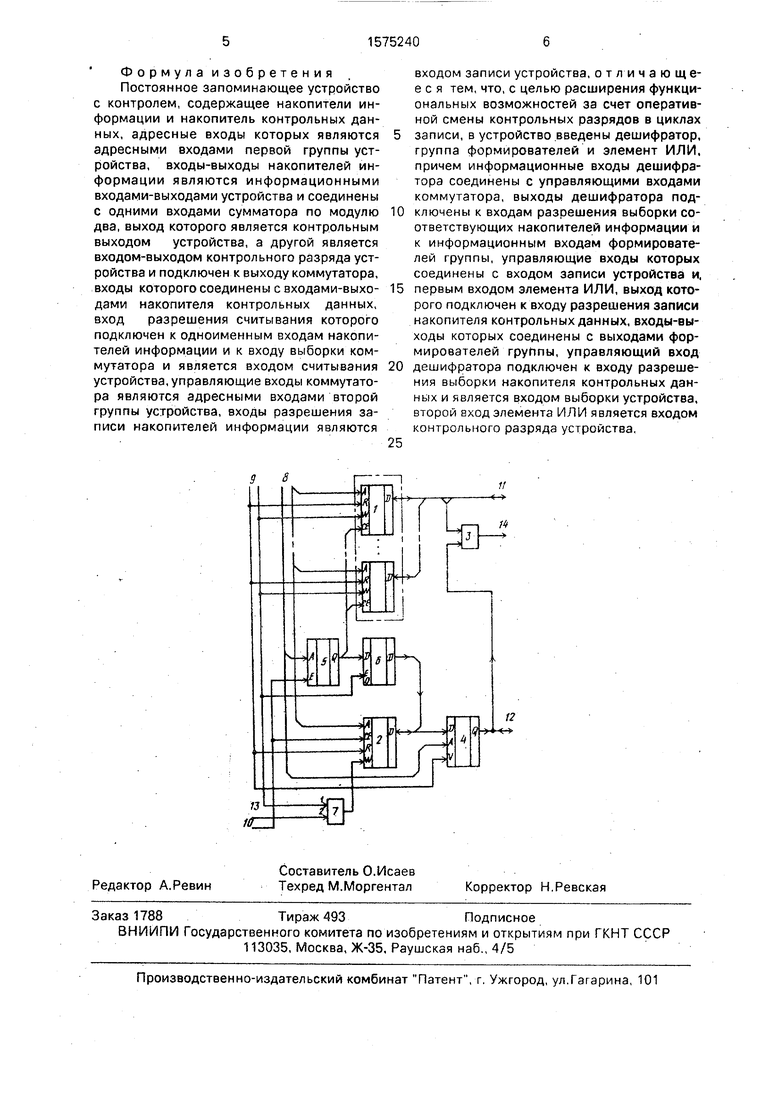

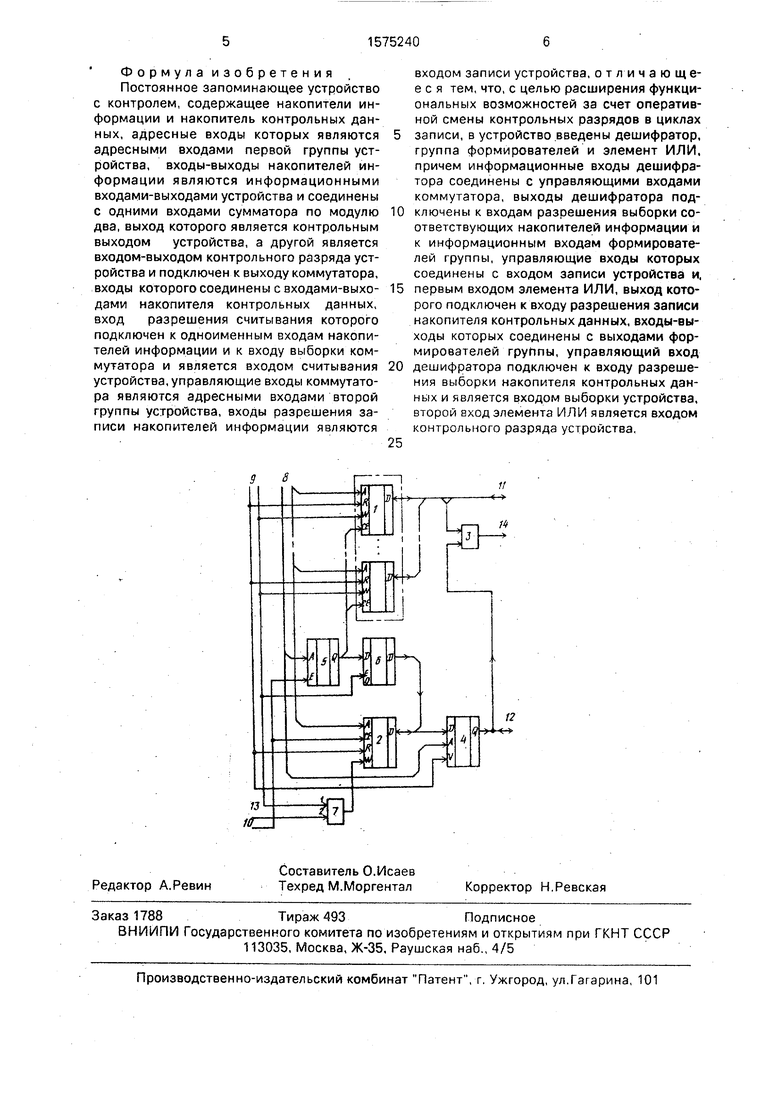

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит М накопителей 1 информации (каждый со структурой 2m x N), образующих ПЗУ емкостью М х 2т слов х N рязрядов, накопитель 2 контрольных данных со структурой 2т слов х М разрядов, сумматор 3 по модулю два на N+1 входов, коммутатор 4, дешифратор 5, группу формирователей 6, элемент ИЛИ 7, адресные входы 8, входы 9 записи и чтения, вход 10 выборки, информационные входы-выходы 11, вход-выход 12 контрольного разряда, вход 13 контрольного разряда и контрольный выход 14.

Так как М целесообразно выбирать равным степени числа 2, а N как правило, кратно 8, то при М N обеспечивается полное использование информационной емкости микросхем, образующих накопитель 2. Действительно, при структуре накопителя 2х /2т х М он будет построен из M/N микросхем со структурой 2т х N.

При М N и применении для накопителя 2 микросхем со структурой 2mxN используется M/N-я часть их емкости. Но так как N - величина ограниченная, то количество случаев использования, при которых

М N, значительно меньше количества случаев, при которых М N и, следовательно, полное использование информационной емкости обеспечивается в большинстве случаев.

Устройство работает следующим образом.

Старшие logaM разрядов кода адреса, поступающего на адресные входы 8, обеспечивают с помощью дешифратора 5 выбор одного из накопителей 1, младшие m разрядов выбирают слов а в каждом из накопителей 1 и накопителе 2. Ячейки (разряды) всех слов накопителей 1 и 2 после стирания находятся в единичном состоянии.

В режиме записи, определяемом соответствующими потенциалами на входах 9 записи и чтения, информационный код по- сгупает с информационных входов 11 на информационные входы накопителей 1 и входы сумматора 3. При работе с внешним контрольным разрядом он поступает на входы 12 и 13 контрольного разряда, на вход сумматора 3 и на вход элемента ИЛИ 7. На контрольном выходе 14 формируется признак исправного (неисправного) приема информации. При единичном уровне контрольного разряда сигнал с выхода элемента ИЛИ 7 запрещает запись информации в накопитель 2 контрольных данных. Поэтому ячейки накопителя 2, соответствующие младшим m разрядам адреса ячейкам выбранного накопителя 2, останутся в единичном состоянии. При нулевом уровне контрольного разряда разрешается запись в накопителе 2, в который запишется (при подаче разрешающего сигнала на вход 10) нулевой уровень разряда кодовой комбинации, проходящей с выхода дешифратора 5 через открытые в режиме записи формирователи 6. В этой кодовой комбинации имеется лишь один О, соответствующий нулевому значению контрольного .разряда и выбранному (одному из М) накопителю 1. Этот О запишется в ячейку накопителя 2 по выбранному адресу. Остальные 1 кодовой комбинации не изменят состояние других ячеек данного адреса накопителя 2.

В режиме считывания разрешается работа коммутатора 4, который (в соответствии с поступающим на его адресную шину кодом адреса) осуществляет выбор контрольного разряда, считываемого из накопителя 2 и соответствующего слову, считываемому из одного из накопителей 1, Выбор накопителя 1 производится дешифратором 5. Считываемое слово и его контрольный разряд поступают (при подаче разрешающего сигнала на вход 10) в сумматор 3, на выходе которого и, следовательно, на контрольном выходе 14 вырабатывается признак исправности.

Если после стирания в накопителях 1 и

2 устанавливаются О, то выходы формирователя 6 должны быть инвертирующими, а контрольный разряд со входа 13 контрольного разряда на вход элемента ИЛИ 7 должен поступать через инвертор. В этом

случае единичное значение контрольного разряда разрешает запись в накопитель 2 и кодовая комбинация с выходов формирователей 6, содержащая одну 1, записывается в накопитель 2. Нулевое значение контрольного разряда запрещает запись в накопитель 2, и в его соответствующей ячейке сохраняется О.

При работе без контрольного разряда

входного информационного кода сохраняется возможность контроля сохранности информации. Для этого контрольный выход 14 соединяют со входом 13 контрольного разряда. В режиме записи информации сумматор 3 формирует контрольный разряд для кода информации, поступающего на информационные входы 11. На выходе коммутатора 4 при этом - постоянный потенциал, не мешающий формированию контрольного

разряда. С контрольного выхода 14 контрольный разряд поступает на вход элемента ИЛИ 7. В дальнейшем работа устройства в режиме записи и считывания происходит аналогично работе устройства при наличии

внешнего контрольного разряда. Возникающий в режиме считывания на контрольном выходе 14 и поступающий на вход элемента ИЛИ 7 сигнал, характеризующий исправность или неисправность считываемой информации, не влияет на режим работы блока 2, так как он (сигнал) блокирован сигналом режима на втором входе элемента ИЛИ 7.

Таким образом, сумматор 3 обеспечивает:

при наличии внешнего контрольного разряда контроль принимаемой информации в режиме записи и контроль считываемого кода в режиме считывания;

при отсутствии внешнего контрольного разряда формирование его в режиме записи и контроль информационного кода в режиме считывания.

У предлагаемого устройства (по сравнению с прототипом) расширены функциональные возможности (за счет организации оперативной перезаписи контрольной информации), что позволяет полностью использовать информационный объем контрольного накопителя.

Формула изобретения Постоянное запоминающее устройство с контролем, содержащее накопители информации и накопитель контрольных данных, адресные входы которых являются адресными входами первой группы устройства, входы-выходы накопителей информации являются информационными входами-выходами устройства и соединены с одними входами сумматора по модулю два, выход которого является контрольным выходом устройства, а другой является входом-выходом контрольного разряда устройства и подключен к выходу коммутатора, входы которого соединены с входами-выходами накопителя контрольных данных, вход разрешения считывания которого подключен к одноименным входам накопителей информации и к входу выборки коммутатора и является входом считывания устройства, управляющие входы коммутатора являются адресными входами второй группы устройства, входы разрешения записи накопителей информации являются

0

5

0

5

входом записи устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет оперативной смены контрольных разрядов в циклах записи, в устройство введены дешифратор, группа формирователей и элемент ИЛИ. причем информационные входы дешифратора соединены с управляющими входами коммутатора, выходы дешифратора подключены к входам разрешения выборки соответствующих накопителей информации и к информационным входам формирователей группы, управляющие входы которых соединены с входом записи устройства и. первым входом элемента ИЛИ, выход которого подключен к входу разрешения записи накопителя контрольных данных, входы-выходы которых соединены с выходами формирователей группы, управляющий вход дешифратора подключен к входу разрешения выборки накопителя контрольных данных и является входом выборки устройства, второй вход элемента ИЛИ является входом контрольного разряда устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Оперативное запоминающее устройство с коррекцией информации | 1983 |

|

SU1111206A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1336122A1 |

| Оперативное запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1089628A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1735907A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении репрограммируемых ПЗУ со стиранием информации. Целью изобретения является расширение функциональных возможностей устройства за счет оперативной смены контрольных размеров в циклах записи. Устройство содержит M накопителей информации со структурой 2M слов xN разрядов, образующих ПЗУ емкостью Мх 2M слов xN разрядов, накопитель контрольных данных со структурой 2M слов хМ разрядов, сумматор по модулю два на N+1 входов, коммутатор, дешифратор, группу формирователей и элемент ИЛИ. Цель изобретения достигается тем, что запись в накопитель контрольных данных, предварительно подвергнутый стиранию, производится (или не производится) в зависимости от значения контрольного разряда. При этом в накопитель контрольных данных записывается выходная кодовая комбинация дешифратора разрядов адреса, осуществляющего одновременно выбор одного из основных накопителей. 1 ил.

| Авторское свидетельство СССР № 913455, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-06-30—Публикация

1988-05-13—Подача