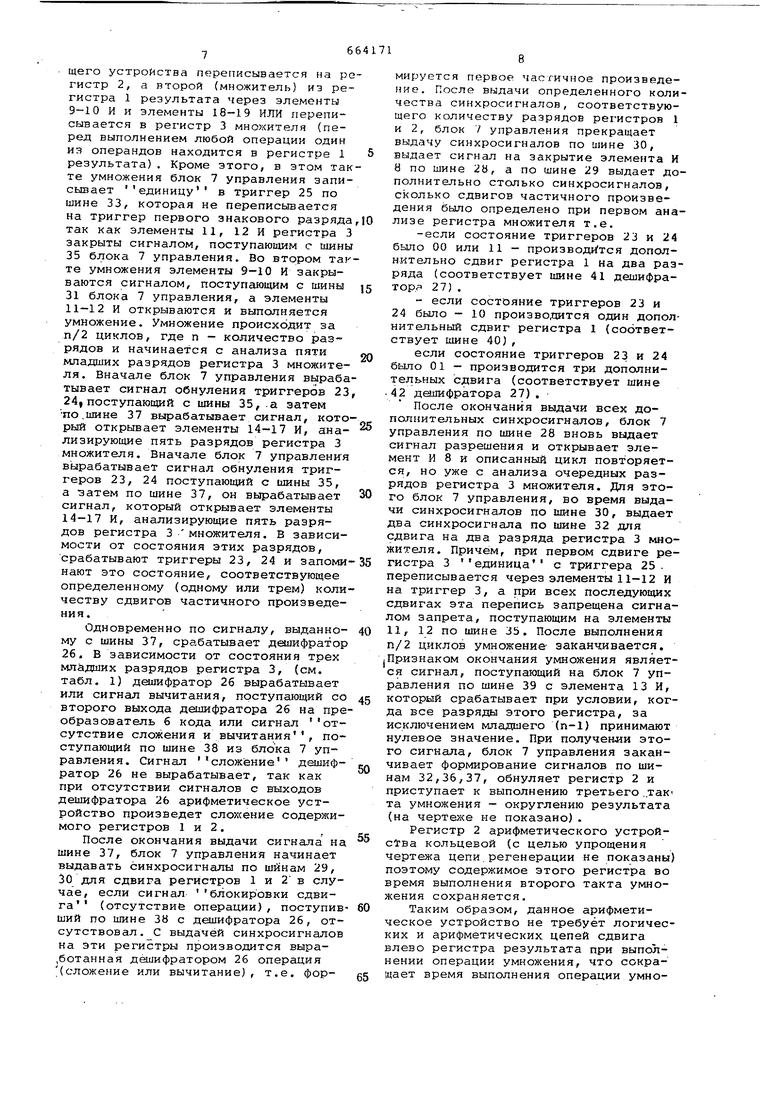

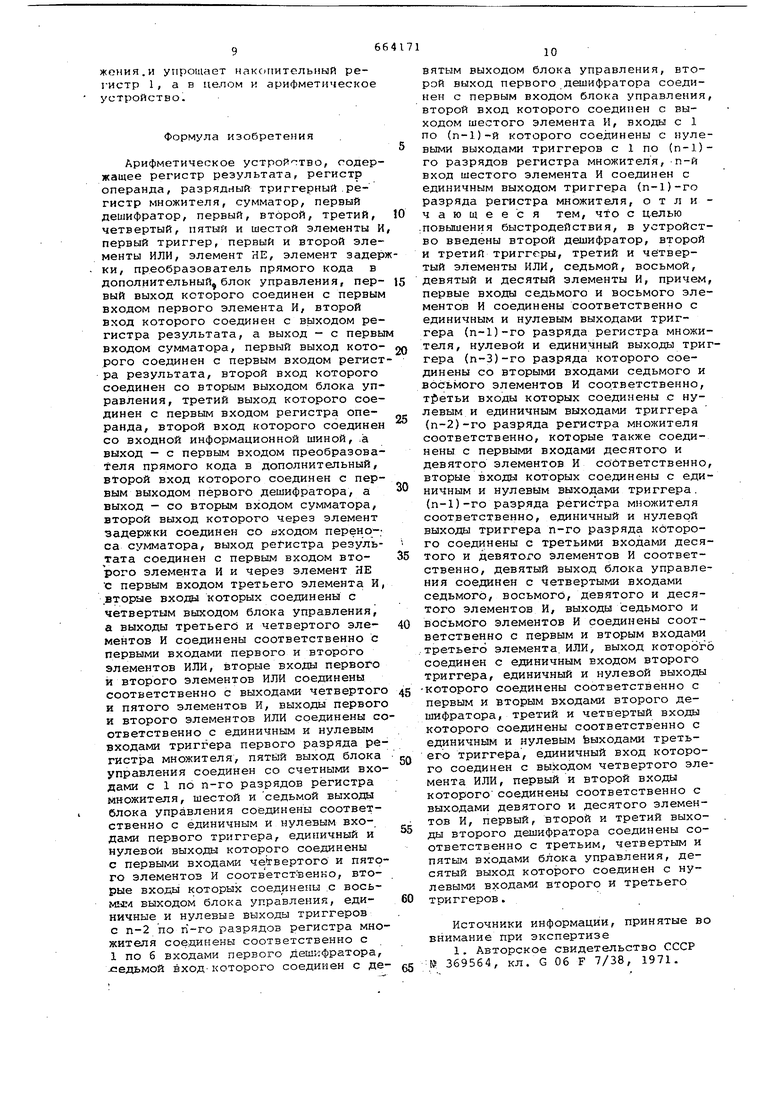

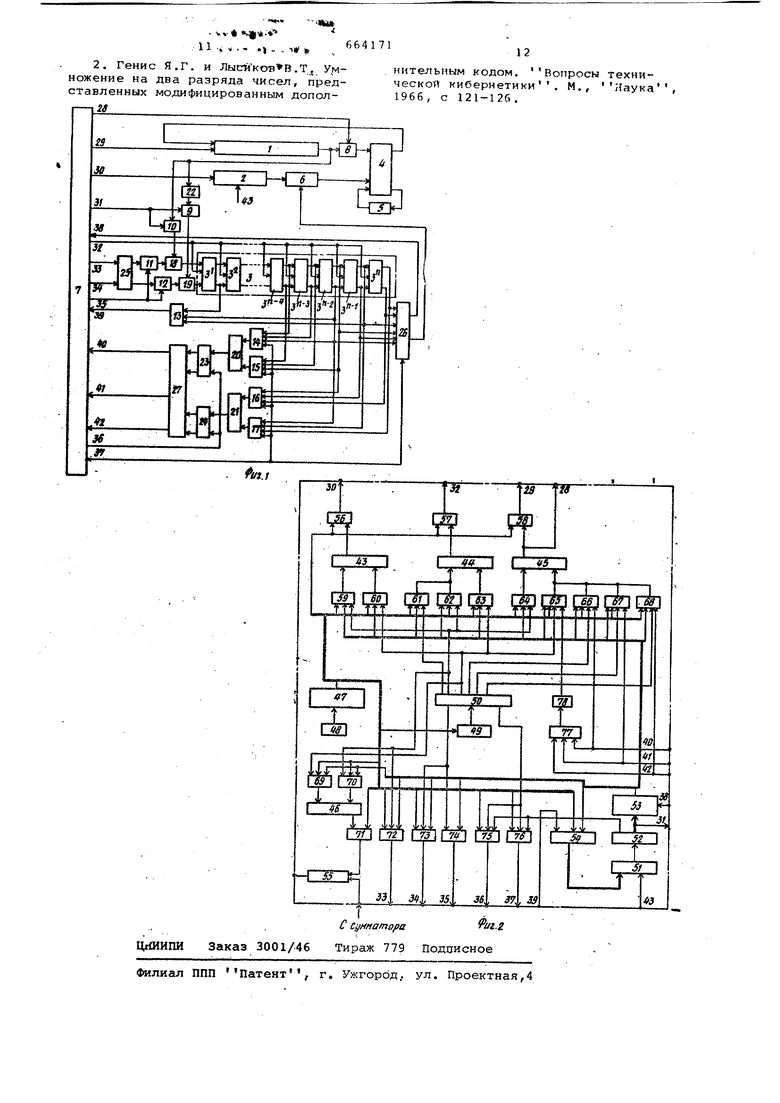

Изобретение относится к области вычислительной техники и может быть использовано при разработках универсальных и специализированных вычислительных машин . Известно арифметическое устройств во с сумматором накапливающего типа, в котором при выполнении операции умножения совмещаются по времени эле ментарные операции формирования частичного результата произведения и сдвига его на один разряд вправо 1 Недостатком известного устройства является его низкое быстродействие. Наиболее близким по технической сущности к данному изобретению является устройство 2, содержащее ре гистр результата, регистр операнда, разрядный триггерный регистр множителя, сумматор, первый дешифратор, первый, второй, . третий, четвертый, пятый и шестой элементы И, первый триггер, первый и второй элементы ИЛИ, элемент НЕ, элемент задержки, преобразователь прямого кода в допол нительный, блок управления, первый выход которого соединен с первым вхо дом первого элемента И, второй вход которого соединен с выходом регистра результата, а выход - с первым входом сумматора, первый выход которого соединен с первым входом регистра :результата, второй вход которого соединен со вторым выходом блока управления, третий выход которого -соединен с первым входом регистра операнда, второй вход которого соединен со входной информационной шиной, а выход - с первым входом преобразователя прямого кода в дополнительный, второй вход которого соединен с первым выходом первого дешифратора, а выход - со вторьям BkoflOM сумматора, второй выход которого через элемент задержки соединен со входом переноса сумматора, выход регистра результата соединение первым входом второго элемента И и через элемент НЕ с первым входом третьего элемента И, вторые входы которых соединены с четвертым выходом блока управления, а выходы третьего и четвертого элементов И соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы первого и, второго элементов ИЛИ соединены соответственно с выходами четвертого и пятого элементов И, выходы первого и второго элементов ИЛИ соединены соответjCTBeHHo с единичным и нулевым входами . триггера первого разряда регистра множителя, пятый выход блока управления соединен со счетньами входами с 1 по п-го разрядов регистра множител шестой и седьмой выходы блока управления соединены соответственно с еди ничньлм и нулевым входами первого триггера, единичный и нулевой выходы которого соединены с первыми входами четвертого и пятого элементов И соответственно, вторые входы которых соединены с восьмым выходом блока управления, единичные и нулевые выхо ды триггеров с п-2 по п-го разрядов регистра множителя соединены соответ ственно с 1 по б входами первого дешифратора, седьмой вход которого сое динён с девятым выходом блока управления, второй выход первого даиифратора соединен с первым входом блока управления, второй вход которого сое динен с выходом шестого элемента И, входы с 1 по (п-1)-й которого соединен с нулевыми выходами триггеров с 1 по (n-l)-ro разрядов регистра множителя, п-й вход шестого элемента И соединен с единичным выходом триг.гёра (n-l)-ro разряда регистра множи теля. Недостатком известного устройства является низкое быстродействие. Целью изобретения является повышение быстродействия, С этой целью в устройство введены второй дешифра тор, второй и третий триггеры, трети и четвертый элементы ИЛИ, седьмой, восьмой, девятый и десятый элементы И, причем, первые входы седьмого и восьмого элементов И соединены соответственно с единичным и нулевым вы.ходами триггера (п-1}-го разряда регистра множителя, нулевой и единичный выходы триггера (п-З)-го разряда которого соединены со вторыми входам седьмого и восьмого элементов И соот ветственно, третьи входы которых сое динены с нулевым и единичным выходами триггера {п-2)-го разряда регистpa множителя соответственно, которые также соединены с первыми входами десятого и девятого элементов И соответственно, вторые входы которых соединены с единичным и нулевым выходами триггера (п-1)-го разряда ре-ч гнстра множителя соответственно, единичный и нулевой выходы триггера п-го разряда которого соединены с третьими входами десятого и девятого элементов И соответственно, девятый выход блока управления соединен с. четвертыми входами седьмого,восьмого, девятого и десятого элементов И, выходы седьмого и восьмого элементов И соединены соответственно с первьм . и вторым входгили третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, единичный и нулевой выходы которого сое динены соответственно с первым и вто входами второго дешифргггора, третий и четвертый входы которого соединены соответственно с единичн1 м и нулевьлм вьлходами третьего триггера, единичный вход которого соединен с выходом четвертого элемента ИЛИ, первый и второй йходы которого соединены соответственно с выходами девятого и десятого элементов И, первый, второй и третий выходы второго дешифратора соединены соответственно с третьим, четвертым и пятым входами блока управления, десятый выход которого соединен с нулевыми входами второго и третьего триггеров. На фиг. 1 изображена функциональная схема арифметического устройства; на фиг. 2 - функциональная схема блока управления. Арифметическое устройство содержит регистр 1 результата, регистр 2 операнда, регистр 3 множителя,, триггеры 3- з регистра множителя, сумматор 4, элемент 5 задержки, преобразователь 6 прямого .кода в дополнительный f блок 7 управления, элементы и 8 - и 17, элементы ИЛИ 18 - ИЛИ 21, элемент ЙЕ 22, триггеры 23 - 25, первый и второй дешифраторы 26, 27, выходы 28-37 блока 7 управления, входы 38-42 блока 7 управления. Блок 7 управления содержит триггеры 43-46, блок 47 синхронизации, генератор 48, счетчик 49, дешифратор 50, регистр 51 кода операции, второй дешифратор 52, программная логическая матрица 53, шифратор 54, регистратор 55 номера команд, элементы И 56 - И 76, элемент ИЛИ 77 и элемент ЯВ 78.. Арифметическое устройство работает следукядим образом: при выполнении коротких операций типа Сложение в работе участвует регистр 1 результата, регистр 2 операнда и сумМатор 4, Регистр 1 результата служит для хранения одного из операндов выполняемой операции и для хранения результата выполненной операции. Регистр 2 операнда служит для хранения второго операнда. Информация на этот регистр пересылается из запоминающего устройства (на чертеже не показано) параллельным кодом. Содержимое обоих регистров последовательно, раЗ ряд за разрядом, поступает на сумматор 4, с помощью которого производи-тся необходимая операция, а результат выполненной операции записывается в регистр 1 результата. Сдвигающие синхросигналы на регистры I и 2 поступают из устройства 7 управления по шинам 29 и 30 соответственно. Преобразователь б кода преобразует прямой код числа, записанного на регистре 2 операнда, в дополнительный в случае выполнения команды

вычитание, поступаганей из блока 7 управления (на чертеже не показано) и команды вьтаитание, поступающей с выхода дешифратора 26 регистра 3 множителя. (Отрицательные числа представлены дополнительным кодом, что сокращает время выполнения операций сложения и вычитания).

При вьтолнении команды умножения используется регистр 3 множителя. Операция умножения также выполняется над числами, представленными дополнительным кодом с использованием метода умножения на два разряда множителя. Для исключения сдвигов влево частичного произведения после анализа каждой триады регистра множителя, анализируются не три разряда регистра 3 множителя, а пять.

Это позволяет определить общее количество сдвигов вправо частичного произведения, включая сдвиг влево на один разряд после анализа очередных разрядов регистра множителя и сдвига вправо на один разряд после его вычисления.

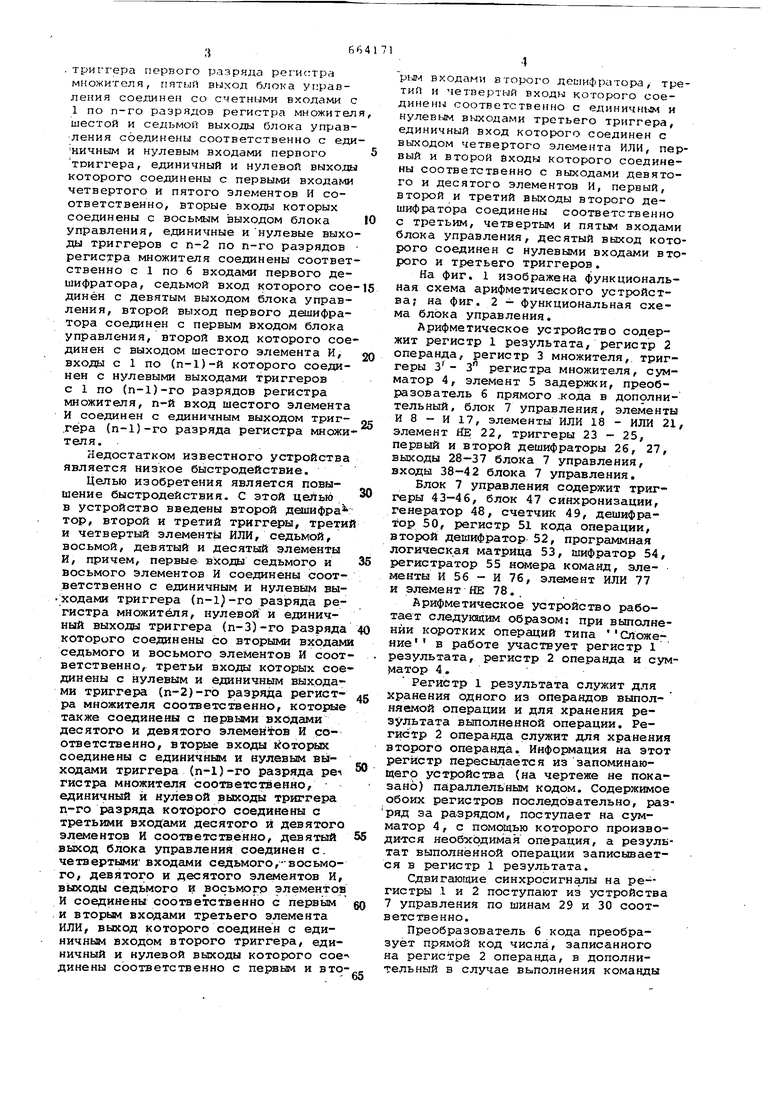

Таблица 1

о о

О

о

Продолжение табл.1

10

Алгоритм умножения имеет вид:

1. Расшифровать 5 разрядов (четыре младших и один свер1хмладший) ре-гистра множителя и произвести сложение (или вычитание) согласно табл. 1.

2.Сдвинуть частичное произведение -на один, два или три разряда согласно табл. 2.

3, Сдвинуть в регистре множителя информацию на два разряда вправо. (Пункты 1-3 повторить п/2 раз).

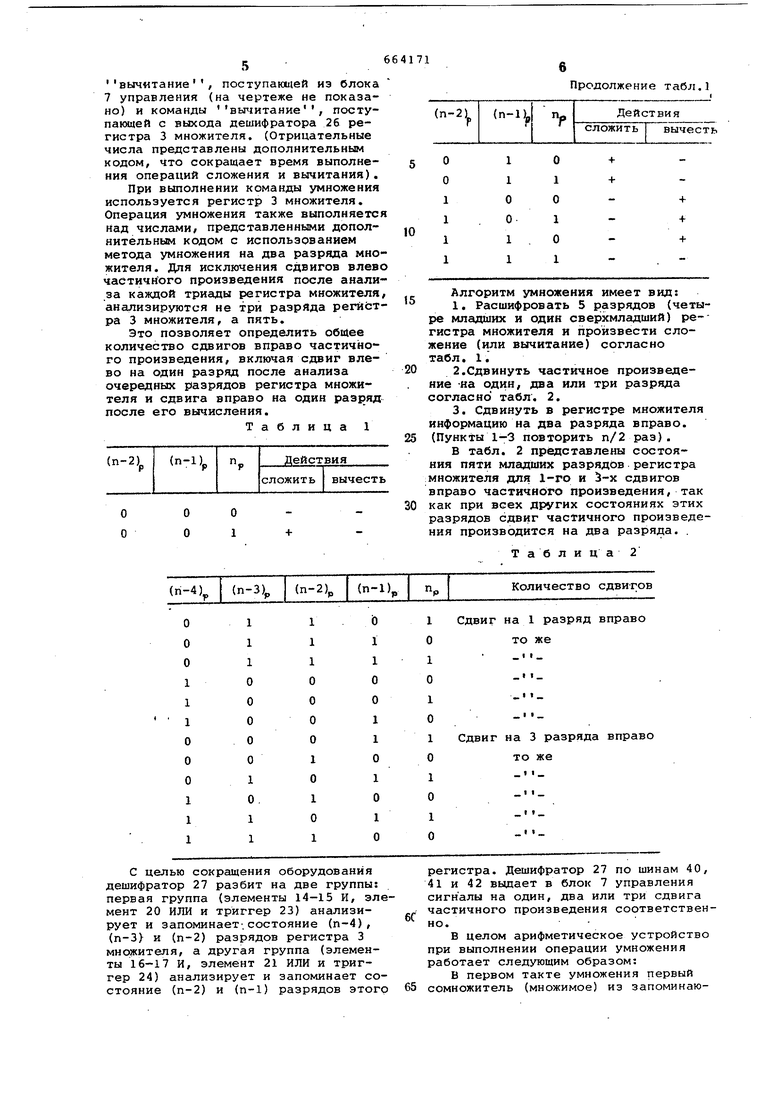

В табл. 2 представлены состояния пяти младших разрядов регистра множителя для 1-го и 3-х сдвигов вправо частично го произведения, так как при всех других состояниях этих разрядов сдвиг час ичного произведения производится на два разряда.

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

1 1 1 о о о о 1 о 1 о 1

1

1

1

о

о

о

о

о

1

о,

1

1

С целью сокращения оборудования дешифратор 27 разбит на две группы: первая группа (элементы 14-15 И, элемент 20 ИЛИ и триггер 23) анализирует и запоминаетсостояние (п-4), (п-3 и (п-2) разрядов регистра 3 множителя, а другая группа (элементы 16-17 и, элемент 21 ИЛИ и триггер 24) анализирует и запоминает состояние (п-2) и (п-1) разрядов этого

Сдвиг на 1 разряд вправо

1

о 1 о 1 о 1 о 1 о 1 о

то же I I

«I -

Сдвиг на 3 разряда вправо

то же I 1

1 I I I 1

регистра. Дешифратор 27 по шинам 40, 41 и 42 выдает в блок 7 управления сигналы на один, два или три сдвига частичного произведения соответственно.

В целом арифметическое устройство при выполнении операции умножения работает следующим образом:

В первом такте умножения первый сомножитель (множимое) из запоминающего устройства переписывается на ре гистр 2, а второй (множитель) из регистра 1 результата через элементы 9-10 И и элементы 18-19 ИЛИ переписывается в регистр 3 множителя (перед выполнением любой операции один из операндов находится в регистре 1 результата). Кроме этого, в этом так те умножения блок 7 управления записывает единицу в триггер 25 по шине 33, которая не переписывается на триггер первого знакового разряда так как элементы 11, 12 И регистра 3 закрыты сигналом, поступающим с шины 35 блока 7 управления. Во втором так те умножения элементы 9-10 И закрываются сигналом, поступающим с шины 31 блока 7 управления, а элементы 11-12 И открываются и выполняется умножение. Умножение происходит за п/2 циклов, где п - количество разрядов и начинается с анализа пяти младших разрядов регистра 3 множителя. Вначале блок 7 управления выраба тывает сигнал обнуления триггеров 23 24| поступающий с шины 35,.а затем по.шине 37 вырабатывает сигнал, кото рый открывает элементы 14-17 И, анализирующие пять разрядов регистра 3 множителя. Вначале блок 7 управления вырабатывает сигнал обнуления триггеров 23, 24 поступающий с шины 35, а затем по шине 37, он вырабатывает сигнал, который открывает элементы 14-17 И, анализирующие пять разрядов регистра 3 множителя. В зависимости от состояния этих разрядов, срабатывают триггеры 23, 24 и запоми нают это состояние, соответствующее определенному (одному или трем) коли честву сдвигов частичного произведения. Одновременно по сигналу, выданному с шины 37, срабатывает дешифратор 26. В зависимости от состояния трех младших разрядов регистра 3, (см. табл. 1) дешифратор 26 вырабатывает или сигнал вычитания, поступающий со второго выхода дешифратора 26 на пре образователь 6 кода или сигнал отсутствие сложения и вычитания , поступающий по шине 38 из блока 7 управления. Сигнал сложение дешифратор 26 не вырабатывает, так как при отсутствии сигналов с выходов дешифратора 26 арифметическое устройство произведет сложение содержимого регистров 1 и 2. После окончания выдачи сигнала на шине 37, блок 7 управления начинает выдавать синхросигналы по шинам 29, 30 для сдвига реги стров 1 и 2 в случае, если сигнал блокировки сдвига (отсутствие операции), поступив ший по шине 38 с дешифратора 26, отсутствовал .С выдачей синхросигналов на эти регистры производится выра,ботанная дешифратором 26 операция (сложение или вычитание), т.е. формируется первое частичное произведение. После выдачи определенного количества синхросигналов, соответствующего количеству разрядов регистров 1 и 2, блок 7 управления прекращает выдачу синхросигналов по шине 30, выдает сигнал на закрытие элемента И а по шине 28, а по шине 29 выдает дополнительно столько синхросигналов, сколько сдвигов частичного произведения было определено при первом анализе регистра множителя т.е. -если состояние триггеров 23 и 24 было 00 или 11 - производится дополнительно сдвиг регистра 1 на два разряда (соответствует шине 41 дешифратора 27) . - если состояние триггеров 23 и 24 было - 10 производится один дополнительный сдвиг регистра 1 (соответствует шине 40), если состояние триггеров 23 к 24 было 01 - производится три дополнительных сдвига (соответствует шине 42 далифратора 27). После окончания выдачи всех дополнительных синхросигналов, блок 7 управления по шине 28 вновь выдает сигнал разрешения и открывает элемент И 8 и описанный цикл повторяется, но уже с анализа очередных разрядов регистра 3 множителя. Для этого блок 7 управления, во время выдачи синхросигналов по шине 30, выдает два синхросигнала по шине 32 дпя сдвига на два разряда регистра 3 множителя. Причем, при первом сдвиге регистра 3 единица с триггера 25. переписывается через элементы 11-12 И на триггер 3, а при всех последующих сдвигах эта перепись запрещена сигналом запрета, поступающим на элементы 11, 12 по шине 35. После выполнения п/2 циклов умножение заканчивается. Признаком окончания умножения является сигнал, поступающий на блок 7 управления по шине 39 с элемента 13 И, который срабатывает при условии, когда все разряды этого регистра, за исключением младшего (п-1) принимают нулевое значение. При получении этого сигнала, блок 7 управления заканчивает формирование сигналов по шинам 32,36,37, обнуляет регистр 2 и приступает к выполнению третьего ..так та умножения - округлению результата (на чертеже не показано). Регистр 2 арифметического устройства кольцевой (с целью упрощения чертежа цепи.регенерации не показаны) поэтому содержимое этого регистра во время выполнения второго такта умножения сохраняется. Таким образом, данное арифметическое устройство не требует логических и арифметических цепей сдвига влево регистра результата при выполнении операции умножения, что сокращает время выполнения операции умножония.и yiipouujGT накопительный регистр 1, а в целом к арифметическое устройство. Формула изобретения Арифметическое устроР тво, содер жащее регистр результата, регистр операнда, разрядный триггерный.регистр множителя, сумматор, первый дешифратор, первый, второй, третий, четвертый, пятый и шестой элементы И первый триггер, первый и второй элементы ИЛИ, элемент НЕ, элемент задер ки, преобразователь прямого кода в дополнительный блок управления, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом регистра результата, а выход - с первы входом сумматора, первый выход которого соединен с первым входом регист ра результата, второй вход которого соединен со вторым выходом блока управления, третий выход которого соединен с первым входом регистра операнда, второй вход которого соединен со входной информационной шиной, ,а выход - с первым входом преобразователя прямого кода в дополнительный, второй вход которого соединен с первым выходом первого дешифратора, а выход - со вторым входом сумматора, второй выход которого через элемент задержки соединен со входом переноса сумматора, выход ре1истра результата соединен с первым входом второго элемента И и через элемент НЕ с первым входом третьего элемента И вторые входы которых соединены с четвертым выходом блока управления, а выходы третьего и четвертого элементов И соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы первого и второго элементов ИЛИ соединены соответственно с выходами четвертого и пятого элементов И, выходы первого и второго элементов ИЛИ соединены со ответственно с единичным и нулевым входами триггера первого разряда регистра множителя, пятйй выход блока управления соединен со счетными входами с 1 по п-го разрядов регистра множителя, шестой и седьмой выходы блока управления соединены соответственно с единичным и нулевым входами первого триггера, единичный и нулевой выходы которого соединены с первыми входами четвертого и пятого элементов И соответственно, вторые входы которых соединены .с восьмы:л выходом блока управления, единичные и нулевые выходы триггеров с п-2 по п-го разрядов регистра множителя соединены соответственно с 1 по 6 входами первого дешифратора, седьмой вход- которого соединен с деВятым выходом блока управления, второй выход первого дешифратора соединен с первым входом блока управления, второй вход которого соединен с выходом шестого элемента И, входы с 1 по (п-1)-й которого соединены с нулевыми выходами триггеров с 1 по (n-l)го разрядов регистра множителя, п-й вход шестого элемента И соединен с единичным выходом триггера (п-1)-го разряда регистра множителя, отличающееся тем, что с ц.елью .повьшения быстродействия, в устройство введены второй дешифратор, второй и третий триггеры, третий и четвертый элементы ИЛИ, седьмой, восьмой, девятый и десятый элементы И, причем, первые входы седьмого и восьмого элементов И соединены соответственно с единичным и нулевым выходами триггера (п-1)-го разряда регистра множителя, нулевой и единичный выходы триггера (п-З)-го разряда которого соединены со вторыми входами седьмого и восьмого элементов И соответственно, третьи входы которых соединены с нулевым и единичным выходами триггера (п-2)-го разряда регистра множителя соответственно, которые также соединены с первыми входами десятого и девятого элементов И соответственно, вторые входы которых соединены с единичным и нулевым выходами триггера, (n-l)-ro разряда регистра множителя соответственно, единичный и нулевой выходы триггера п-го разряда которого соединены с третьими входами десятого и девятого элементов И соответственно, девятый выход блока управления соединен с четвертыми входами седьмого, восьмого, девятого и десятого элементов И, выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами третьего элемента. ИЛИ, выход которого соединен с единичным входом второго триггера, единичный и нулевой выходы которого соединены соответственно с первым и вторым входами второго дешифратора, третий и четввртый входы которого соединены соответственно с единичным и нулевым Ьыходами третьего триггера, единичный вход которого соединен с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами девятого и десятого элементов И, первый, второй и третий выходы второго дешифратора соединены соответственно с третьим, четвертым и пятьгм входами блока управления, десятый выход которого соединен с нулевыми входами второго и третьего триггеров. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 369564, кл. G 06 F 7/38, 1971.

Авторы

Даты

1979-05-25—Публикация

1976-10-18—Подача