Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах, к которым предъявляются требования повышенной надежности.

Цель изобретения - повышение надежности за счет обеспечения функционирования при отказах одноразрядных узлов суммирования.

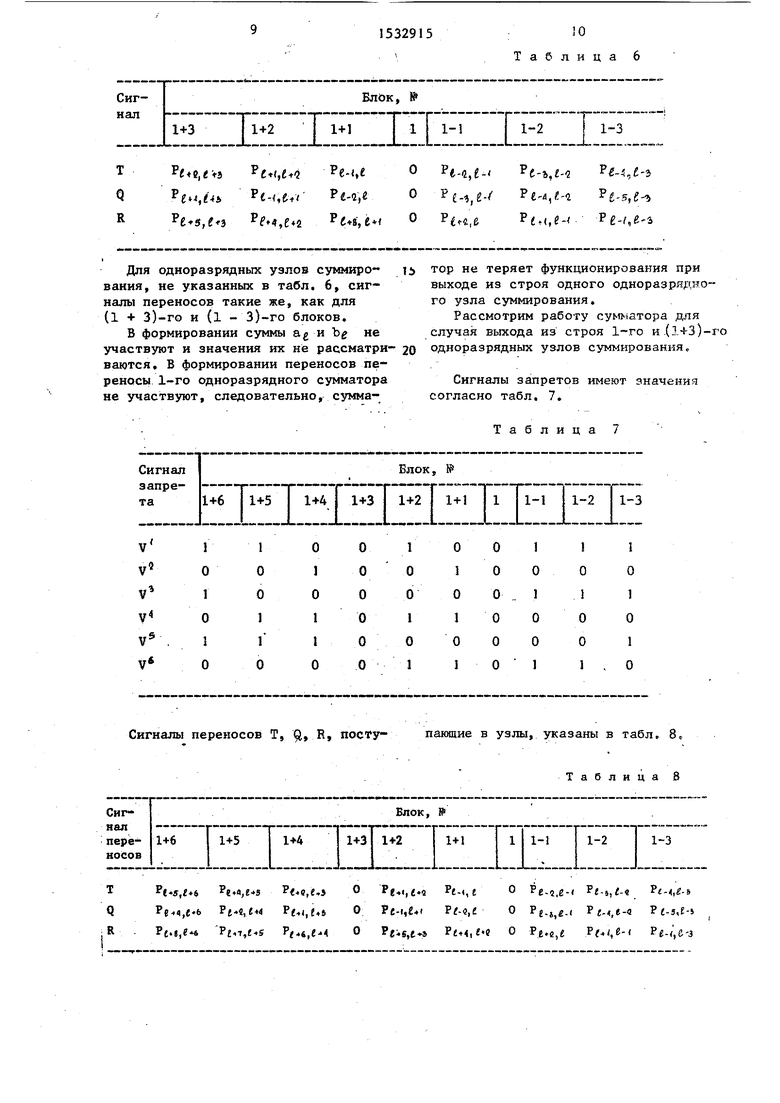

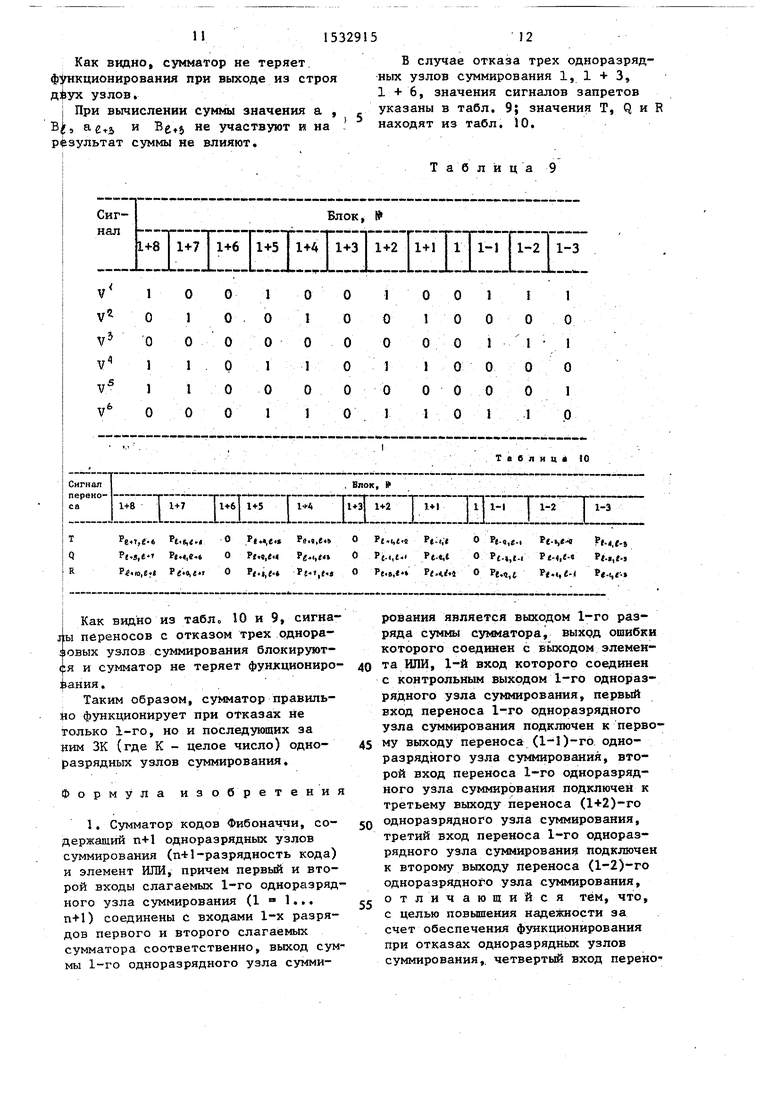

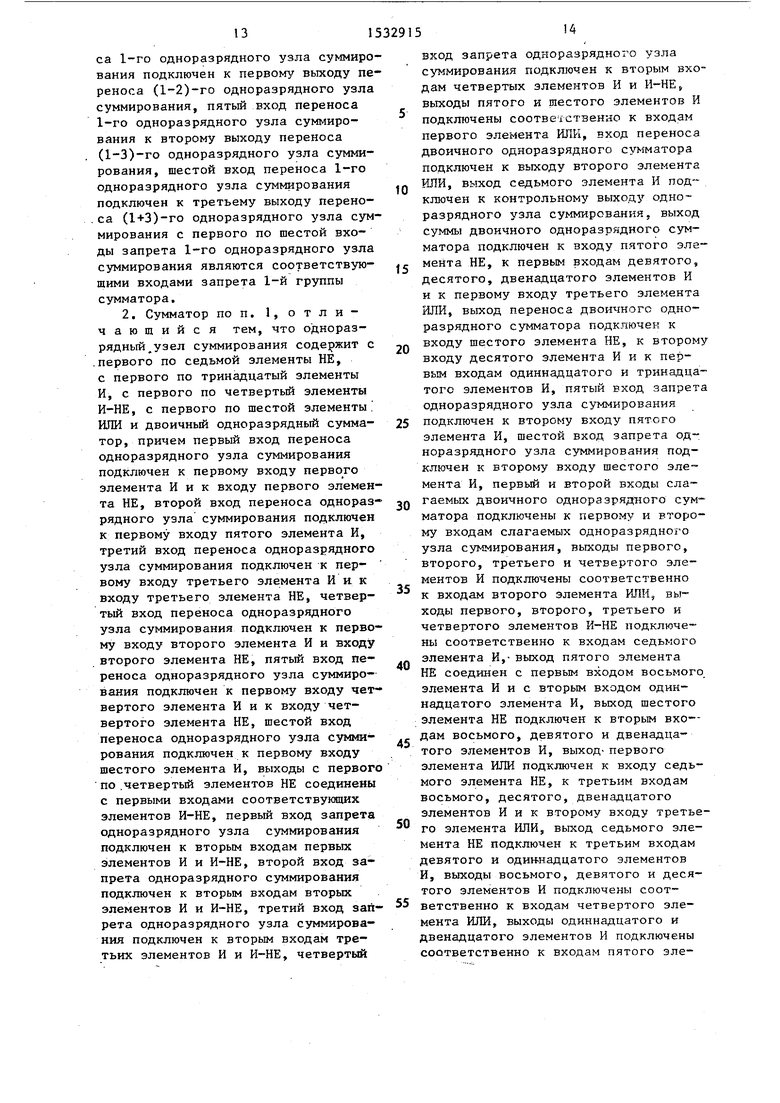

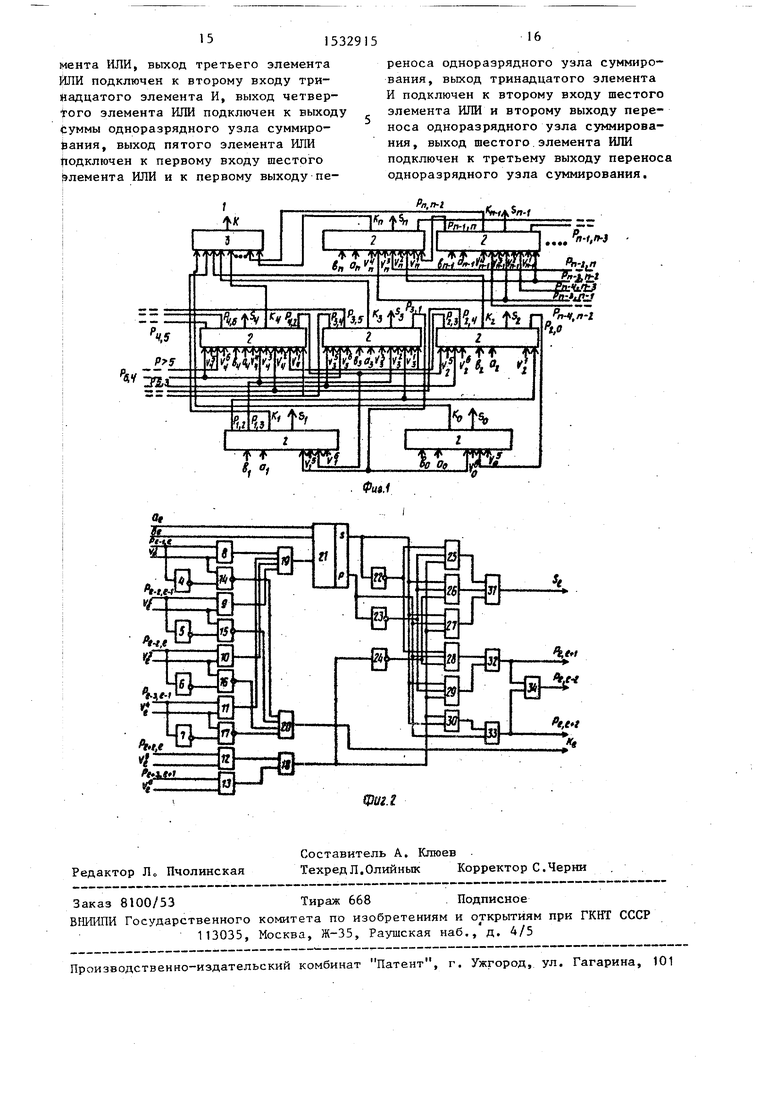

На фиг. 1 представлена схема сумматора кодов Фибоначчи; на фиг. 2 - схема одноразрядного узла суммирования.

Сумматор образуют выход 1 ошибки сумматора, (п + 1) одноразрядных узлов 2 суммирования и элемент ИЛИ 3.

Одноразрядный узел 2 суммирования содержит с первого по четвертый элементы НЕ 4 - 7, с первого по шестой элементы И 8 - 13, с первого по четвертый элементы 14-17, первый 18 и второй 19 элементы ИЛИ,

седьмой элемент И 20, двоичный одноразрядный сумматор 21, с пятого по седьмой элементы НЕ 22 - 24, с восьмого по двенадцатый элементы И 25 - 29, с третьего по пятый элементы ИЛИ 30 - 32, тринадцатый элемент И 33 и шестой элемент ИЛИ 34.

На фиг. 1 и 2 использованы следующие обозначения: ag и В - значения 1-х разрядов суммируемый чисел; Р; - значение переноса с 1-го ра зряда в j-й разряд; V/ - сигнал запрета Pg.e V v« - сигнал запрета Pf-«j,g- ; V/ - сигнал запрета 5 Vt сигнал запрета Pt.t.t ; V сигнал запрета v« сиг нал запрета , s сигнал суммы двоичного одноразрядного сумматора; Р - сигнал переноса двоичного одноразрядного сумматора; S - сигнал суммы одноразрядного узла суммирования; К - сигнал ошибки, которая следует от невозможности одно№

ел

со ю со

СП

временного появления переносов из (l - l)-ro и (l - 2)-го разрядов в JL-й в случае всех исправных одноразрядных узлов суммирования.

Незадействованные входы переноса и запрета одноразрядных узлов суммирования подключаются к потенциалу 0.

Сумматор работает следующим образом.

На входы элемента ИЛИ 3 поступает сигнал ошибки с каждого из одноразрядных узлов суммирования.

На выходе элемента ИЛИ 3 формируется сигнал о наличии ошибки К, На входы слагаемых сумматора поступают а, и В, коды Фибоначчи в нормальной форме о Формируются переносы в каждом одноразрядном узле суммирования, затем осуществляется суммирование переносов, образование второй промежуточной суммы и новых переносов. И так д тех пор, пока не прокатится образование переносов и на выходах узлов суммирования не образуется код суммы.

Функционирование 1-го одноразрядного узла суммирования

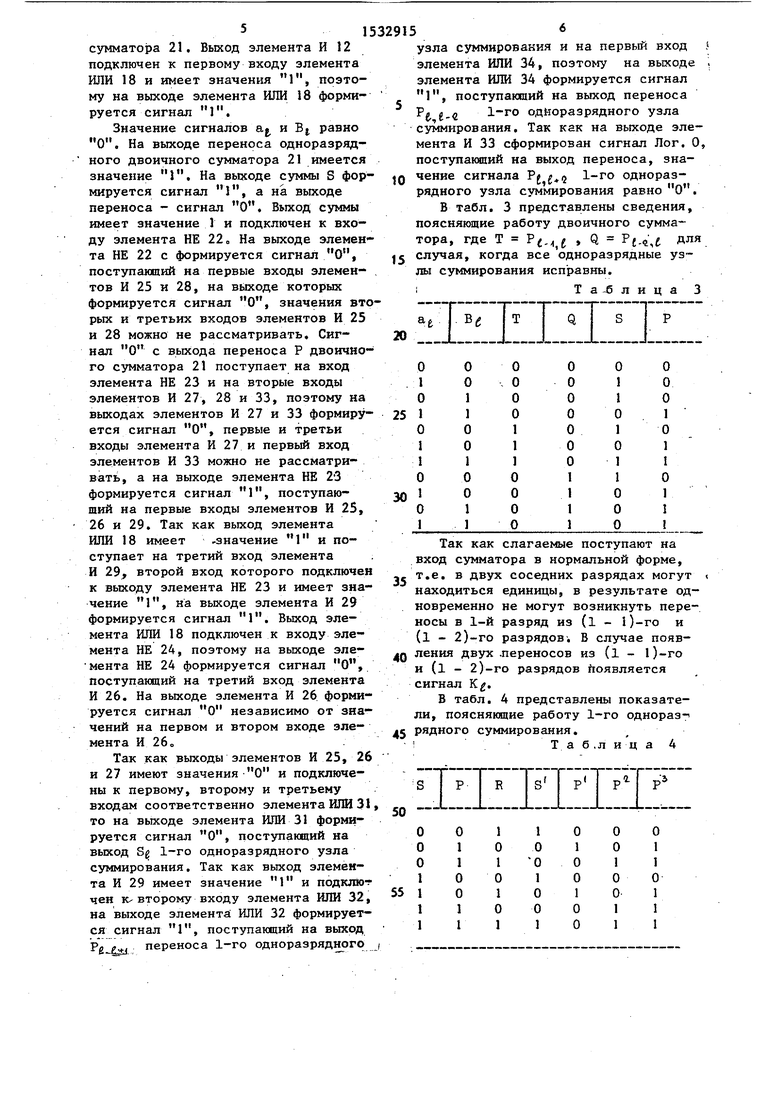

Пусть на входы запретов V 1-го одноразрядного узла суммирования подаются значения согласно табл. 1.

Таблица 1

В этом случае на 1-й одноразрядный узел суммирования поступают переносы с (l + 2)-го, (1 - 1)-го и (l - 2)-го одноразрядных узлов суммирования. Сигналы поступают согласно табл. 2.

Таблица 2

Сигнал 1 с входа Vf поступает

Lна вторые входы элемента И 8 и эле

0

5

0

5

0

5

0

5

мента И-НЕ 14. Так как сигнал Pg,r j, имеет значения 1 и поступает на первый вход элемента И 8 и на вход элемента НЕ 4, «то на выходе элемента И 8 формируется сигнал 1. Выход элемента 4 подключен к первому входу элемента И-НЕ 14, следовательно, на первом входе элемента И-НЕ 14 появляется О и на выходе этого элемента И-НЕ 14 формируется 1. Так как на втором входе запрета имеется О, поступающий на вторые входы элемента И 9 и элемента И-НЕ 15, то на выходе элемента И 9 формируется О, а на выходе элемента И-НЕ 15 Ml II

l .

На вторые входы элемента И 10 и элемента И-НЕ 16 поступает 1 с третьего входа запрета 1-го одноразрядного узла суммирования, сигнал Pg-tt e имеет значение О и поступает на первый вход элемента И 10 и на вход элемента НЕ 6, поэтому на выходе элемента НЕ 6 формируется 1, следовательно, на выходе элемента И 10 формируется сигнал О. Так как выход элемента НЕ 6 подключен к первому входу элемента И-НЕ 16 и имеет значения 1, на выходе элемента И-НЕ 16 формируется сигнал О. Поскольку сигнал Vg имеет значение О и поступает на вторые входы элемента И 11 и элемента И-НЕ 17, на выходе элемента И 11 формируется сигнал О, а на выходе элемента И-НЕ 17 - 1. Сигнал V| имеет значение 1 и поступает на второй вход элемента И 12, Так как сигнал ,e имеет значение 1 и поступает на первый вход элемента И 12, на выходе элемента И 12 формируется 1. Сигнал Vg6 имеет значение О и поступает на второй вход элемента И 13, поэтому на выходе элемента И И формируется сигнал О. Выход элемента И-НЕ 16 подключен к третьему входу элемента И 20. Независимо от значений сигнала на первом, втором и четвертом входах, на выходе элемента И 20 формируется сигнал О, поступающий на выход Кг. Выход элемента И 8 подключен к первому входу элемента ИЛИ 19, поэтому независимо от значений сигналов на втором, третьем и четвертом входах элемента ИЛИ 19 формируется сигнал 1, поступающий на вход переноса элемента одноразрядного двоичного

сумматора 21. Выход элемента И 12 подключен к первому входу элемента ИЛИ 18 и имеет значения 1, поэтому на выходе элемента ИЛИ 18 формируется сигнал 1.

Значение сигналов а и Bt равно О. На выходе переноса одноразрядного двоичного сумматора 21 имеется значение 1, На выходе суммы S формируется сигнал 1, а на выходе переноса - сигнал О. Выход суммы имеет значение 1 и подключен к входу элемента НЕ 22„ На выходе элемента НЕ 22 с формируется сигнал О, поступающий на первые входы элементов И 25 и 28, на выходе которых формируется сигнал О, значения вторых и третьих входов элементов И 25 и 28 можно не рассматривать. Сигнал О с выхода переноса Р двоичного сумматора 21 поступает на вход элемента НЕ 23 и на вторые входы элементов И 27, 28 и 33, поэтому на выходах элементов И 27 и 33 формируется сигнал О, первые и третьи входы элемента И 27 и первый вход элементов И 33 можно не рассматривать, а на выходе элемента НЕ 23 формируется сигнал 1, поступающий на первые входы элементов И 25, 26 и 29. Так как выход элемента ИЛИ 18 имеет .значение 1 и поступает на третий вход элемента И 29, второй вход которого подключен к выходу элемента НЕ 23 и имеет значение 1, на выходе элемента И 29 формируется сигнал 1. Выход элемента ИЛИ 18 подключен к входу элемента НЕ 24, поэтому на выходе элемента НЕ 24 формируется сигнал О, поступающий на третий вход элемента И 26. На выходе элемента И 26 формируется сигнал О независимо от значений на первом и втором входе элемента И 26„

Так как выходы элементов И 25, 26 и 27 имеют значения О и подключены к первому, второму и третьему входам соответственно элемента ИЛИ 31 то на выходе элемента ИЛИ 31 формируется сигнал О, поступающий на выход Sg 1-го одноразрядного узла суммирования. Так как выход элемента И 29 имеет значение 1 и подключен к-второму входу элемента ИЛИ 32, на выходе элемента ИЛИ 32 формируется сигнал 1, поступающий на выход Pg y переноса 1-го одноразрядного

o

5

0

узла суммирования и на первый вход элемента ИЛИ 34, поэтому на выходе , элемента ИЛИ 34 формируется сигнал 1, поступающий на выход переноса Pg, е,в 1-го одноразрядного узла суммирования. Так как на выходе элемента И 33 сформирован сигнал Лог. О, поступающий на выход переноса, значение сигнала Pj 5 1-го одноразрядного узла суммирования равно О. В табл. 3 представлены сведения, поясняющие работу двоичного сумматора, где Т РЈ. , Q Ре-«,е Аля случая, когда все одноразрядные узлы суммирования исправны.

Та-блица 3

ЗЕ1П111111

25

30

Так как слагаемые поступают на вход сумматора в нормальной форме,

т.е. в двух соседних разрядах могут , находиться единицы, в результате одновременно не могут возникнуть переносы в 1-й разряд из (1 - 1)-го и (1 - 2)-го разрядов. В случае появления двух -переносов из (1 - 1)-го и (l - 2)-го разрядов появляется сигнал К.

В табл. 4 представлены показатели, поясняющие работу 1-го однораэ-ч

рядного суммирования.

Таб,лица4

50

iniZEEI

55

Примечание. Для случаи, когда R ,е S S, Р

Р,ш Рг г

Ј,

рэ р

td i

все одноразрядные узлы суммирования исправны.

Одновременно на входы слагаемых сумматора поступают коды Фибоначчи в нормальной форме (А и В).

А ап . & BQ

В B...BfBgj

где а;, В j - двоичные цифры в I .

i-м разряде кода (i

0,1,...п).

Формируются переносы в каждом одноразрядном узле суммирования и первая промежуточная сумма, затем осуществляется суммирование переносов, образование второй промежуточной суммы и новых переносов и так до тех пор, пока не прекратится образование переносов и на выходах одноразрядных узлов суммирования не образуется код суммы

s,s(

о

где S; - двоичные цифры в i-м раз- ряде кода.

В дальнейшем этот код переписывается из сумматора на нормализатор, где с помощью операции свертки происходит нормализация кода результата. Если нарушено контрольное соотношение, то формируется соответствующий единичный сигнал Kg, который поступает на третий элемент ИЛИ и порождает на его выходе единичные значения, т.е. формируется сигнал ошибки К. При этом сигнал ошибки К 5 формируется исходя из того, что суммируемые коды находятся в нормальной форме, в их нулевых разрядах должны быть нули, а следовательно, единичный сигнал на выходе переноса двоичного сумматора 1 сигнализирует об ошибкео

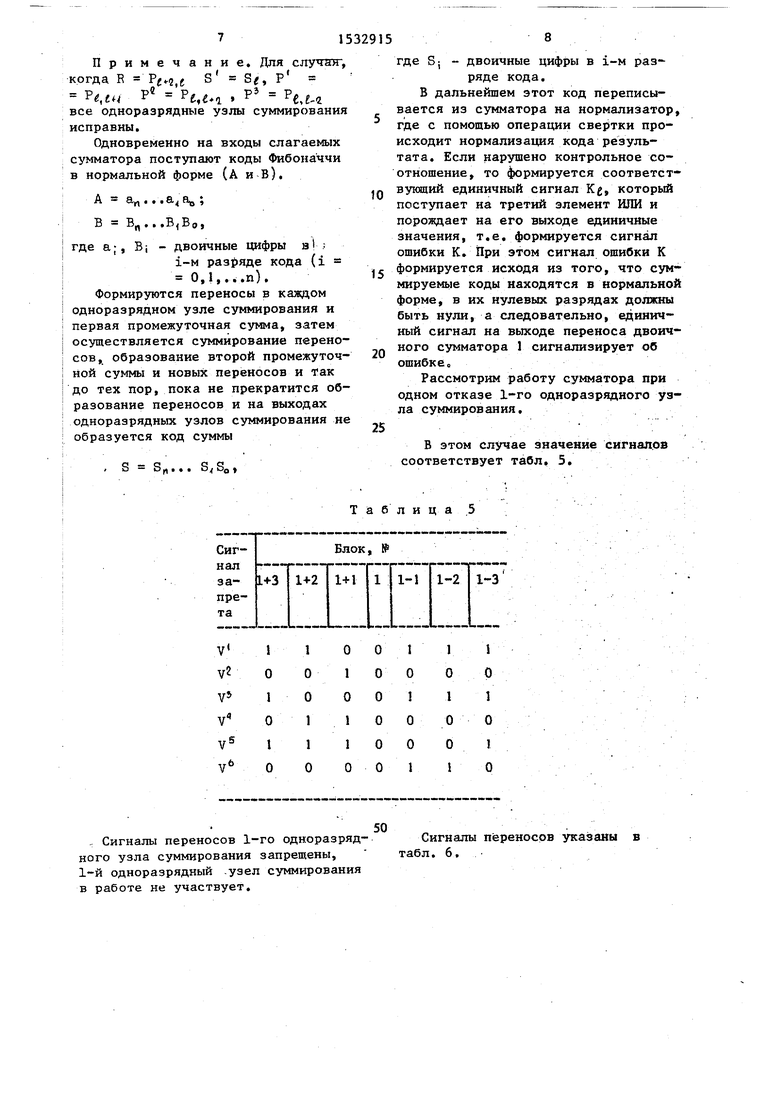

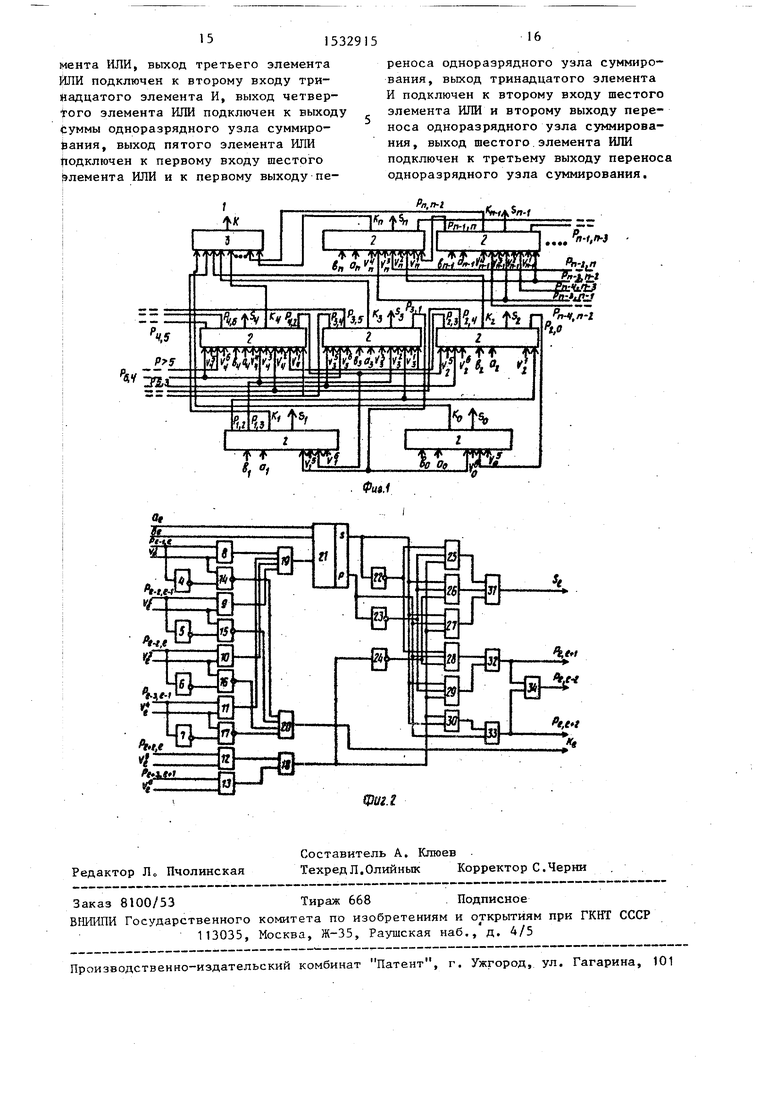

Рассмотрим работу сумматора при одном отказе 1-го одноразрядного узла суммирования.

0

В этом случае значение сигналов соответствует табл. 5,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах, к которым предъявляются требования повышенной надежности. Целью изобретения является повышение надежности за счет обеспечения функционирования при отказах одноразрядных узлов суммирования. Поставленная цель достигается за счет новой организации связей и решения одноразрядного узла суммирования в сумматоре кодов Фибоначчи, содержащем одноразрядные узлы суммирования и элемент ИЛИ. 1 з.п.ф-лы, 2 ил., 10 табл.

Сигналы переносов 1-го одноразрядного узла суммирования запрещены, 1-й одноразрядный узел суммирования в работе не участвует.

Таблица 5

50

Сигналы переносов указаны табл. 6.

Для одноразрядных узлов суммиро- вания, не указанных в табл. 6, сигналы переносов такие же, как для (1 + 3)-го и (l - 3)-го блоков.

В формировании суммы а и bg не участвуют и значения их не рассматри- вавдтся. В формировании переносов переносы 1-го одноразрядного сумматора не участвуют, следовательно, суммаСигналзапрета

Блок, №

1+6

|1+5 Т 1+4 Г 1+3Т 1+2 Г 1+3 Tl jfl-1 1 1-2 Tl-3

1

о 1 о 1 о

1

о о 1

г

о

о

о 1 1 о

Сигналы переносов Т, $, R, посту- пающие в узлы, указаны в табл, 8f

, , ,e,i °

QVfn.t b ,«+4 Ры,44 О

.«, PЈ,7,«-S ,г-4О

Таблица 6

тор не теряет функционирования при выходе из строя одного одноразрядного узла суммирования.

Рассмотрим работу сумматора для случая выхода из строя 1-го и(14-3)-го одноразрядных узлов суммирования.,

Сигналы запретов имеют значения согласно табл. 7.

Таблица 7

Блок, №

1 о о 1

о 1

о 1

о 1

о

1

о о о о о о

1

о 1

о о 1

1

о 1

о о 1

1 о 1

о 1 о

Таблица 8

ре-.,гч ре-«,е ° pe-s,e- p«-s,f-« -,«- Pe-i,«+t Р/-в,г О PJ.JIЈ.( P«., P«-5,e-s ««s,t Ргн.г.е о Ре.й)г Р,е-« ,е-з

Как видно, сумматор не теряет функционирования при выходе из строя двух узлов.

I При вычислении суммы значения а , &Ј.+ и не участвуют и на результат суммы не влияют.

тре- т,г. pt.s,c«

I QPe.s,e «.«,-

1 ,е«« Р «««,««

о Р|««,е« «.«,«« о Ре.цгч Р.,,« о Ve-«,-i (,« f(-4,«- о РЈ.«,«Ч ,« 0 РМ,{- ,е о Pj.1)4.( РЈ.«,«-« ,«ч 0 «, Р{ ,« о Ре.м ,б4 о Pe.«,i Р«.«,г- «-,«

Как видно из табл. 10 и 9, сигналы переносов с отказом трех однора- мовых узлов суммирования блокируются и сумматор не теряет функционирования .

Таким образом, сумматор правильно функционирует при отказах не только 1-го, но и последующих за Ним ЗК (где К - целое число) одноразрядных узлов суммирования.

Формула изобретения

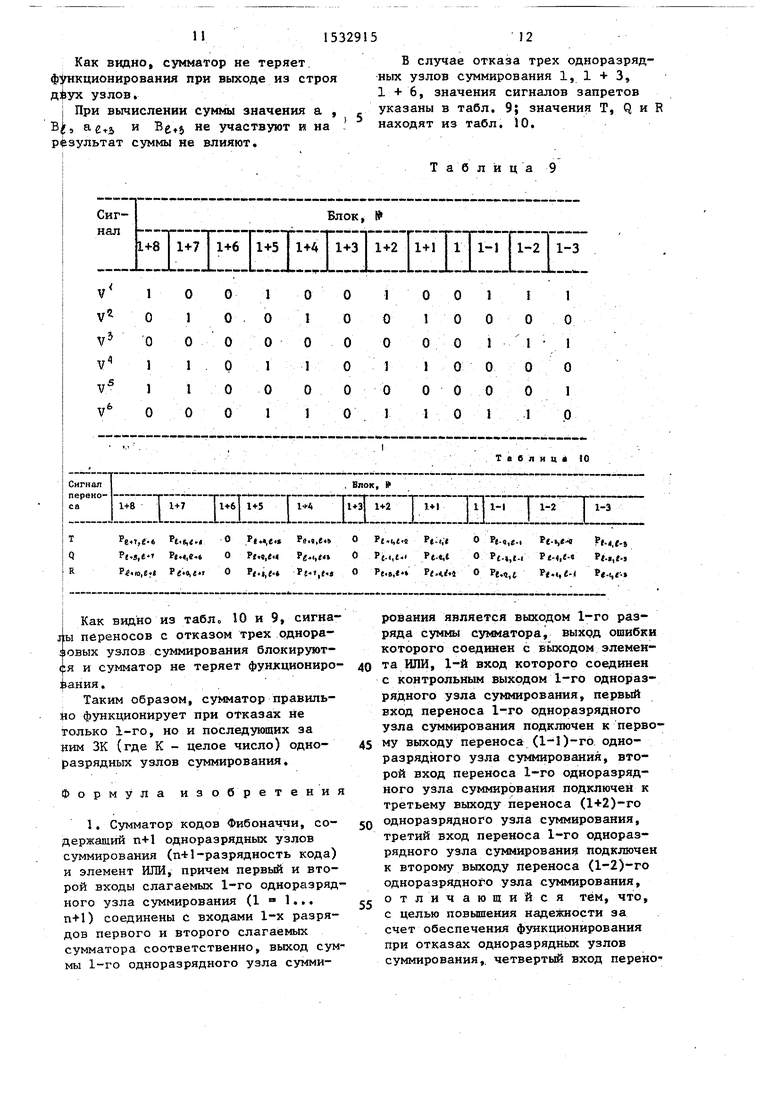

Таблица 9

0

рования является выходом 1-го разряда суммы сумматора, выход ошибки которого соединен с выходом элемента ИЛИ, 1-й вход которого соединен с контрольным выходом 1-го одноразрядного узла суммирования, первый вход переноса 1-го одноразрядного узла суммирования подключен к перво- 5 У выходу переноса (l-l)-ro одноразрядного узла суммирования, второй вход переноса 1-го одноразрядного узла суммирования подключен к третьему выходу переноса (1+2)-го одноразрядного узла суммирования, третий вход переноса 1-го одноразрядного узла суммирования подключен к второму выходу переноса (1-2)-го одноразрядного узла суммирования, отличающийся тем, что, с целью повышения надежности за счет обеспечения функционирования при отказах одноразрядных узлов суммирования, четвертый вход перено0

5

са 1-го одноразрядного узла суммирования подключен к первому выходу переноса (1-2)-го одноразрядного узла суммирования, пятый вход переноса 1-го одноразрядного узла суммирования к второму выходу переноса (1-3)-го одноразрядного узла суммирования, шестой вход переноса 1-го одноразрядного узла суммирования подключен к третьему выходу переноса (1+3)-го одноразрядного узла суммирования с первого по шестой входы запрета 1-го одноразрядного узла суммирования являются соответствующими входами запрета 1-й группы сумматора.

o

5

0

5

0

5

0

5

0

5

вход запрета одноразрядного узла суммирования подключен к вторым входам четвертых элементов И и И-НЕ, выходы пятого и шестого элементов И подключены соотвеАСтвенно к входам первого элемента ИЛИ, вход переноса двоичного одноразрядного сумматора подключен к выходу второго элемента ИЛИ, выход седьмого элемента И подключен к контрольному выходу одноразрядного узла суммирования, выход суммы двоичного одноразрядного сумматора подключен к входу пятого элемента НЕ, к первым входам девятого, десятого, двенадцатого элементов И и к первому входу третьего элемента ИЛИ, выход переноса двоичного одноразрядного сумматора подключен к входу шестого элемента НЕ, к второму входу десятого элемента И и к первым входам одиннадцатого и тринадцатого элементов И, пятый вход запрета одноразрядного узла суммирования подключен к второму входу пятого элемента И, шестой вход запрета одноразрядного узла суммирования подключен к второму входу шестого эле™ мента И, первый и второй входы слагаемых двоичного одноразрядного сумматора подключены к первому и второму входам слагаемых одноразрядного узла суммирования, выходы первого, второго, третьего и четвертого элементов И подключены соответственно к входам второго элемента ИЛИ, выходы первого, второго, третьего и четвертого элементов И-НЕ подключены соответственно к входам седьмого элемента И,- выход пятого элемента НЕ соединен с первым входом восьмого элемента И и с вторым входом одиннадцатого элемента И, выход шестого элемента НЕ подключен к вторым вхо- дам восьмого, девятого и двенадцатого элементов И, выход- первого элемента ИЛИ подключен к входу седьмого элемента НЕ, к третьим входам восьмого, десятого, двенадцатого элементов И и к второму входу третьего элемента ИЛИ, выход седьмого элемента НЕ подключен к третьим входам девятого и один-надцатого элементов И, выходы восьмого, девятого и десятого элементов И подключены соответственно к входам четвертого элемента ИЛИ, выходы одиннадцатого и двенадцатого элементов И подключены соответственно к входам пятого элемента ИЛИ, выход третьего элемента ИЛИ подключен к второму входу тринадцатого элемента И, выход четвертого элемента ИЛИ подключен к выходу суммы одноразрядного узла суммирования, выход пятого элемента ИЛИ Подключен к первому входу шестого (элемента ИЛИ и к первому выходу печг

реноса одноразрядного узла суммирования, выход тринадцатого элемента И подключен к второму входу шестого элемента ИЛИ и второму выходу переноса одноразрядного узла суммирования , выход шестого элемента ИЛИ подключен к третьему выходу переноса одноразрядного узла суммирования.

Фш.1

| Сумматор кодов Фибоначчи | 1987 |

|

SU1411735A1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-30—Публикация

1987-12-04—Подача