сд

Фие.

Изобретение относится к вычисли- тельной технике и может быть применено в централизованных программируемых контроллерах, предназначенных для управления технологическими линиями и оборудованием массового производства; металлорежущим, кузнеч- но прессовым, литейным и др.

Цель изобретения - расширение области применения устройства путем обеспечения его работы с битовым форматом данных.

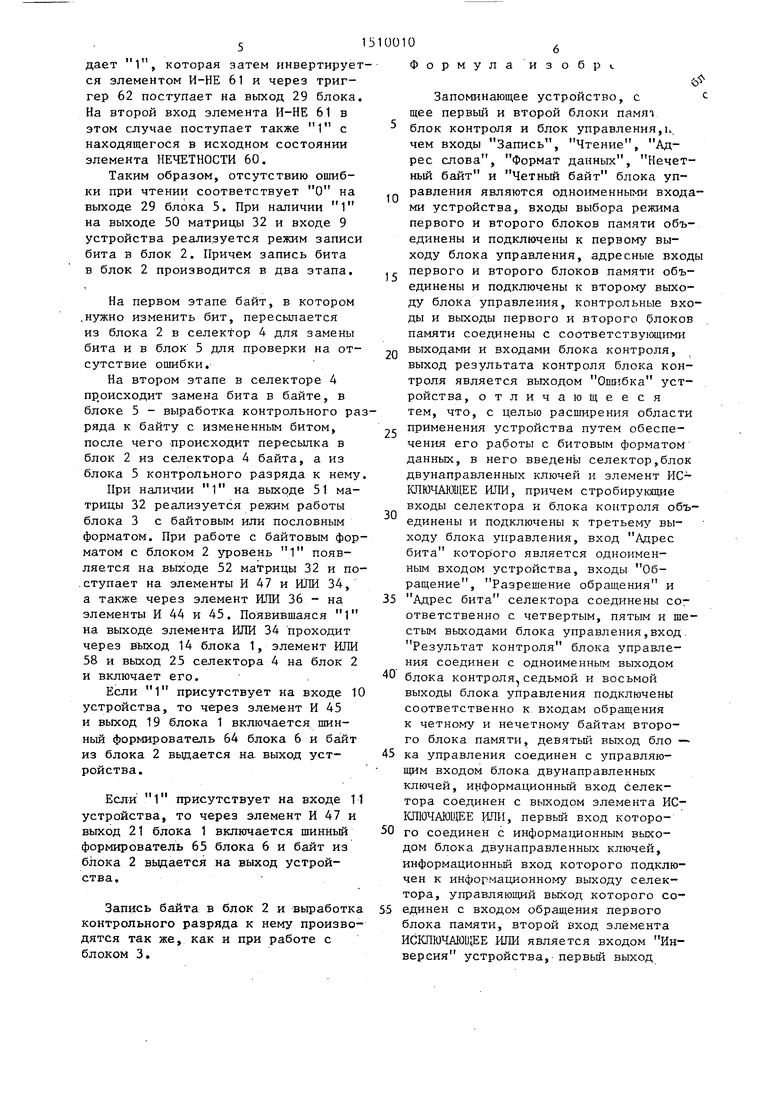

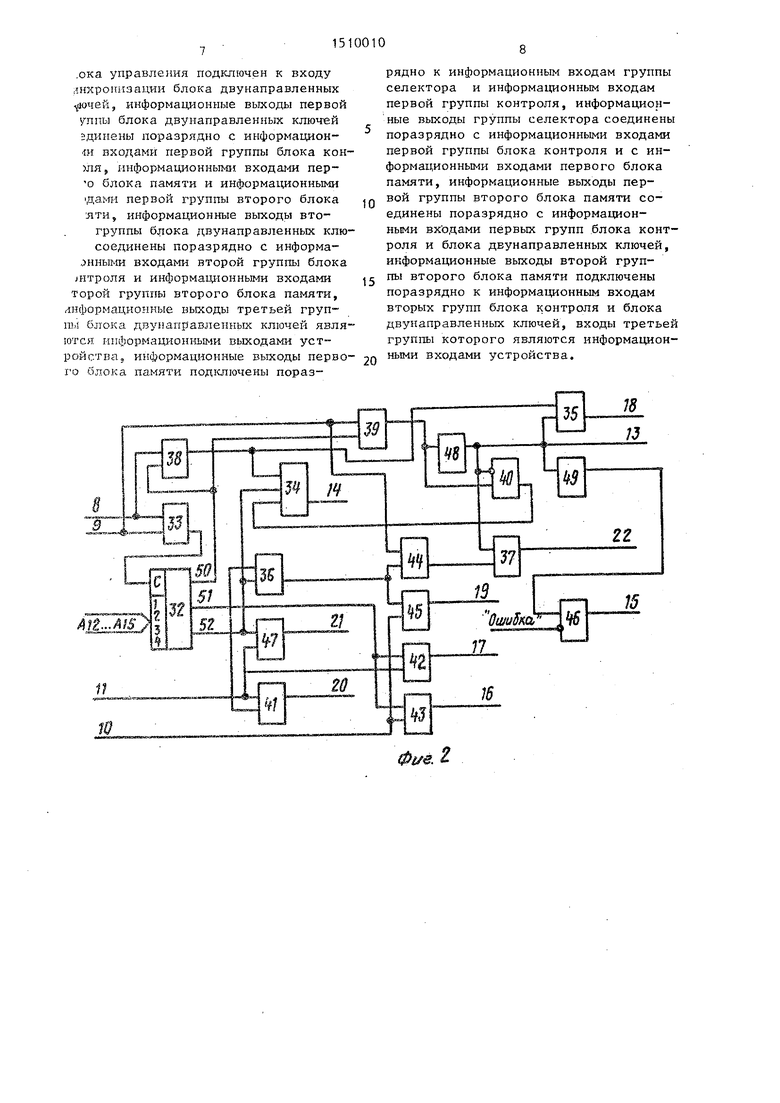

На фиг,1 приведена структурная схема запоминанлцего устройства; на фиг,2 - структурная схема блока управления; на фиг.З - структурная схема селектора; на фиг.4 - структурная схема блока контроля; на фиг.З - структурная схема блока двунаправленных ключей.

Запоминающее устройство содержит (фиг.1) блок 1 управления, первый 2 и второй 3 блоки памяти,селектор,4

10

15

20

Устройство может работать с битовым, байтовым и пословным форматами информации. Формат информации задается в адресном коде старшими разрядами А12...А15, которые поступают .на информационные входы матрицы 32,

Уровень 1 на выходе 50 матрицы 32 означает работу с блоком 2 в битовом формате, на выходе 51 - работу с блоком 3 в байтовом или пословном формате, на выходе 52 - работу с блоком 2 в байтовом формате.

Устройство работает следующим образом.

При наличии 1 на выходе 50 матрицы 32 и входе 8 устройства реализуется режим чтения бита информации из блока 2. При этом срабатывает элемент И 38 и его выходной сигнал через элемент ИЛИ 35 и выход 18 блока 1 устанавливает шинный формирователь 63 на выдачу бита из устройблок 5 контроля, блок 6 двунаправлен-25 ства, причем на вьг-оде 23 формирова- ных ключей и элемент ИС1ШЮЧАЩЕЕ ИЛИ 7. На фиг.1 обозначены также входы 8-11 блока 1 управления, вход Ин- версия 12, выходы 13-22 блока управления, выход 23 блока 6, вход 24 и выходы 25 и 26 селектора 4, входы 27 и 28 и выходы 29-31 блока 5 контроля. .

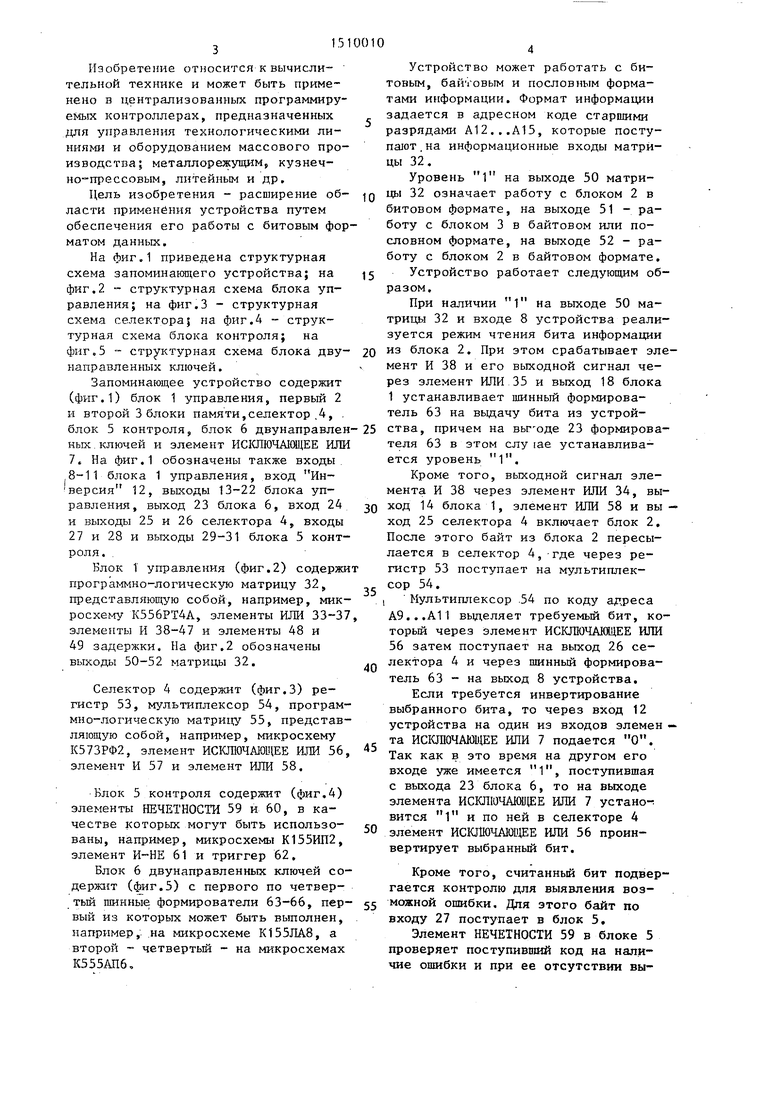

Блок Т управления (фиг.2) содержит программно-логическую матрицу 32, представляющую собой, например, микросхему К556РТ4А, элементы ИЛИ 33-37, элементы И 38-47 и элементы 48 и 49 задержки. На фиг.2 обозначены выходы 50-52 матрицы 32.

теля 63 в этом слу lae устанавливается уровень 1.

Кроме того, выходной сигнал элемента И 38 через элемент ИЛИ 34, вы- 30 ход 14 блока 1, элемент ИЛИ 58 и вы - ход 25 селектора 4 включает блок 2, После этого байт из блока 2 пересылается в селектор 4,-где через регистр 53 поступает на мультиплексор 54.

Мультиплексор .54 по коду адреса

35

40

А9...А11 выделяет требуемый бит, который через элемент ИСКЛЮЧАЩЕЕ ИЛИ 56 затем поступает на выход 26 селектора 4 и через шинный формирователь 63 - на выход 8 устройства. Если требуется инвертирование выбранного бита, то через вход 12 устройства на один из входов элемен - та ИСКЛЮЧАЮЬ ЕЕ ИЛИ 7 подается О. Так как в это время на другом его входе уже имеется 1, поступившая с выхода 23 блока 6, то на выходе элемента ИСКЛЮЧАЮПЩЕ ИЛИ 7 устано-г вится 1 и по ней в селекторе 4 50 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 56 проин- вертирует выбранный бит.

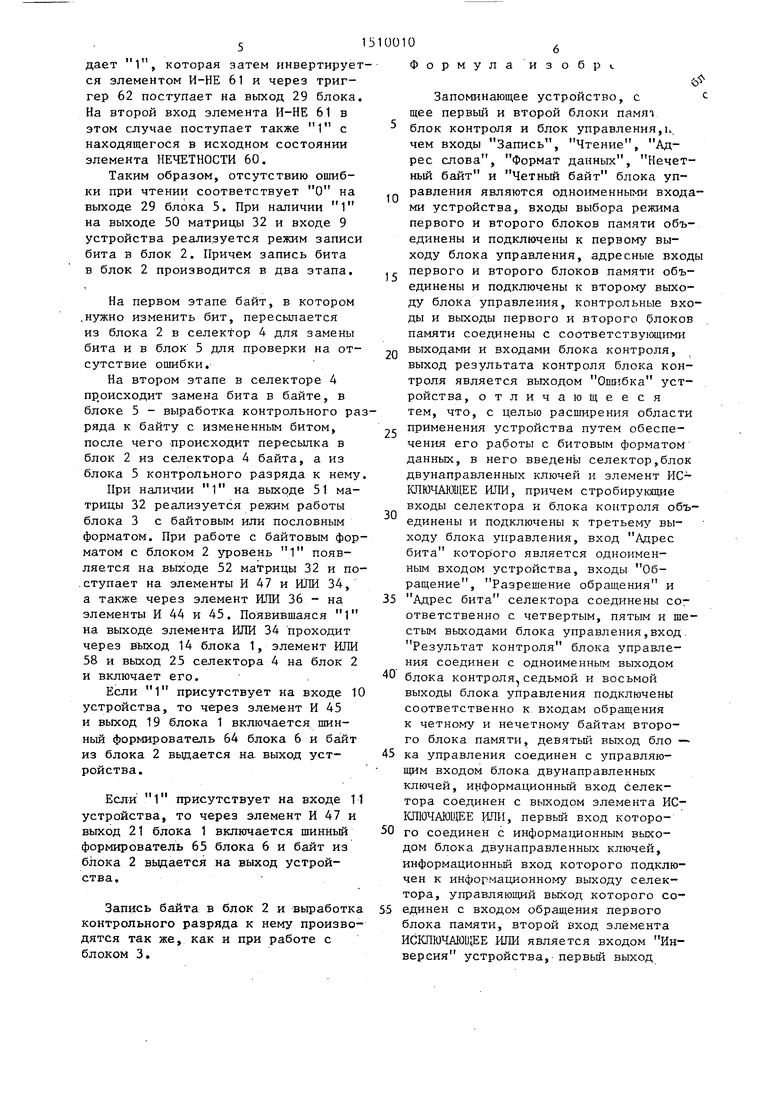

Селектор 4 содержит (фиг.З) регистр 53, мультиплексор 54, программно-логическую матрицу 55, представляющую собой, например, микросхему К573РФ2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 56, элемент И 57 и элемент ИЛИ 58.

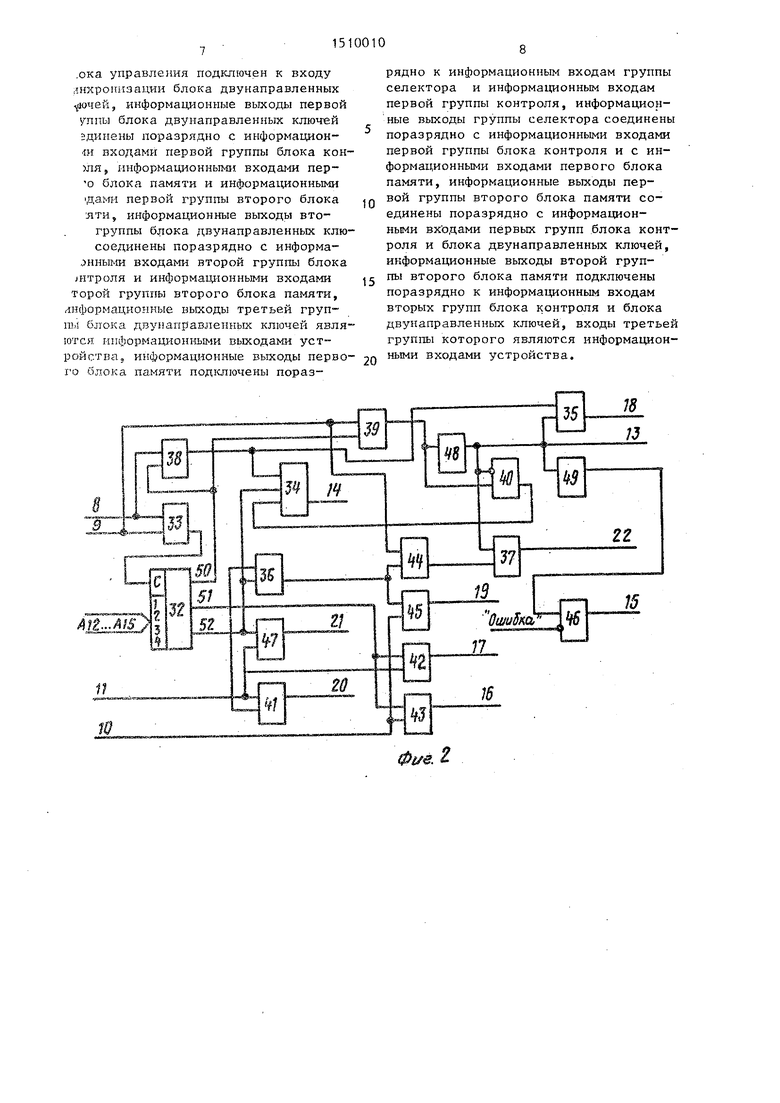

Блок 5 контроля содержит (фиг.4) элементы НЕЧЕТНОСТИ 59 и 60, в качестве которых могут быть использованы, например, микросхемы К155ИП2, элемент 61 и триггер 62.

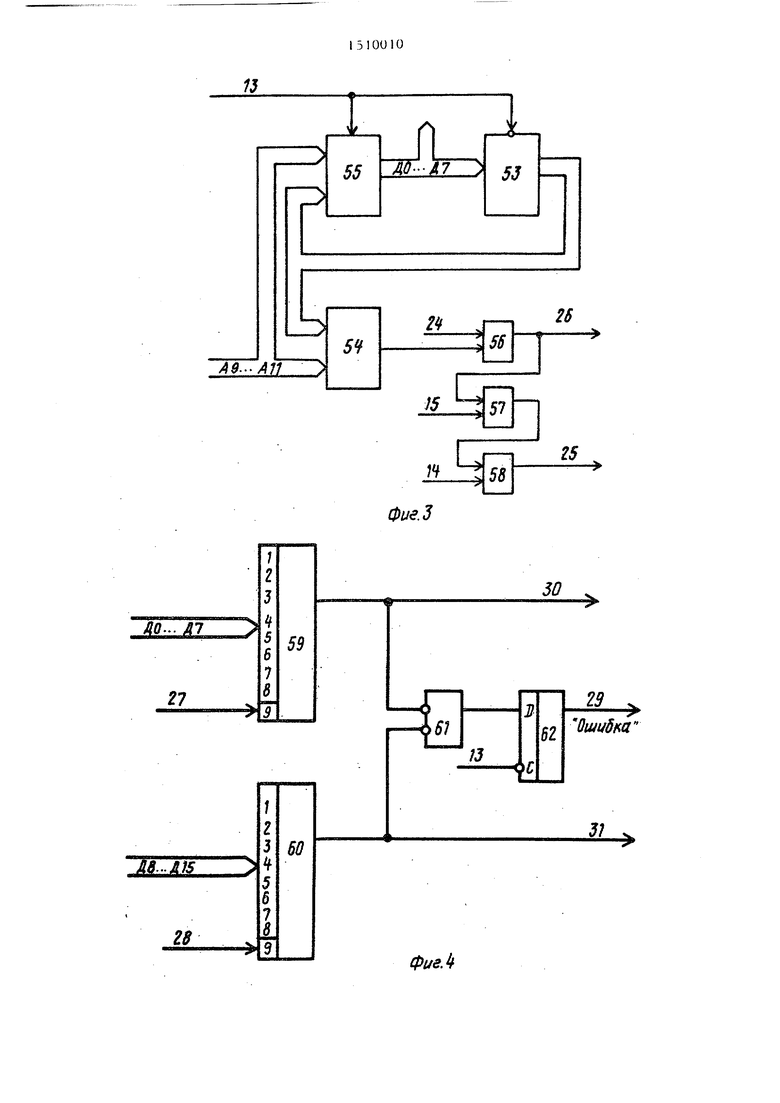

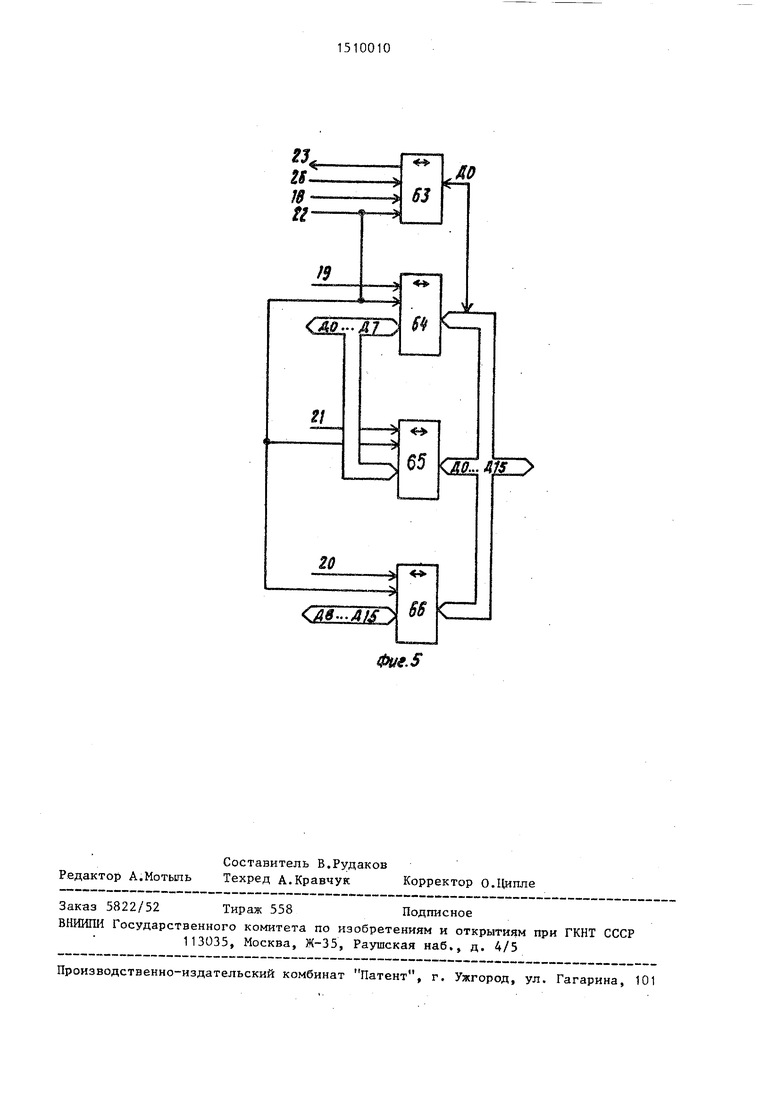

Блок 6 двунаправленных ключей содержит (фиг.5) с первого по четвер0

5

0

Устройство может работать с битовым, байтовым и пословным форматами информации. Формат информации задается в адресном коде старшими разрядами А12...А15, которые поступают .на информационные входы матрицы 32,

Уровень 1 на выходе 50 матрицы 32 означает работу с блоком 2 в битовом формате, на выходе 51 - работу с блоком 3 в байтовом или пословном формате, на выходе 52 - работу с блоком 2 в байтовом формате.

Устройство работает следующим образом.

При наличии 1 на выходе 50 матрицы 32 и входе 8 устройства реализуется режим чтения бита информации из блока 2. При этом срабатывает элемент И 38 и его выходной сигнал через элемент ИЛИ 35 и выход 18 блока 1 устанавливает шинный формирователь 63 на выдачу бита из устройства, причем на вьг-оде 23 формирова-

теля 63 в этом слу lae устанавливается уровень 1.

Кроме того, выходной сигнал элемента И 38 через элемент ИЛИ 34, вы- ход 14 блока 1, элемент ИЛИ 58 и вы - ход 25 селектора 4 включает блок 2, После этого байт из блока 2 пересылается в селектор 4,-где через регистр 53 поступает на мультиплексор 54.

Мультиплексор .54 по коду адреса

0

А9...А11 выделяет требуемый бит, который через элемент ИСКЛЮЧАЩЕЕ ИЛИ 56 затем поступает на выход 26 селектора 4 и через шинный формирователь 63 - на выход 8 устройства. Если требуется инвертирование выбранного бита, то через вход 12 устройства на один из входов элемен - та ИСКЛЮЧАЮЬ ЕЕ ИЛИ 7 подается О. Так как в это время на другом его входе уже имеется 1, поступившая с выхода 23 блока 6, то на выходе элемента ИСКЛЮЧАЮПЩЕ ИЛИ 7 устано-г вится 1 и по ней в селекторе 4 0 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 56 проин- вертирует выбранный бит.

Кроме того, считанный бит подвергается контролю для выявления воз5

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1990 |

|

SU1805496A1 |

| Запоминающее устройство для программируемого контроллера | 1984 |

|

SU1228146A1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2503135C1 |

| МНОГОЛИНЕЙНОЕ УСТРОЙСТВО УПЛОТНЕНИЯ ПО ДЛИНАМ ВОЛН И ОПТИЧЕСКАЯ АВТОМАТИЧЕСКАЯ ТЕЛЕФОННАЯ СТАНЦИЯ | 2005 |

|

RU2297719C2 |

| СПОСОБ И УСТРОЙСТВО ЗАПИСИ ДАННЫХ, НОСИТЕЛЬ ДАННЫХ И СПОСОБ И УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ ДАННЫХ | 1996 |

|

RU2191423C2 |

| Устройство для декодирования информации с исправлением ошибок | 1985 |

|

SU1505451A3 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| СПОСОБ, УСТРОЙСТВО И НОСИТЕЛЬ ДЛЯ КОДИРОВАНИЯ СОСТОЯЩЕЙ ИЗ МНОГИХ СЛОВ ИНФОРМАЦИИ | 1999 |

|

RU2273092C2 |

Изобретение относится к вычислительной технике и может быть применено в централизованн ых программируемых контроллерах, предназначенных для управления техно логическими линиями и оборудованием массового производства: металлорежущим, кузнечно-прессовым, литейным и др. Цель изобретения состоит в расширении области применения устройства за счет придания ему дополнительных свойств, позволяющих в пределах байта селективно производить запись и чтение битовой информации, включая иее инвертирование. Устройство содержит блок 1 управления, блоки 2 и 3 памяти, селектор 4, блок 5 контроля, блок 6 двунаправленных ключей и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7. 5 ил.

тый шинные формирователи 63-66, пер- 55 ожной ошибки. Для этого байт по вый из которых может быть выполнен, входу 27 поступает в блок 5,

например, на микросхеме К155ЛА8, а второй - четвертый - на микросхемах

К555АП6,

Элемент НЕЧЕТНОСТИ 59 в блоке 5 проверяет поступнвпшй код на наличие опшбки и при ее отсутствии выдает 1, которая затем инвертируется элементом И-НЕ 61 и через триггер 62 поступает на выход 29 блока. На второй вход элемента И-НЕ 61 в этом случае поступает также 1 с находящегося в исходном состоянии элемента НЕЧЕТНОСТИ 60.

Таким образом, отсутствию ошибки при чтении соответствует О на выходе 29 блока 5. При наличии 1 на выходе 50 матрицы 32 и входе 9 устройства реализуется режим записи бита в блок 2. Причем запись бита в блок 2 производится в два этапа.

На первом этапе байт, в котором .нужно изменить бит, пересылается из блока 2 в селектор 4 для замены бита и в блок 5 для проверки на отсутствие ошибки.

На втором этапе в селекторе 4 пр оисходит замена бита в байте, в блоке 5 - выработка контрольного раряда к байту с измененным битом, после чего -происходит пересылка в блок 2 из селектора 4 байта, а из блока 5 контрольного разряда к нему

При наличии 1 на выходе 51 матрицы 32 реализуется режим работы блока 3 с байтовым или пословным форматом. При работе с байтовым форматом с блоком 2 уровень 1 появляется на выходе 52 матрицы 32 и по- .ступает на элементы И 47 и ИЛИ 34, а также через элемент ИЛИ 36 - на элементы И 44 и 45. Появившаяся 1 на выходе элемента ИЛИ 34 проходит через выход 14 блока 1, элемент ИЛИ 58 и выход 25 селектора 4 на блок 2 и включает его.

Если 1 присутствует на входе 10 устройства, то через элемент И 45 и выход 19 блока 1 включается шинный формирователь 64 блока 6 и байт из блока 2 вьздается на. выход устройства.

Если 1 присутствует на входе 1 устройства, то через элемент И 47 и выход 21 блока 1 включается шинньй формирователь 65 блока 6 и байт из блока 2 вьщается на выход устройства.

Запись байта в блок 2 и выработка контрольного разряда к нему производятся так же, как и при работе с блоком 3.

0

Формула изобр(.

Ъ

Запоминающее устройство, с щее первьш и второй блоки памя блок контроля и блок управления,ь. чем входы Запись, Чтение, Адрес слова, Формат данных, Нечетный байт и Четный байт блока управления являются одноименными входами устройства, входы выбора режима первого и второго блоков памяти объединены и подключены к первому выходу блока управления, адресные входы

первого и второго блоков памяти объединены и подключены к второму выходу блока управления, контрольные входы и выходы первого и второго блоков памяти соединены с соответствующими

Q выходами и входами блока контроля, выход результата контроля блока контроля является выходом Опшбка устройства, отличающееся тем, что, с целью расширения области

,г применения устройства путем обеспечения его работы с битовым форматом данных, в него введены селектор,блок двунаправленных ключей и элемент ИСКЛЮЧАЮЩЕЕ ИТШ, причем стробирукящ1е входы селектора и блока контроля объединены и подключены к третьему выходу блока управления, вход Адрес бита которого является одноименным входом устройства, входы Обращение, Разрешение обращения и

5 Адрес бита селектора соединены соответственно с четвертым, пятым и шестым выходами блока управления,вход. Результат контроля блока управления соединен с одноименным выходом

0 блока контроля,седьмой и восьмой выходы блока управления подключены соответственно к входам обращения к четному и нечетному байтам второго блока памяти, девятьй выход бло -

5 ка управления соединен с управляющим входом блока двунаправленных ключей, информационный вход селектора соединен с выходом элемента ИС- КЛЮЧАКИЩЕ ИЛИ, первый вход которо0 го соединен с информатдаонным выходом блока двунаправленных ключей, информаЦионньй вход которого подключен к информационному выходу селектора, управляющий выход которого со5 единен с входом обращения первого блока памяти, второй вход элемента ИСКПЮЧАЮи ЕЕ ИЛИ является входом Инверсия устройства,-первый выход

0

.ока управления подключен к входу лнхронизадии блока двунаправленных , информационные выходы первой у-ппы блока двунаправленных ключей гдинены поразрядно с информацион- «I входами первой группы блока кон- шя, информационными входами пер- о блока памяти и информагщонными первой группы второго блока яти, информационные выходы вто- группы блока двунаправленных клю- соединены поразрядно с информа- .зиными входами второй группы блока нтроля и инфopмaциoнньпvIи входами торой группы второго блока памяти, лнформациоиные выходы третьей группы блока двунаправленных ключей явля- 50ТСЯ информационными выходами устройства, информационные выходы первого блока памяти подключены пораз21

20

0

рядно к информационным входам группы селектора и информационным входам первой группы контроля, информационные выходы группы селектора соединены поразрядно с информационными входами первой группы блока контроля и с информационными входами первого блока памяти, информационные выходы первой группы второго блока памяти соединены поразрядно с информационными входами первых групп блока контроля и блока двунаправленных ключей, информационные выходы второй груп- 5 пы второго блока памяти подключены поразрядно к информационным входам вторых групп блока контроля и блока двунаправленных ключей, входы третьей группы которого являются информационными входами устройства.

0

75

Ю

0i/€.

фие.З

3

Wп

f9

Ж-Ж.)

20

M3ZO

МО

63

4

и

65

М1.М

4

§s

czU

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПРОИЗВОЛЬНОЙ ОДНОВРЕМЕННОЙ ВЫБОРКОЙ ПЕРЕМЕННОГО МАССИВА | 0 |

|

SU367456A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство | 1978 |

|

SU898502A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1987-05-04—Подача