Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), и может быть использовано при построении ЗУ программируемых контроллеров.

Цель изобретения - упрощение и повышение информационной емкости устроства.

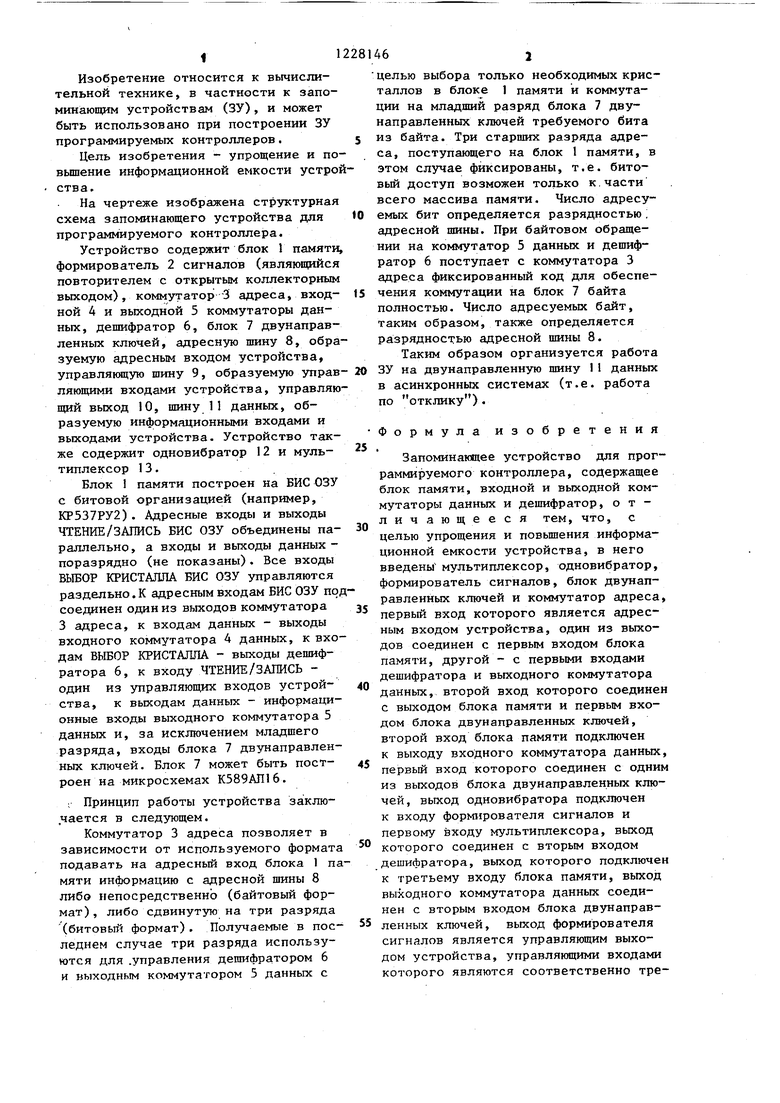

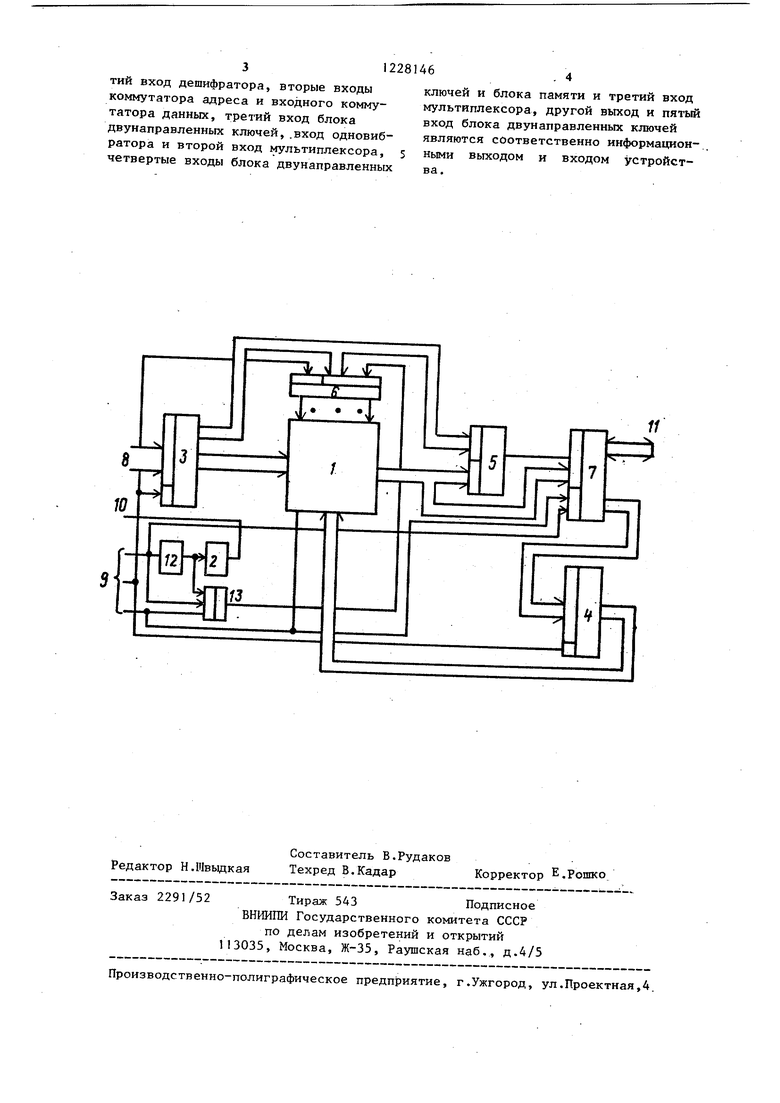

На чертеже изображена структурная схема запоминающего устройства для программируемого контроллера.

Устройство содержит блок 1 памяти формирователь 2 сигналов (являющийся повторителем с открытьм коллекторным выходом), коммутатор -3 адреса, вход- ной А и выходной 5 коммутаторы данных, дешифратор 6, блок 7 двунаправленных ключей, адресную шину 8, образуемую адресным входом устройства, управляющую шину 9, образуемую управ ляющими входами устройства, управляющий выход 10, шину 11 данных, образуемую информационными входами и выходами устройства. Устройство также содержит одновибратор 12 и муль- типлексор 13.

Блок памяти построен на БИС ОЗУ с битовой организацией (например, КР537РУ2). Адресные входы и выходы ЧТЕНИЕ/ЗАПИСЬ БИС ОЗУ объединены па- раллельно, а входы и выходы данных - поразрядно (не показаны). Все входы ВЫБОР КРИСТАЛЛА БИС ОЗУ управляются раздельно.К адресным входам БИС ОЗУ подсоединен один из выходов коммутатора 3 адреса, к входам данных - выходы входного коммутатора А данных, к входам ВЫБОР КРИСТАЛЛА - выходы дешифратора 6, к входу ЧТЕНИЕ/ЗАПИСЬ - один из управляющих входов устрой- ства, к выходам данных - информационные входы выходного коммутатора 5 данных и, за исключением младшего разряда, входы блока 7 двунаправленных ключей. Блок 7 может быть пост- роен на микросхемах К589АП16.

; Принцип работы устройства чается в следующем.

Коммутатор 3 адреса позволяет в зависимости от используемого формата подавать на адресный вход блока 1 памяти информацию с адресной шины 8 либо непосредственно (байтовый формат), либо сдвинутую на три разряда (битовьш формат). Получаемые в пос- леднем случае три разряда используются для .управления дешифратором 6 и выходным коммутатором 5 данных с

целью выбора только необходимых кристаллов в блоке 1 памяти и коммутации на младший разряд блока 7 двунаправленных ключей требуемого бита из байта. Три старших разряда адреса, поступающего на блок 1 памяти, в этом случае фиксированы, т.е. битовый доступ возможеи только к.части всего массива памяти. Число адресуемых бит определяется разрядностью . адресной шины. При байтовом обращении на коммутатор 5 данных и дешифратор 6 поступает с коммутатора 3 адреса фиксированный код для обеспечения коммутации на блок 7 байта полностью. Число адресуемых байт, таким образом, также определяется ра:зрядностью адресной шины 8.

Таким образом организуется работа ЗУ на двунаправленную шину I1 данных в асинхронных системах (т.е. работа по отклику).

Формула изобретения

Запоминающее устройство для программируемого контроллера, содержащее блок памяти, входной и выходной коммутаторы данных и дешифратор, отличающееся тем, что, с целью упрощения и повьш1ения информационной емкости устройства, в него введены мультиплексор, одновибратор, формирователь сигналов, блок двунап- равленньпс ключей и коммутатор адреса, первый вход которого является адресным входом устройства, один из выходов соединен с первым входом блока памяти, другой - с первыми входами дешифратора и выходного коммутатора данных, второй вход которого соединен с выходом блока памяти и первым входом блока двунаправленных ключей, второй вход блока памяти подключен к выходу входного коммутатора данных, первый вход которого соединен с одним из выходов блока двунаправленных ключей, выход одновибратора подключен к входу формирователя сигналов и первому входу мультиплексора, вьпсод которого соединен с вторым входом дешифратора, выход которого подключен к третьему входу блока памяти, выход выходного коммутатора данных соединен с вторым входом блока двунаправленных ключей, выход формирователя сигналов является управляющим выходом устройства, управляющими входами которого являются соответственно третий вход дешифратора, вторые входы коммутатора адреса и входного коммутатора данных, третий вход блока двунаправленных ключей, .вход одновиб- ратора и второй вход мультиплексора, четвертые входы блока двунаправленных

II

I

Ю

3

13

Составитель В.Рудаков Редактор Н.Швыдкая Техред В.Кадар Корректор Е.рошко

2291/52

Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4.

- , 5 х

12281464

ключей и блока памяти и третий вход мультиплексора, другой выход и пятый вход блока двунаправленных ключей являются соответственно информационными выходом и входом устройства.

11

Р

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1510010A1 |

| Запоминающее устройство | 1990 |

|

SU1805496A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

Изобретение относится к области., вычислительной техники и может быть использовано при построении запоминающих устройств для программируемых контроллеров. Цель изобретения - упрощение устройства и повышение его информационной емкости. В устройстве используют только два формата: байтовый и битовый. Коммутатор адреса позволяет подавать на адресные входы блока памяти информацию с адресной шины либо непосредственно (байтовый формат) либо сдвинутую на три разряда (битовый формат). Получаемые в - последнем случае три разряда используются для управления дешифратором и выходным коммутатором данных с целью выбора только необходимых кристаллов в блоке памяти и коммутации на младший разряд блока двунаправленных ключей требуемого бита из байта4 1 ил. (Л с ю ю сх 4 аь

| Патент США № 3825907, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Запоминающее устройство | 1974 |

|

SU526019A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-30—Публикация

1984-04-03—Подача