Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в централизованных программируемых контроллерах, предназначенных для управления Технологическими линиями и оборудованием массового производства.

Целью изобретения является расширение области применения устройства за счет возможности выполнения селективно операций чтения и записи битовой информации в пределах байта.

На фиг. 1 приведена схема запоминающего устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема селектора; на фиг. 4 - схема блока контроля; на фиг. 5 - схема блока двунаправленных ключей.

Устройство (фиг, 1) содержит блок 1 управления, первый 2 и второй 3 блоки памяти, селектор 4, блок контроля 5, блок двунаправленных ключей б, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, триггер 8, элемент ИЛИ-ЫЕ 9, элемент И-НЕ 10, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, элемент И 12. На фиг. 1 обозначены также выходы 13-22 блока управления, выход 23 блока двунаправленных ключей б, четвертый вход 24, первый 25 и второй 26 выходы селектора 4, первый 27, второй 28 входы, выход 29 Ошибка, первый 30, второй 31 выходы блока контроля 5.

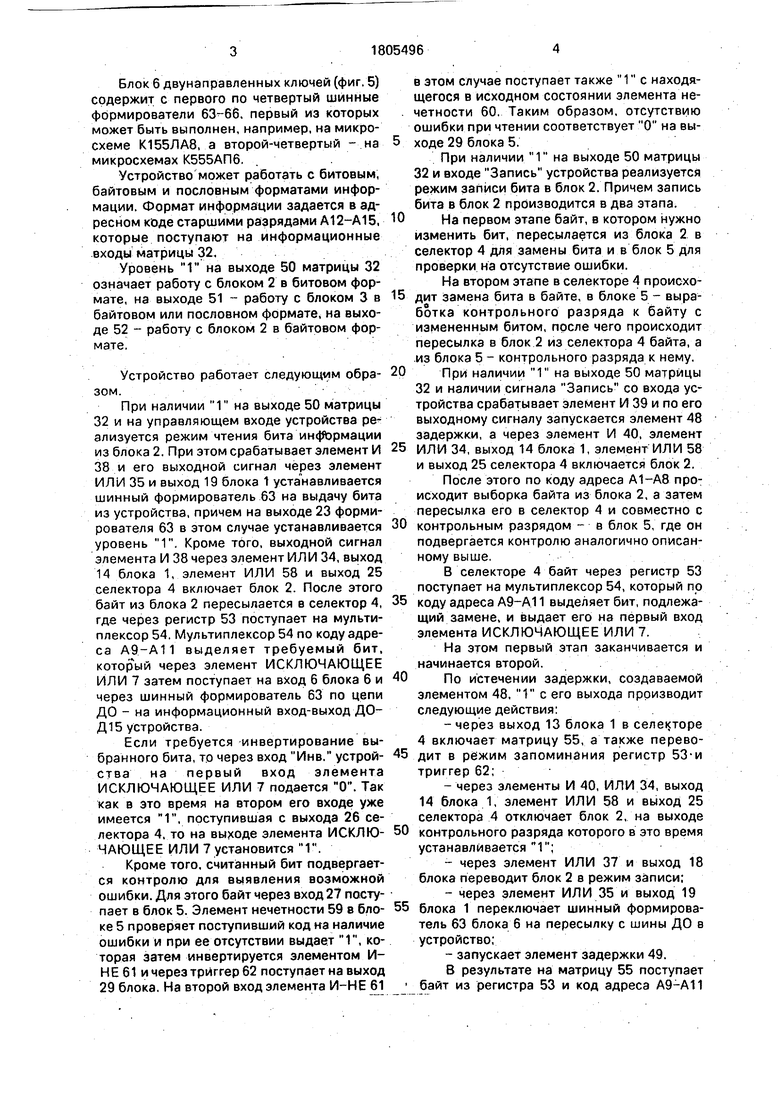

Блок 1 управления (фиг. 2) содержит программно-логическую матрицу 32, представляющую собой, например, микросхему К556РТ4А. элементы ИЛИ 33-37. элементы И 38-47 и элементы задержки 48 и 49. На фиг. 2 обозначены выходы 50-52 матрицы 32.

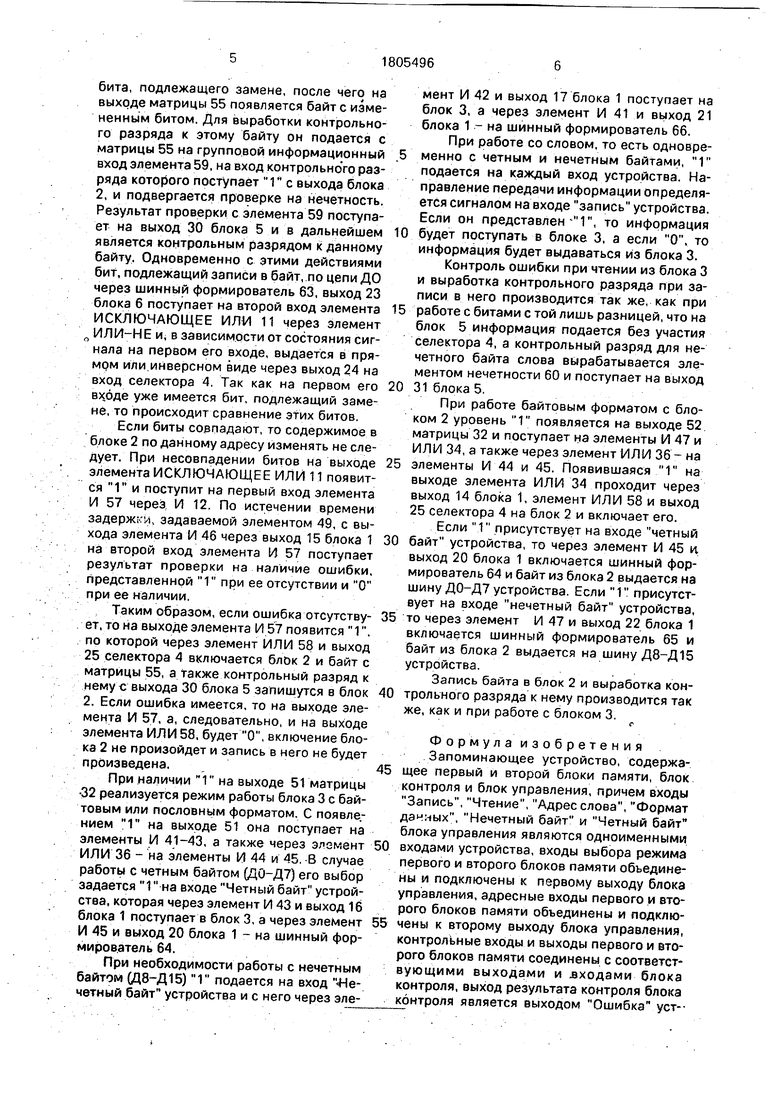

Селектор 4 (фиг. 3) содержит регистр 53, мультиплексор 54, программно-логическую матрицу 55, представляющую собой, например, микросхему К573РФ2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 56, элемент И 57 и элемент ИЛИ 58.

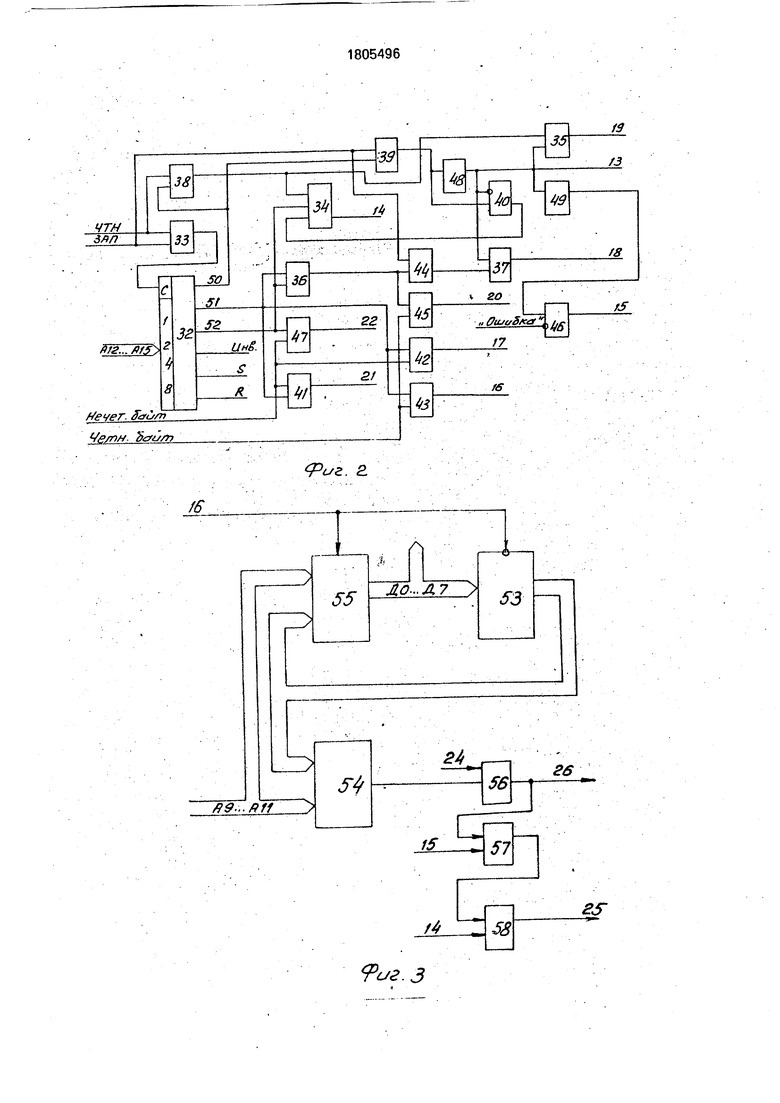

Блок 5 контроля (фиг. 4) содержит элементы нечетности 59 и 60, в качестве которых могут быть использованы, например, микросхемы К155ИП2, элемент И-НЕ 61 и триггер 62.

ел ю о

Блок 6 двунаправленных ключей (фиг. 5) содержит с первого по четвертый шинные формирователи . первый из которых может быть выполнен, например, на микросхеме К155ЛА8, а второй-четвертый - на микросхемах К555АП6.

Устройство может работать с битовым, байтовым и пословным форматами информации. Формат информации задается в адресном коде старшими разрядами А12-А15, которые поступают на информационные входы матрицы 32.

Уровень 1 на выходе 50 матрицы 32 означает работу с блоком 2 в битовом формате, на выходе 51 - работу с блоком 3 в байтовом или пословном формате, на выходе 52 - работу с блоком 2 в байтовом формате.

Устройство работает следующим образом.

При наличии 1 на выходе 50 матрицы 32 и на управляющем входе устройства ре ализуется режим чтения бита информации из блока 2. При этом срабатывает элемент И 38 и его выходной сигнал через элемент ИЛИ 35 и выход 19 блока 1 устанавливается шинный формирователь 63 на выдачу бита из устройства, причем на выходе 23 формирователя 63 в этом случае устанавливается уровень 1. Кроме того, выходной сигнал элемента И 38 через элемент ИЛИ 34, выход 14 блока 1, элемент ИЛИ 58 и выход 25 селектора 4 включает блок 2. После этого байт из блока 2 пересылается в селектор 4, где через регистр 53 поступает на мультиплексор 54. Мультиплексор 54 по коду адреса А9-А11 выделяет требуемый бит, который через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 затем поступает на вход 6 блока 6 и через шинный формирователь 63 по цепи ДО - на информационный вход-выход ДО- Д15 устройства.

Если требуется инвертирование выбранного бита, то через вход Инв. устройства на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 подается О. Так как в это время на втором его входе уже имеется 1, поступившая с выхода 26 селектора 4, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 установится Г.

Кроме того, считанный бит подвергается контролю для выявления возможной ошибки. Для этого байт через вход 27 поступает в блок 5. Элемент нечетности 59 в блоке 5 проверяет поступивший код на наличие ошибки и при ее отсутствии выдает 1, которая затем инвертируется элементом И- НЕ 61 и через триггер 62 поступает на выход 29 блока. На второй вход элемента И-НЕ 61

в этом случае поступает также 1 с находящегося в исходном состоянии элемента не- четности 60. Таким образом, отсутствию ошибки при чтении соответствует О на выходе 29 блока 5.

При наличии 1 на выходе 50 матрицы 32 и входе Запись устройства реализуется режим записи бита в блок 2. Причем запись бита в блок 2 производится в два этапа.

На первом этапе байт, в котором нужно изменить бит, пересылается из блока 2 в селектор 4 для замены бита и в блок 5 для проверки на отсутствие ошибки.

На втором этапе в селекторе 4 происхо5 дит замена бита в байте, в блоке 5 - выработка контрольного разряда к байту с измененным битом, после чего происходит пересылка в блок 2 из селектора 4 байта, а .из блока 5 - контрольного разряда к нему.

0 При наличии 1 на выходе 50 матрицы 32 и наличии сигнала Запись со входа устройства срабатывает элемент И 39 и по его выходному сигналу запускается элемент 48 задержки, а через элемент И 40, элемент

5 ИЛИ 34, выход 14 блока 1, элемент ИЛИ 58 и выход 25 селектора 4 включается блок 2.

После этого по коду адреса А1-А8 происходит выборка байта из блока 2, а затем пересылка его в селектор 4 и совместно с

0 контрольным разрядом - в блок 5, где он подвергается контролю аналогично описанному выше.

В селекторе 4 байт через регистр 53 поступает на мультиплексор 54, который по

5 коду адреса А9-А11 выделяет бит, подлежащий замене, и выдает его на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7.

На этом первый этап заканчивается и начинается второй.

0 По истечении задержки, создаваемой элементом 48, 1 с его выхода производит следующие действия:

-через выход 13 блока 1 в селекторе 4 включает матрицу 55, а также перево- 5 дит в режим запоминания регистр 53-и триггер 62;

- через элементы И 40, ИЛИ 34, выход

14 блока 1, элемент ИЛИ 58 и выход 25

селектора 4 отключает блок 2, на выходе

0 контрольного разряда которого в это время

устанавливается

- через элемент ИЛИ 37 и выход 18 блока переводит блок 2 в режим записи;

- через элемент ИЛИ 35 и выход 19 5 блока 1 переключает шинный формирователь 63 блока 6 на пересылку с шины ДО в устройство;

- запускает элемент задержки 49. В результате на матрицу 55 поступает 1 байт из регистра 53 и код адреса А9-А11

бита, подлежащего замене, после чего на выходе матрицы 55 появляется байт с измененным битом. Для выработки контрольного разряда к этому байту он подается с матрицы 55 на групповой информационный .5 вход элемента 59, на вход контрольного разряда которого поступает 1 с выхода блока 2, и подвергается проверке на нечетность. Результат проверки с элемента 59 поступает на выход 30 блока 5 и в дальнейшем 10 является контрольным разрядом к данному байту. Одновременно с этими действиями бит, подлежащий записи в байт, по цепи ДО через шинный формирователь 63, выход 23 блока 6 поступает на второй вход элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ 11 через элемент ИЛИ-НЕ и, в зависимости от состояния сигнала на первом его входе, выдается в пря- MQM или.инверсном виде через выход 24 на вход селектора 4. Так как на первом его 20 входе уже имеется бит, подлежащий замене, то происходит сравнение этих битов.

Если биты совпадают, то содержимое в блоке 2 по данному адресу изменять не следует. При несовпадении битов на выходе 25 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 появится 1 и поступит на первый вход элемента И 57 через И 12. По истечении времени задержки, задаваемой элементом 49, с выхода элемента И 46 через выход 15 блока 1 30 на второй вход элемента И 57 поступает результат проверки на наличие ошибки, представленной 1 при ее отсутствии и О при ее наличии.

Таким образом, если ошибка отсутству- 35 ет, то на выходе элемента И 57 появится 1. по которой через элемент ИЛИ 58 и выход 25 селектора 4 включается блок 2 и байт с матрицы 55, а также контрольный разряд к нему с выхода 30 блока 5 запишутся в блок 40 2. Если ошибка имеется, то на выходе элемента И 57, а, следовательно, и на выходе элемента ИЛИ 58, будет О, включение блока 2 не произойдет и запись в него не будет произведена.45

При наличии 1 на выходе 51 матрицы 32 реализуется режим работы блока 3 с байтовым или пословным форматом. С появлением 1 на выходе 51 она поступает на элементы И 41-43, а также через элемент 50 ИЛИ 36 - на элементы И 44 и 45. В случае работы с четным байтом (ДО-Д7) его выбор задается 1 на входе Четный байт устройства, которая через элемент И 43 и выход 16 блока 1 поступает в блок 3, а через элемент 55 И 45 и выход 20 блока 1 - на шинный формирователь 64.

При необходимости работы с нечетным байтом (Д8-Д15) 1 подается на вход -Нечетный байт устройства и с него через элемент И 42 и выход 17 блока 1 поступает на блок 3, а через элемент И 41 и выход 21 блока 1 - на шинный формирователь 66.

При работе со словом, то есть одновременно с четным и нечетным байтами, 1 подается на каждый вход устройства. Направление передачи информации определяется сигналом на входе запись устройства. Если он представлен 1, то информация будет поступать в блоке 3, а если О, то информация будет выдаваться из блока 3.

Контроль ошибки при чтении из блока 3 и выработка контрольного разряда при записи в него производится так же, как при работе с битами с той лишь разницей, что на блок 5 информация подается без участия селектора 4, а контрольный разряд для нечетного байта слова вырабатывается элементом нечетности 60 и поступает на выход 31 блока 5.

При работе байтовым форматом с блоком 2 уровень 1 появляется на выходе 52 матрицы 32 и поступает на элементы И 47 и ИЛИ 34, а также через элемент ИЛИ 36 - на элементы И 44 и 45. Появившаяся 1 на выходе элемента ИЛИ 34 проходит через выход 14 блока 1, элемент ИЛИ 58 и выход 25 селектора 4 на блок 2 и включает его.

Если 1 присутствует на входе четный байт устройства, то через элемент И 45 и, выход 20 блока 1 включается шинный формирователь 64 и байт из блока 2 выдается на шину ДО-Д7 устройства. Если 1 присутствует на входе нечетный байт устройства, то через элемент И 47 и выход 22 блока 1 включается шинный формирователь 65 и байт из блока 2 выдается на шину Д8-Д15 устройства.

Запись байта в блок 2 и выработка контрольного разряда к нему производится так же, как и при работе с блоком 3.

Г

Формула изобретения Запоминающее устройство, содержащее первый и второй блоки памяти, блок контроля и блок управления, причем входы Запись, Чтение, Адрес слова, Формат данлых, Нечетный байт и Четный байт блока управления являются одноименными входами устройства, входы выбора режима первого и второго блоков памяти объединены и подключены к первому выходу блока управления, адресные входы первого и второго блоков памяти объединены и подключены к второму выходу блока управления, контрольные входы и выходы первого и второго блоков памяти соединены с соответствующими выходами и входами блока контроля, выход результата контроля блока контроля является выходом Ошибка уст-ройства, содержащее также селектор, блок двунаправленных ключей и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем стробирую- щие входы селектора и блока контроля объединены и подключены к третьему выходу блока управления, вход Адрес бита которого является одноименным входом устройства, входы Обращение, Разрешение обращения и Адрес бита селектора соединены соответственно с четвертым, пятым и шестым выходами блока управления, вход Результат контроля блока управления соединен с одноименным выходом блока контроля, седьмой и восьмой выходы блока управления подключены соответственно к входам обращения к четному и нечетному байтам второго блока памяти, девятый выход блока управления соединен с управляющим входом блока двунаправленных ключей, управляющий выход селектора соединен с входом обращения первого блока памяти, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является входом Инверсия устройства, первый выхбд блока управления подключен к входу синхронизации блока двунаправленных ключей, информационные выходы первой группы блока двунаправленных ключей соединены поразрядно с информационными входами первой группы блока контроля, первого блока памяти и первой группы второго блока памяти, информационные входы второй группы блока двунаправленных ключей соединены поразрядно с информационными входами второй группы блока, контроля и второй группы второго блока памяти, информационные выходы третьей групгды блока двунаправленных ключей являются информационными выходами устройства, информационные выходы первого блока памяти подключены поразрядно к информационным входам группы селектора и первой группы блока контроля, информационные выходы первой группы второго блока памяти соединены поразрядно с информационными входами первых групп блока контроля и блока двунаправленных ключей, информационные выходы второй группы второго блока памяти подключены поразрядно к информационным входам вторых групп блока

контроля и блока двунаправленных ключей, входы третьей группы которого являются информационными входами устройства, о т- личающееся тем, что, с целью расширения области применения устройства за

счЈт возможности выполнения селективно операций чтения и записи битовой информации в пределах байта, в него введены триггер, элемент ИЛИ-НЕ, элемент И, элемент И-НЕ и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем счетный вход триггера соединен с десятым выходом блока управления, управляющий вход триггера с информационным выходом блока двунаправленных ключей, и первым входом элемента ИЛИНЕ, второй вход которого соединен с выходом триггера, выход элемента ИЛИ-НЕ соединен с первым входом элемента И-НЁ и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и с информационным входом блока двунаправленных ключей, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ - с первым входом элемента И, второй

вход которого соединен с выходом элемента И-НЕ, а выход элемента И - с информационным входом селектора, информационный выход которого соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

второй вход элемента И-НЕ соединен с одиннадцатым выходом блока управления.

Pua.f

rs

3

ЧТИ

6fin

ft

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1510010A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Запоминающее устройство для программируемого контроллера | 1984 |

|

SU1228146A1 |

| Устройство для контроля памяти | 1984 |

|

SU1249589A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Устройство для сопряжения магистрали с ЦВМ | 1988 |

|

SU1569837A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Цель изобретения - расширение области применения устройства за счет возможности выполнения селективно операций чтения и записи битовой информации в пределах байта. Устройство содержит блок управления, блок памяти, селектор, блок контроля, блок двунаправленных ключей, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер, элемент ИЛ И-НЕ, элемент И-НЕ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И. 5 ил.

so

ЈL

вгг.../)гУ

за

sz

(Jug.

tfever. Sac/m

Уе/лн, Ъ&и/п

Фиг. Ј

г

Ц

т- ч Ч

г- М

Ьг

го

iifftt/t/SfCOr

/7

fS

fS

9иг.з

Фиг. 4

Редактор

ЛО... Л7

64

65

№..ДГ5

ЖИШУ(

66

/г: S

| Запоминающее устройство | 1987 |

|

SU1510010A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-03-30—Публикация

1990-04-09—Подача