I

Изобрегение относигся к запоминаюшим устройствам (ЗУ).

Известно оперативное запоминающее устройство, содержащее регистры четного и нечетного байта, блок формирования, коммутаторы четного и нечетного байта, блок запоминания tl .

Однако при необходимости работы с переменными форматами слов от байта . и до длины большей, чем два байта, аппаратурные затраты становятся большими.

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с одновременной выборкой переменного массива слов, содержа шее модули памяти, регистр адреса, разделенный на части - старшую и младшую, коммутаторы входной и выходной информации (кольцевые сдвигатели), шифраторы и дешифраторы, блок добавления единицы (преобразователь кода адреса) 2J.

Однако при необходимости использоваигая ЗУ в системах, предполагающих смену формата ЗУ в процессе работы на продолжигельное время или постоянную работу со словами различного формата при решении какой- либо задачи большая часть коммутирующего оборудования используется непроизводительно.

Целью изобретения является повышение надежности устройства.

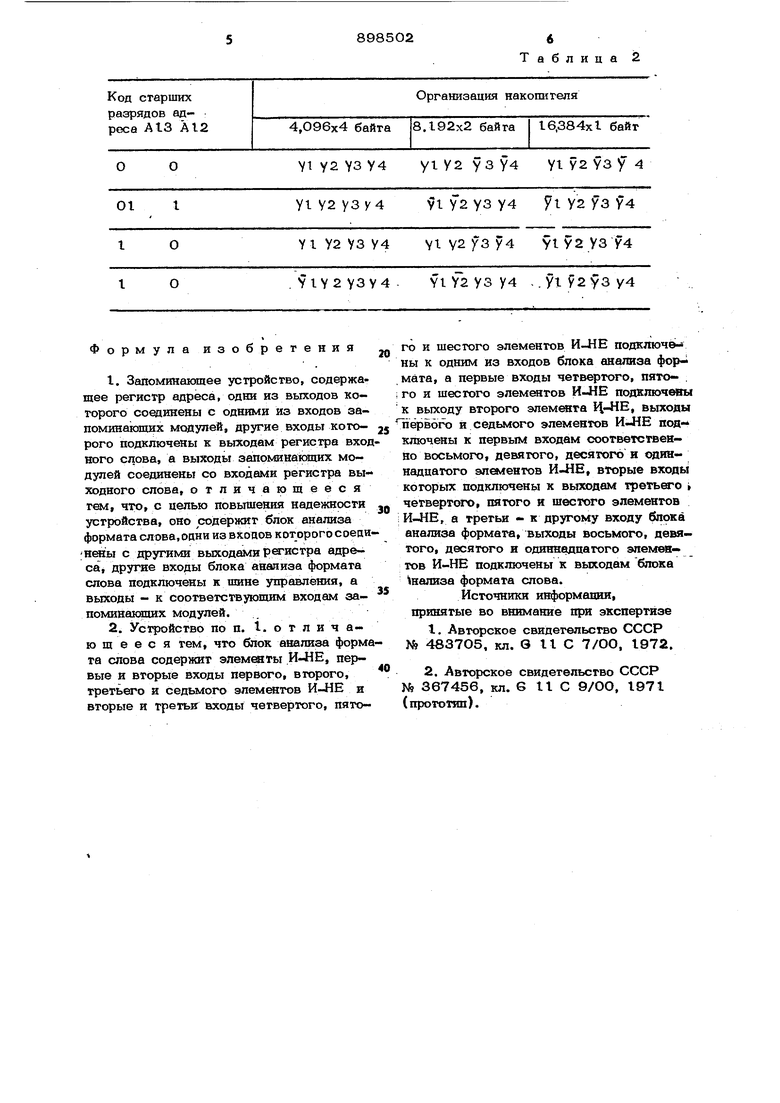

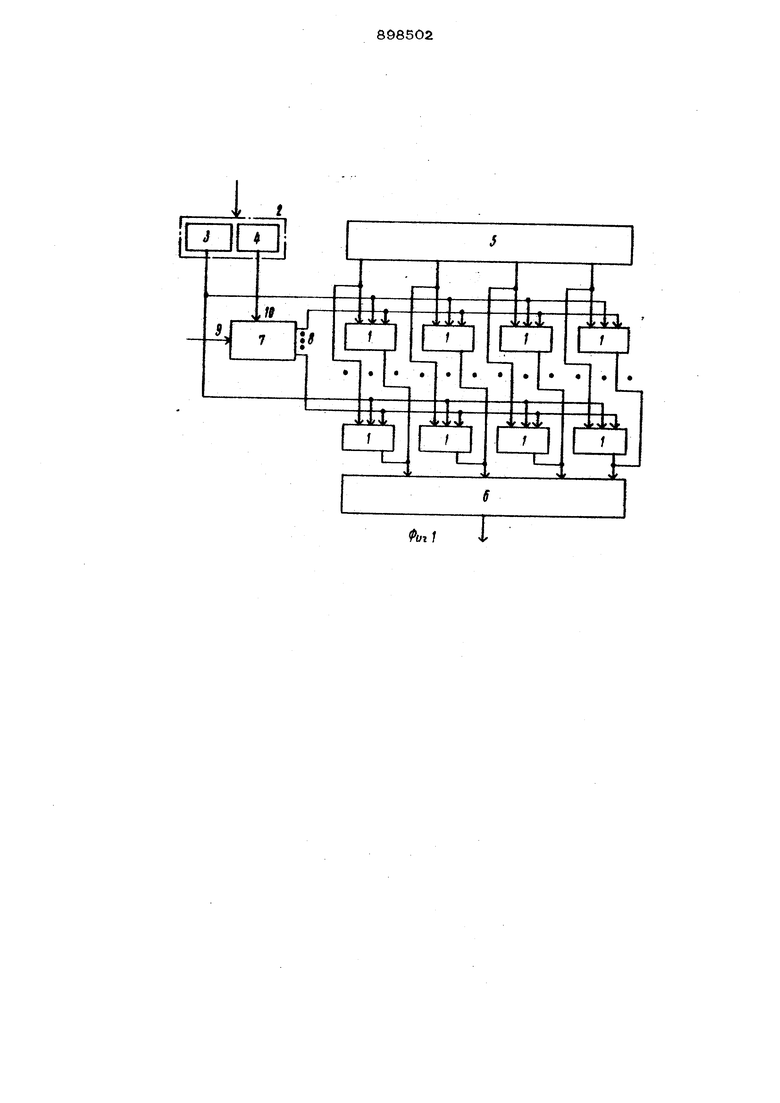

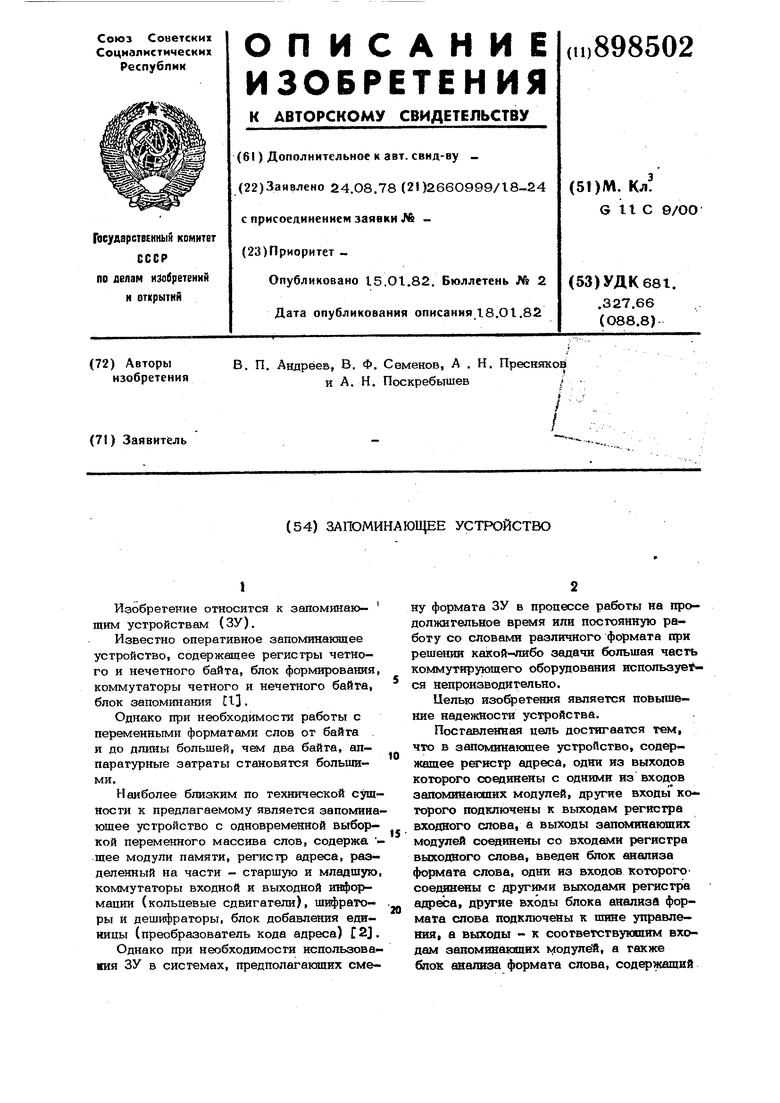

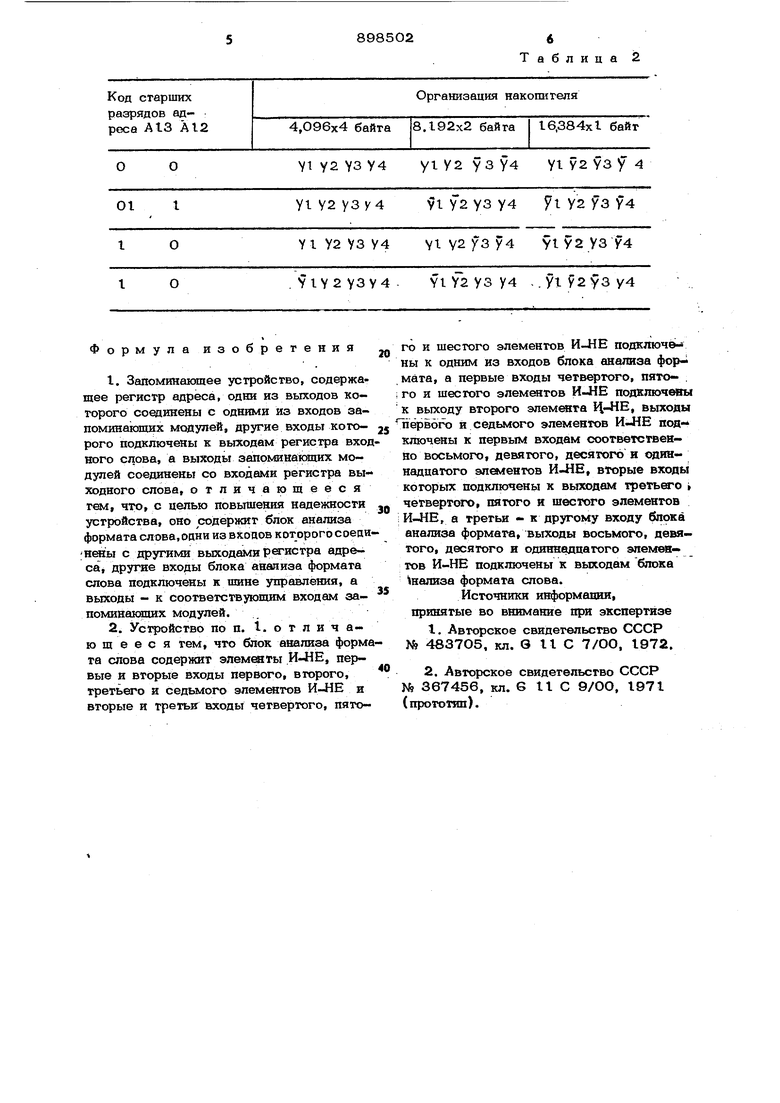

Поставленная цель достагаатся тем, что в запоминающее устройство, содержащее регистр адреса, одни из выходов которого соединены с одними из входов запоминаюших модулей, другие входы которого подключены к выходам регистра входного слова, а выходы запоминающих модулей соединены со входами регистра выхолшюго слова, введен блок анализа формата слова, одни из входе® которого соединены с другими выходами регистра адреса, другие входы блока анализа формата слова подключены к шине управления а выходы - к соответствующим входам запоминаюших модуле, а также блок анализа формата слова, содержащий 389 элементы И-НЕ, первые и вторые входы первого, второго, третьего и седьмого элементов ИЛЕ и вторые и третьи входы четвертого, пятого и шестого элементов И-НЕ подключены к одним из входов блока анализа формата, а первые входы четвертого , пятого, шестого элементов И-НЕ подключены к выходу второго элемента И-НЕ, выходы первого и седьмого элементов подключены к входам соответственно восьмого, девятого, десятого и одиннадцатого элементов И-НЕ, вторые входы которых подключены к выходам третьего, четвертого, пятого и шестого элементов И-НЕ, а третьи - к другому входу блока анализа формата, выходы восьмого, девятого, десятого и одиннадцатого элементов подключены к выходам блока анализа фор мата слова. На фиг. I представлена блок-схема устройства; на фиг, 2 - структурная схе ма блока анализа формата слова, Схема содержит запомкнаюшие модули I памяти, регистр адреса 2, разделенный на части - младшую 3 и старшую 4,причем выходы младшей части 3 регистра адреса 2 соединены со входами запоминакипих модулей, регистр входного елова 5, выходы, которого соединены С Другими входами модулей t, регистр выходного слова 6, входы Которого соединены с выходами модулей I, коммутатор формата слова 7, выходы 8 которого соединены с третьими входами модулей I памяти, входы 9 являются шинами управления сменой формата слова ЗУ, а входы 10 соединены со старшей частью 4 регистра 2. Устройство работает следующим образом. Перед обращением к ЗУ с записью или со считыванием на входы 9 коммутатора 7 подается код управляющих потенциалов В , В зависимости от кода и

В2

В1

О

О

О

О

Организация накопителя

4О96 X 4 байта

4,096 X 4 байта

16.384 X I байт

8,192 X 2 байта 2 старших разрядов адреса, поступающих на входы 10 блока анализа формата слова 7 из старшей части 4 регистра адреса 2, на выходе 8 вырабатываются потенш алы, разрешающие обращение к модулю или группе модулей. Из младшей части 3 регистра адреса 4 поступают младшие разряды кода адреса для выбора в модуле или группе модулей ячей, „„ ки памяти. Один модуль вмешает П слов длиной в один байт. Если число модулей равно Т , то организация ЗУ может из себя представлять модификации: п слов длиной в f байтов; 2 ц, слов длиной в i байтов и т.д. по и. Г слов длиной в один байт, при кратности изменения емкости ЗУ и формата слова равной двум. Можно построить блок анализа формата слова 7 и так, что изменение емкое-, . ти ЗУ будет происходить с кратностью не равной двум. На фет. 2 показан пример построения блока анализа формата слова, сюушествляющего изменение организации накопи теля от 16К х I байт, до 4К X 4 байта с кратностью 2 и который содержит одиннадцать элементов И-НЕ 11-21. В табл. I показана зависимость организации ЗУ от кода сигналов управления перестройкой формата слова В{, Блок анализа формата слова на двух- и трехвходовых элементах И-НЕ и вырабатывает сигналы yi- V4, В табл, 2 показана зависимость формирования потенциальных сигналов У 1- У4 от старших разрядов адреса А12, А13 и организации накопителя ЗУ. Емкость одного модутш О,5Кх1 байт. Всего модулей 32. Они организованы в столбцы .У I- У4; Потеншюльные сигналы УЧ-- У4 поступают на соответствующие столбцы накопителя. В предлагаемом устройстве аппаратурные затраты в комплектующем оборудовании уменьшаются примерно в десять раз. Таблица I

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для управления вводом информации | 1983 |

|

SU1161949A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Устройство для кусочно-линейной интерполяции функций | 1983 |

|

SU1215117A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

Формупа изобретения 1.Запоминающее усгройсгво, содержащее регистр адреса, одни из выходов которого соединены с одними из входов запоминающих модулей, другие входы когорого подключены к выходам регистра вхо ного слова, а вызсоды запоминающих модулей соединены со входами регистра выходного слова, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок анализа формата слова.одни из входов кот орого соеди :н0аы с другими выходами Р истра адреса, другие входы блока анализа формата слова подключены к шине управления, а - к соответствующим входам запоминакяцих модулей. 2.Ус1ройство по п. 1. о т л и ч аю щ е е с я тем, что блок анагахза форм та слова содержит элемшты И-НЕ, первые и вторые входы первого, второго, третьего и седьмого элементов И-НЕ и вторые и третьи входы четвертого, пятоГО и шестого элементов И-НЕ подключены к одним из входов блока анализа фор- мата, а первые входы четвертого, пято- . го и шестого элементов И-НЕ подключены к выходу второго элемента , выходы iepioro и седьмого элементов ИЛЕ под- ключены к первым входам соответственно восьмого, девятого, десятого и одиннадцатого элементов И-НЕ, вторые входы которых подключены к выходам третьето четвертого, пятого и шестого элементов И-НЕ, а третьи - к другому входу блока анализа формата, выходы восьмого, девятого, десятого и одиннадцатого элементов И-НЕ подключены к выходам блока Анализа формата слова. Источники информбшии, принятые во внимание при экспертизе I, Авторское свидетельство СССР № 483705, кл. Q II С 7/ОО, 1972. 2. Авторское свидетельство СССР N 367456, кл. 6 II С 9/ОО, 1971 (прототип).

I

zi

18

18

rt

G:

и

LJ fw

m

t/7/

Авторы

Даты

1982-01-15—Публикация

1978-08-24—Подача