31510

Изобретение относится к области связи и может быть использовано при построении устройств управления автоматических телефонных станций (АТС). Цель изобретения - сокращение числа формируемых сигналов Занято.

На фиг.1 приведена структурная схема формирователя сигналов, на фиг.2 - пример выполнения блока прие- ма информации; на фиг„3 - выполнение блока вьщеления управляющих сигналов; -на фиг о 4 - вьтолнёние первого коммутатора; на фиг.5 - выполнение блока . вьщачи информациис

Формирователь сигналов ДТС (фигс1) содерзшт блок 1 приема информации, блок 2 оперативной памяти, блок 3 выделения управляющих сигналов, счетчик 4, инвертор 5, первый коммутатор 6, второй коммутатор 7, генератор 8 импульсов, регистр 9, блок 10 сравнения , блок 11 вьщачи информации.

Блок 1 приема информации (фиг«2) содержит первый ключ 12, первый ивто рой приемные регистры 13 и 14 о

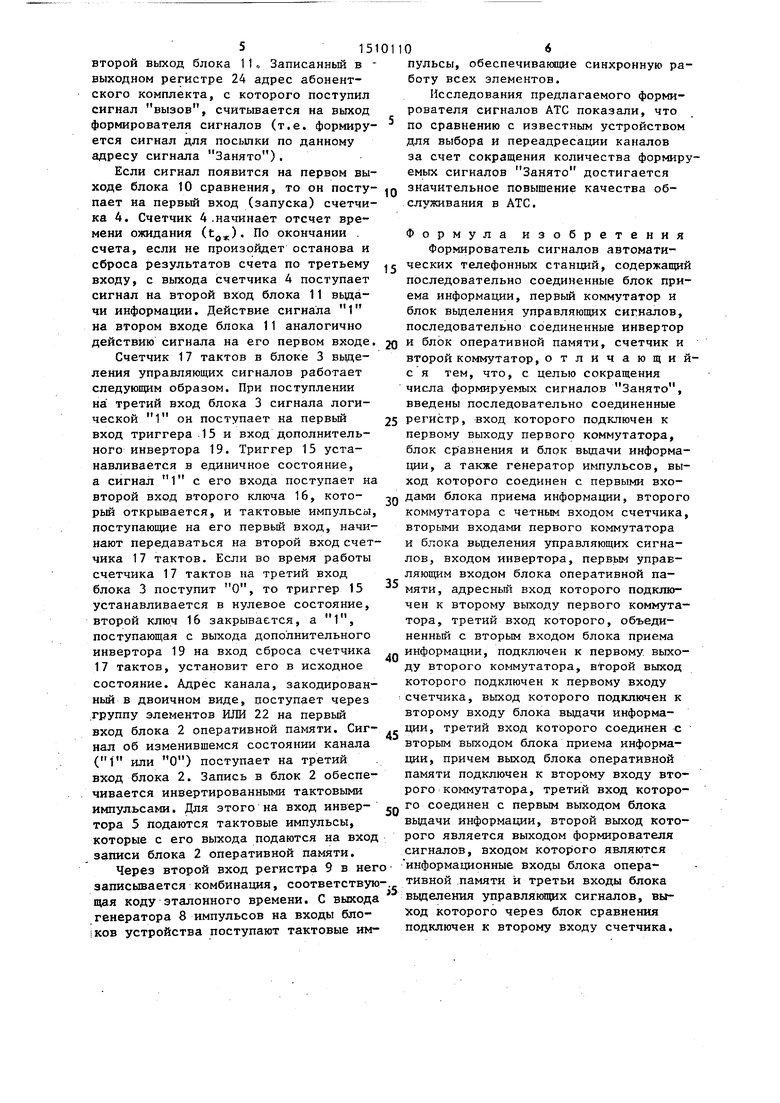

Блок 3 выделения управляющих сигналов (фиг.З) содержит триггер 15, второй ключ 16, счетчик 17 тактов, первую группу ключей 18, дополнитель- ньй инвертор 19„

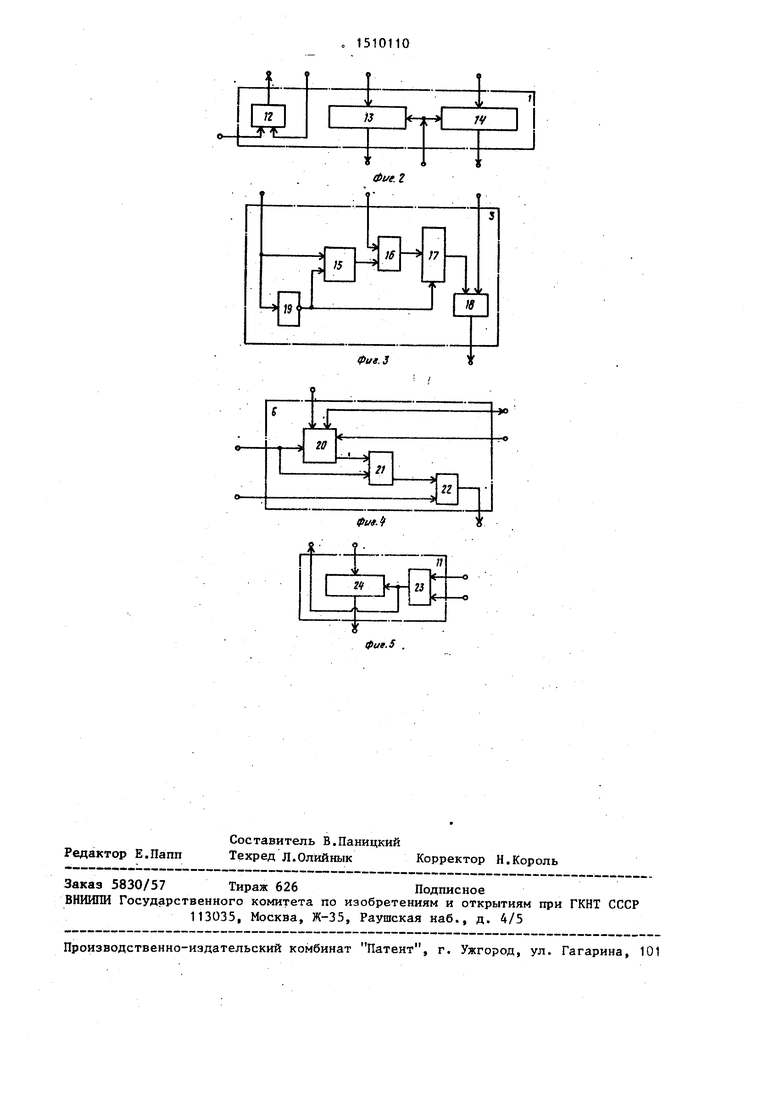

Первый коммутатор 6 (фиг.4) содержит счетчик 20 адреса, вторую группу ключей 21, группу элементов ИЛИ 22.

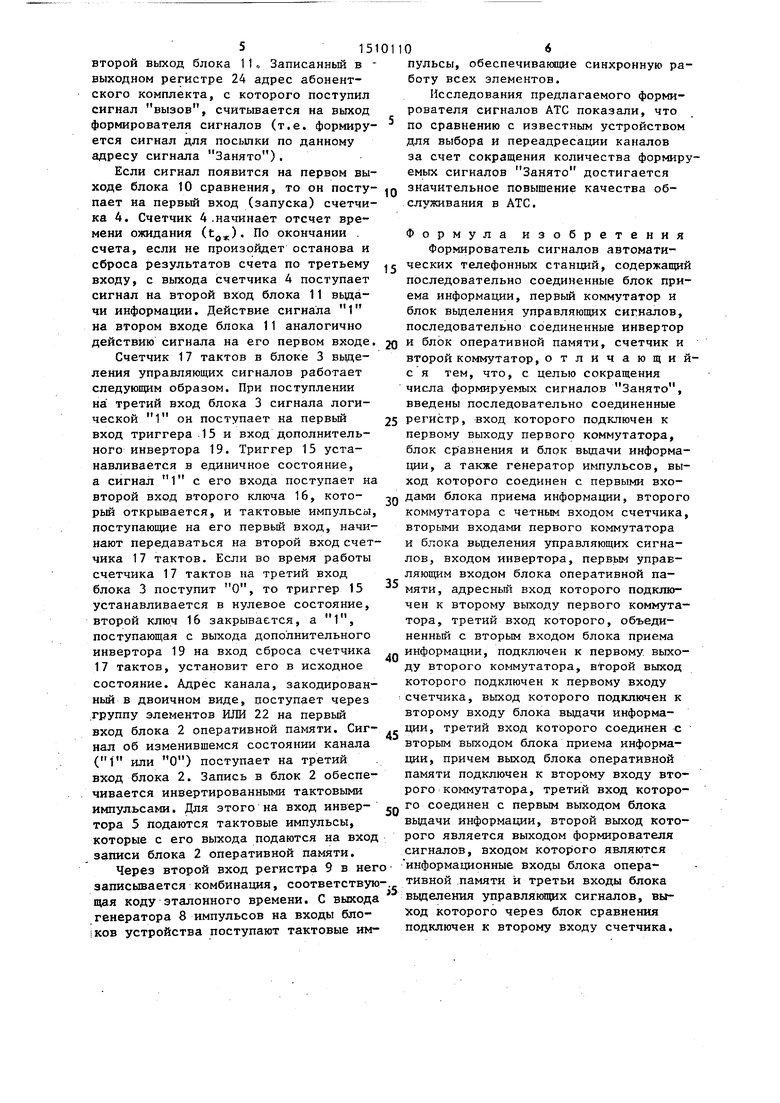

Блок 11 вьщачи информации (фиг.З) содержит элемент ИЛИ 23 и выходной регистр 24.

Формирователь сигналов работает следукицим образом.

На вход блошка 1 приема информации поступают сигналы вызова, сопровождающиеся номером абонентского комплекта, с которого поступил вызов; При совпадении поступившего запроса с импульсом генератора 8 импульсов на первом ключе 12 код вызова и номер абонентского комплекта записьгоаются соответственно в первый и второй приемные регистры i3 и 14. При поступлении на их вторые входы считываимцего импульса адрес из второго приемного регистра 14 передается в блок 11 и записывается в выходной регистр 24, а код вызова поступает на запускают щий вход счетчика 20 адреса первого коммутатора 6.

Счетчик 20 адреса начинает отсчитывать адреса ячеек блока 2 оперативной памяти, в котором записана информация о состоянии каналов связи АТС Состояние Занято отображается логической 1, Свободно - логическим О. При поступлении сигналов считывания на первый вход блока 2 оперативной памяти информация о состоянии каналов связи (логические 1 и О) поступает с выхода блока 2 на вход второго коммутатора 7. С первого выхода второго коммутатора 7 логические 1 и О поступают на третий вход первого коммутатора 6 и второй вход (считьюания) блока 1 приема информации, с третьего входа первого коммутатора 6 логические 1 и О поступают на вход останова счетчика 20 адреса. Останов счетчика 20 адреса, а также считьшание информации о сигнале Вызов из первого и второго приемных регистров 13 и 14 блока 1 приема информации происходит при наличии на первом выходе второго коммутатора 6 логической 1, которая появляется только в том случае, когда на второй вход поступает логический О (что соответствует наличию свободного ка- нала связи в AtC) или на третий - логическая 1. С второго выхода второго коммутатора 6 логическая 1 поступает также на третий вход (останова) счетчика 4.

Если счетчик 20 адреса в первом коммутаторе 6 досчитает до N (N равно числу ячеек в блоке 2 оперативной памяти) , что возможно только при заня- . тости всех каналов, то на втором выходе первого коммутатора 6 появляется 1, после чего счетчик 20 адреса начинает новый цикл счета, а сигнал поступает на первые входы регистра 9 и блока 3 вьщецения управляющих сигналов В блоке 3 сигнал поступает на вход первой группы ключей 18, открывает его и комбинация (код времени счета) с выхода счетчика тактов 17 поступает на выход блока 3 и, далее, на первый вход блока 10 сравнения, на второй вход которого одновременно поступает комбинация (код эталонного времени) с выхода регистра 9. После сравнения этих комбинаций на первом или втором выходе блока 10 появляется сигнал (логическая 1). Если 1 появляется на втором выходе, то она поступает на первый вход блока 11 вьщачи информации, а затем через элемент ИЛИ 23 на вход считывания выходного регистра 24 и

второй выход блока 1 К Записанный в выходном регистре 24 адрес абонентского комплекта, с которого поступил сигнал вызов, считьшается на выход формирователя сигналов (т.е. формиру- ется сигнал для посылки по данному адресу сигнала Занято),

Если сигнал появится на первом выходе блока 10 сравнения, то он посту- пает на первый вход (запуска) счетчика 4. Счетчик 4 .начинает отсчет времени ожидания (t.). По окончании . счета, если не произойдет останова и сброса результатов счета по третьему входу, с выхода счетчика 4 поступает сигнал на второй вход блока 11 вьща- чи информации. Действие сигнала 1 на втором входе блока 11 аналогично

пульсы, обеспечивакяцие синхронную работу всех элементов.

Исследования предлагаемого формирователя сигналов АТС показали, что по сравнению с известным устройством для выбора и переадресации каналов за счет сокращения количества формируемых сигналов Занято достигается значительное повышение качества обслуживания в АТС.

Формула изобретения

Формирователь сигналов автомати- ческих телефонных станций, содержащий последовательно соединенные блок приема информации, первый коммутатор и блок вьщеления управляющих сигналов, последовательно соединенные инвертор

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Система телемеханики | 1982 |

|

SU1152015A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

Изобретение относится к технике связи. Цель изобретения - сокращение числа формируемых сигналов "Занято". Формирователь содержит блок 1 приема информации, блок 2 оперативной памяти, блок 3 выделения управляющих сигналов, счетчик 4, инвертор 5, коммутаторы 6 и 7, генератор 8 импульсов, регистр 9, блок 10 сравнения и блок 11 выдачи информации. При занятости всех каналов на втором выходе коммутатора 6 появляется сигнал "Г", который поступает на регистр 9. Он вырабатывает код эталонного времени, который затем сравнивается в блоке 10 сравнения с кодом времени счета, формируемым в блоке 3 выделения. Сигнал "1" со второго выхода блока 10 сравнения поступает на блок 11 выдачи непосредственно, а с первого выхода - через счетчик 4, который осуществляет отсчет времени ожидания. Цель достигается введением генератора 8, регистра 9, блока 10 сравнения и блока 11 выдачи 11. 5 ил.

действию сигнала на его первом входе. 20 блок оперативной памяти, счетчик и

Счетчик 17 тактов в блоке 3 вьщеления управляющих сигналов работает следующим образом. При поступлении на третий вход блока 3 сигнала логической 1 он поступает на первый вход триггера 15 и вход дополнительного инвертора 19. Триггер 15 устанавливается в единичное состояние, а сигнал 1 с его входа поступает на второй вход второго ключа 16, который открьшается, и тактовые импульсы, поступающие на его первый вход, начинают передаваться на второй вход счетчика 17 тактов. Если во время работы счетчика 17 тактов на третий вход блока 3 поступит О, то триггер 15

второй коммутатор, отличающий с я тем, что, с целью сокращения числа формируемых сигналов Занято, введены последовательно соединенные

25 регистр, вход которого подключен к первому выходу первого коммутатора, блок сравнения и блок выдачи информации, а также генератор импульсов, выход которого соединен с первыми вхо2Q дами блока приема информации, второго коммутатора с четным входом счетчика, вторыми входами первого коммутатора и блока выделения управляющих сигналов, входом инвертора, первьм управляющим входом блока оперативной па35

мяти, адресньш вход которого подклюустанавливается в нулевое состояние, второй ключ 16 закрывается, а

1

чен к второму выходу первого коммутатора, третий вход которого, объединенный с вторым входом блока приема инвертора 19 на вход сброса счетчика информации, подключен к первому, выхо- 17 тактов, установит его в исходное ду второго коммутатора, второй выход состояние. Адрес канала, закодирован- которого подключен к первому входу

счетчика, выход которого подключен к второму входу блока вьздачи информа- вход блока 2 оперативной памяти. Сиг- ции, третий вход которого соединен с нал об изменившемся состоянии канала вторым выходом блока приема информации, причем выход блока оперативной памяти подключен к второму входу второго коммутатора, третий вход которого соединен с первым выходом блока вьдачи информации, второй выход которого является выходом формирователя сигналов, входом которого являются

поступающая с выхода дополнительного

ный в двоичном виде, поступает через группу элементов ИЛИ 22 на первьй

(1 или О) поступает на третий вход блока 2. Запись в блок 2 обеспечивается инвертированньми тактовыми импульсами. Для этого на вход инвертора 5 подаются тактовые импульсы, которые с его выхода подаются на вход

50

записи блока 2 оперативной памяти.

Через второй вход регистра 9 в него информационные входы блока опера- записывается комбинация, соответствую- тивной памяти и третьи входы блока

л ,-,-, л etirTOTTOtirjCJ rTTT4aenOt/TlTITTT V Г ТТ-ПТТвТТЛТЭПК.

щая коду эталонного времени. С выхода генератора 8 импульсов на входы бло- IKOB устройства поступают тактовые имвьщеления управлянлцих сигналов, выход которого через блок сравнения подключен к второму входу счетчика.

второй коммутатор, отличающий- с я тем, что, с целью сокращения числа формируемых сигналов Занято, введены последовательно соединенные

25 регистр, вход которого подключен к первому выходу первого коммутатора, блок сравнения и блок выдачи информации, а также генератор импульсов, выход которого соединен с первыми вхо2Q дами блока приема информации, второго коммутатора с четным входом счетчика, вторыми входами первого коммутатора и блока выделения управляющих сигналов, входом инвертора, первьм управляющим входом блока оперативной па35

мяти, адресньш вход которого подклюинформационные входы блока опера- тивной памяти и третьи входы блока

etirTOTTOtirjCJ rTTT4aenOt/TlTITTT V Г ТТ-ПТТвТТЛТЭПК.

вьщеления управлянлцих сигналов, выход которого через блок сравнения подключен к второму входу счетчика.

фив.5 .

| Устройство для выбора и переадресации каналов | 1984 |

|

SU1177956A1 |

Авторы

Даты

1989-09-23—Публикация

1987-08-17—Подача