151

Изобретение относится к вычислительной технике и может быть использовано для автоматизированной отладки программ в режиме реального вре- мени „

Целью изобретения является повышение производительности отладки программ.

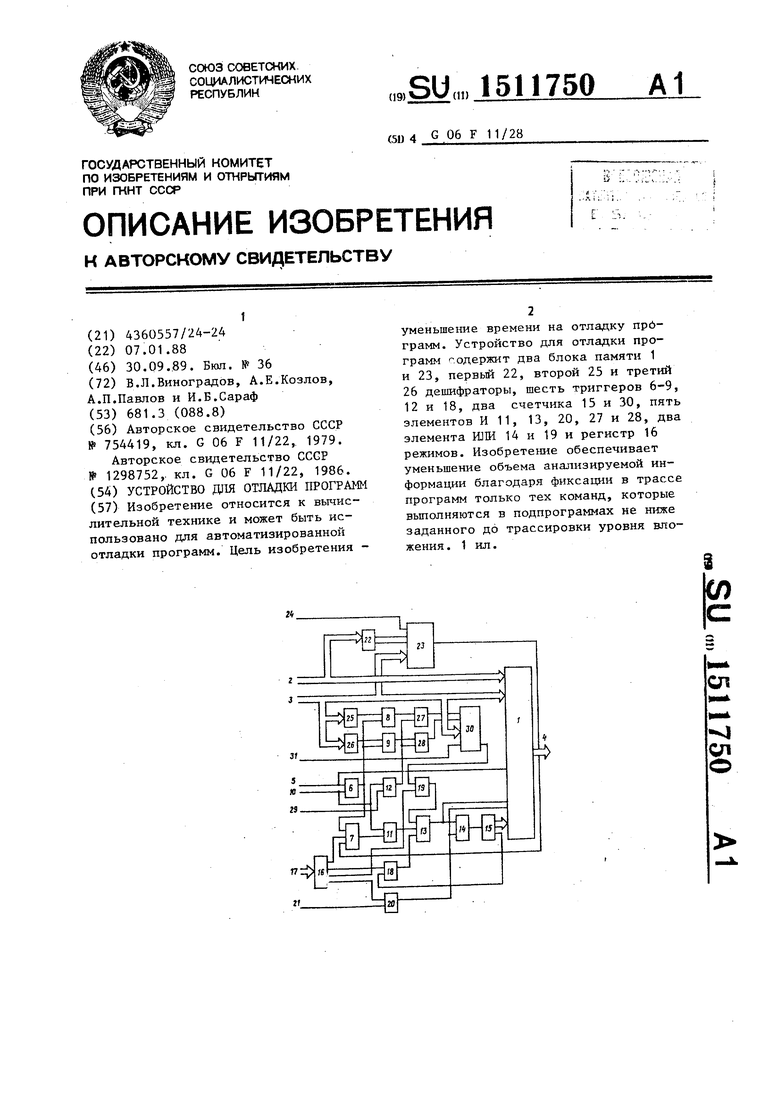

На чертеже представлена схема устройства для отладки программ.

Устройство содержит первый блок 1 памяти, первыми информационными входами подключенньй к адресным входам 2 устройства и соединенный вторыми информационными входами с информационными входами 3 устройства. Ин- формационньй ВЫХОД блока 1 подключен к информационному выходу 4 устройства. Вход 5 признака кода команды уст ройства соединен с входом обращения блока 1 памяти и информационным входом первого триггера 6, выход которого соединен с синхровходами второго 7, третьего 8 и четвертого 9 тригге- ров. Вход 10 начала гщкла команды устройства соединен с синхровз одом первого триггера 6, вторым входом элемента И 11 и с синхровходом пятого триггера 12. Выход элемента И 11 соединен с первым входом элемента И 13, выход которого соединен с первьм входом элемента ИЛИ 14 и входом признака записи блока 1 памяти., выход элемента .ИЛИ 14 соединен со счетньш входом первого счетчика 15, информационные выходы которого соединены с адресными входами блока 1 памяти.Вхо дь регистра 16 релсимов соединены с информационными входами 17 задания режимов устройства. Первый выход регистра 16 режимов соединен с установочным входом второго триггера 7 , Второй выход регистра 16 режимов соединен с информационным входом шесто- го триггера 18, выход которого соединен с вторым входом-элемента И 13, Третий выход регистра 16 режимов соединен с первым входом элемента ИЛ 19, выход которого с треть- им входом элемента И 13, Четвертый выход регистра 16 режимов соединен с первым входом элемента И 20, второй вход которого соединен с вторым управляющим входом 21 устройства. Выход элемента И 20 соединен с вторым входом элемента ИЛИ 14 и входом признака чтения блока 1 памяти.Группа адресных входов 2 устройства соединена с вход. первого г -и1ифра7. - рэ 22. IlepBbrii и второй выходы к-то- роро соединены с иь;формационным входом и входом обращения блока 23 памяти соответственно. Адресные входы блока 23 памяти соединены с группой информациоиньк входов 3 устройства. Вход 24 записи устройства соединен с входом записи блока 23 памяти, выход которого соединен с информационным входом второго триггера 7. Группа информационных входов 3 устройства соединена с информационными входами второго 25 и третьего 26 дешифраторов, выходы которых соединены с информационными входами третьего 8 и четвертого 9 триггеров соответственно. Синхровходы третьего 8 и четвертого 9 триггеров соединены с выходом первого триггера 6. Выход третьего триггера 8 соединен с первым входом эле.мента И , а выход четвертого триггера 9 соединен с первым входом элемента И 28. Вторые входы элементов И 27 и И 28 соединены с выходом пятого триггера 12, информационньй вход которого соединен с третьим входом 29 признака обращения к стековой памяти устройства Выходы элементов И 27 и И 28 соединены со .входом сложения li вычитания реверсивного счетчика 30, старший информационный выход которого со еди- ней с вторым входом элемента ИПИ 19 с Группа установочных входов реверсивного счетчика 30 соединена с группой информа1дионных входов 3 ус тройства, а установочньй синхровход реверсивного счетчика 30 соединен с нходом установки кода уровня вложения устройства 31. Выход переполнения первого счетчика 15 соединен с синхровходом пятого триггера 18. Выход второго триггера 2 соединен с вторым входом элемента И t1,

Блок 1 памяти в составе устройст- ва для отладки прогреет вьптолняет- роль буферного оперативного запоминающего устройстваS в котором во время трассировки программы в реальном времени запоминается адрес выполняемой команды, код вьтолняемой команды результат вьшолнения ,

Устройство функционирует в четырех режимах.

В режиме один разрешена трассировка програм1чы с запох-мнанием в блоке 1 памяти всех выпoJj; яeмьгx команд. В

51

режиме два разрешена трассировка программы с запоминанием в блоке 1 памяти только тех Команд, коды которых до трассировки были заданы. В режиме три разрешена трассировка программы с запоминанием в блоке 1 памяти команд только тех подпрограмм, уров- вень вложения которых не превьппает заданного до трассировки в реверсивном счетчике 30. В режиме четыре разрешено чтение результатов трассировки для дальнейшей обработки.

В режимах запоминания команд режимы один или два на вход 5 устройства из отлаживаемой системы подается сигнал, информирующий о том, что производится выборка кода команды из памяти отлаживаемой системы. На вход 10 устройства из отлаживаемой системы подается строб, сопровождающий начало цикла команды, выполняемой в отлаживаемой системе. В режиме один разрешена трассировка программы с запоминанием в блоке 1 памяти всех выполняемых команд. При этом с первого выхода регистра 16 режимов на установочньй вход второго триггера 7 поступает сигнал, который устанавливает выход второго триггера 7 в состояние 1. Тогда сигнал с входа 10 устройства, которьй сопровождает начало каждого машинного цикла команды, через первьш 11, второй 13 элементы И поступает на вход записи блока 1 памяти и записывает в него информацию, поступающую с группы адресных 2 и группы информационных 3 входов устройства, а также поступая на счетный вход счетчика 15, наращивает адрес блока 1 памяти.

В режиме два разрешена трассировка программы с запоминанием в блоке 1 памяти только тех команд, коды которых до трассировки были заданы. При этом, до трассировки программ необходимо соответствующим образом заполнить блок 23 памяти. При этом на группе адресных входов 2 устройства формируется адрес, который поступает на вход дешифратора 22 устанавливает на первом и втором выходе дешифратора 22 уровни О и 1 соответственно. Уровень 1, поступая на вход обращения блока 23 паьяти, разрешает выбор блока 23 памяти. По группе информационных входов. 3 устройства перебираются все возмож-

7506

ные комбина цн; . причем каждая комбинация сопровбж,ается стробом на входе 24 устройства, который, поступая

на вход записи блока 23 памяти, обеспечивает запись по адресу, сформированному на группе и формационных входов, значение О. После чего весь объем блока 23 будет заполнен нуля0 МИ; что соответствует запрещению записи в блок 1 памяти всех команд из системы команд. Далее на группе адресных входов 2 устройства формируется код, KOTOpLMj поступая на вход де5 шифратора 22, устанавливает на первом и втором выходе дешифратора 22 уровни 1. На группе информационных входов 3 устройства формируется код той. команды, которую надо запомнить в

0 блоке 1 памяти во время трассировки программ. Этот код команды сопровождается стробом на входе 24 устройства, которьй, поступая на вход записи второго блока 23 памяти, обеспечива5 ет запись по адресу, сформированному на группе информационных входов, значение 1. Если при трассировке необходимо запоминать несколько команд, то эту процедуру необходимо повто0 рить столько раз,сколько кодов команд необходимо запомнить в трассе програм- мы, причем на группе информационных входов 3 устройства необходимо выставить соответствующий код команды.После

, этой процедуры устройство для отладки программ готово к функционированию во втором режиме. На первом выходе регистра 16 режимов установлен уровень О. Первьй триггер 6 формирует

Q импульс для машинного цикла, в котором на группе информационных входов 3 устройства появляется код команды, которьп поступает на блок 23 памяти. На его выходе появляется логический

г уровень либо О, либо 1 в зависимости от того, что было записано в блок 23 памяти на этапе подготовки трассировки программы. Если на выходе второго дополнительного блока 23

0 памяти появляется уровень О, то импульсом с выхода первого триггера 6 второй триггер 7 устанавливается в нуль, который, поступая на первьй вход первого элемента И 11, запрещает прохождение синхроимпульса для записи в блок 1 памяти. Если на выходе блока 23 памяти появляется уровень 1, то импульсом с выхода первого триггера 6 второй триггер 7 ус5

танавливается в единицу, которая, поступая на первьп вход первого элемента И 11, разрешает прохождение синхроимпульсов для записи в блок 1 памяти. После того, как счетчик 15 сформировал сигнал о переполнении, если на втором выходе регистра 16 режимов установлен уровень О, то третий триггер 18 устанавливает состоя-ние нуля запрещая прохождение синхроимпульса для записи в блок 1 памяти. Если на втором выходе регистра 16 режимов установлен уровень 1, то третий триггер 18 устанавливает состояние единицы и трассировка программы продолжается.

В режиме три разрешена трассировка программы с запоминанием в блоке 1 памяти команд только тех подпрограмм, уровень вложения которых не превьшает заданного до трассировки в реверсивном счетчике 30. При этом до трассировки необходимо задать уровень вложения подпрограмм, подлежащих трассировке. Для этого на группе информационных входов 3 формируется уровень вложения подпрограмм следующим образом: значение информационных разрядов (кроме старшего) равно уровню вложения подпрограмм, подлежащих трассировке (отсчет с нуля), а .значение старшего информационного разряда равно единице. После этой процедуры устройство для отладки программ готово к функционированию в третьем режиме. Для этого на третьем выходе регистра 16 режимов устанавливается уровень О. Второй дешифратор 25 работает таким образом, что на выходе ег появляется уровень 1, когда на группе информационных входов появляются коды команд условного или безусловного выбора подпрограмм. Если код команды перехода 3 появился при выборке команды (на выходе первого триггера 6 появится уровень 1), то на выходе триггера устанавливается уровень 1. На выходе пятого триггера 12 уровень 1 появляется только в том случае, если в машинном цикле команды (стробируеТся вторым синхровходом 10 устройства) есть обращения к стековой памяти (на третьем синхровходе устройства появляется уровень 1), это означает, что после команды условного вызова подпрограммы действительно произошел

0

5

0

5

0

5

переход на выпо1 нение подпрограМд и, (вьятолнилась сТековай операиля по сохранению адреса возврата), При этом на выходе элемента И 27 появляется уровень 1, которьй вызывает уменьшение содержимого, реверсивного счетчика 30 на единицу. Цепочка третий дешифратор 26, четвертьп триггер 9 и элемент И 28 работает аналогично с той лишь разницей, что уровень 1 появляется на выходе третьего дешифратора 26, когда на группе информационных входов появляются коды команд условного или безусловного возврата из подпрограмм. При этом появление уровня 1 на выходе элемента И 28 вызывает увеличение содержимого реверсивного счетчика 30 на единицу. Таким образом выполнение команд перехода на подпрограмму вызывает уменьшение значения реверсивного счетчика на единицу, а выполнение команд возврата из подпрограмм - увеличение содержимого реверсивного счетчика на единицу. Как только количество вложений в подпрограммы (выполнение команд обращения к подпрограммам без соответствующих команд возврата из подпрограмм) достигнет заданного до трассировки значения, состояние старшего информационного выхода реверсивного счетчика 30 окажется равным нулю, что приведет к появлению на третьем входе элемента 13 уров 0

что запрещает наращивание

0

5

0

5

значения счетчика 15 и приводит к запрету трассировки команд данной подпрограммы, до тех пор пока не выполнится команда возврата из подпрограммы.

В режиме четыре на третьем выходе регистра 16 режимов устанавливается уровень 1, что разрешает прохождение сигналов чтения с второго управляющего входа 21 устройства. При этом на выходе 4 устройства появляются результаты трассировки, которые затем могут быть преобразованы в удобный для анализа вид.

Ф.ормула изобретения

Устройство для отладки программ, содержащее первый и второй блоки памяти, первьй, второй и третий триггеры, первьй, второй и третий элементы И, элемент ИЛИ, счетчик адреса, первьй дешифратор и регистр режимов,

причем адресные входы устройства соединены с входами первог о дешифратора и с первой группой информационных входов первого блока памяти, выходы которого являются информационными выходами устройства, первьш и второй выходы первого дешифратора соединены соответственно с входом обращения и с информационным входом второго блока памяти, информационные входы устройства соединены с адресными входами второго блока памяти и второй группой информационных входов первого блока памяти, признаки кода коман ды и начала цикла команды устройства соединены соответственно с информационным входом и входом синхронизации первого триггера, прямой выход которого соединен с входом синхро- низации второго триггера, информационный выход второго блока памяти соединен с информационным входом второго триггера, отличающееся тем, что, с целью повышения производительности отладки программ, в устройство введены второй и третий дешифраторы, четвертьй, пятьш и шестой триггеры и счетчик вложенности, причем информационные входы устрой- ства соединены с входами второго и третьего дешифраторов, выходы которых соединены с информационными входами соответственно третьего и четвертого триггеров, выход первого триггера соединен с тактовьми входами третьего и четвертого триггеров, входы задания режимов устройства соединены с информационными входами регистра режимов, первьй йыход которого соединен с единичным входом второго триггера, прямой выход которого соединен с первьм входом первого элемента И, вход начала цикла команды устройства соеди- нен с тактовым входом пятого триггера и вторым входом первого эле

Q ; 0 5 Q

5

0

меита И, выход ;л орого соединен с первым входом перного элемента И-, второй, третий и четвертьп выходы регистра режимов соединены соответственно с информационным входом тес - того триггера, с первым входом пер-- вого элемента lUlII и с первым входом третьего элемента Н, выходы шестого триггера и первого элемента ШБ1 соединены соответственно с вторыьш и третьими входами второго элемента И, выход которого соединен с входом признака записи первого блока памяти и с первым входом второго элемента ИЛИ, вход признака чтения, устройства соединен с вторым входом третьего, элемента И, выход которого соединен с входом признака чтения первого блока памяти и вторым входом второго элемента ИЛИ, выход второго элемента I-Dni соединен со счетным входом счетчика адреса, информационный выход и выход переполнения которого соединены соответственно с адресным входом первого блока памяти и с тактовым входом шестого триггера, выходы признака кода команды и признака обращения к стеновой памяти устройства соединены соответственно с входом обращения первого блока памяти и с информационным входом пятого триггера, выход которого соединен с вторыми входами четвертого и пятого элементов И, выходы четвертого и пятого элементов И соединены соответственно с входами сложения и вычитания счетчика вложенности, выход старшего разряда которого соединен с вторым входом первого элемента l-LTIi, информационный вход, входы признаков установки кода и записи устройства соединены соответственно с информационным входом счетчика вложенности, с признаком записи счетчика вложенности и с входом записи второго блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1298752A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к вычислительной технике и может быть использовано для автоматизированной отладки программ. Цель изобретения - уменьшение времени на отладку программ. Устройство для отладки программ содержит два блока памяти 1 и 23, первый 22, второй 25 и третий 26 дешифраторы, шесть триггеров 6-9, 12 и 18, два счетчика 15 и 30, пять элементов И 11, 13, 20, 27 и 28, два элемента ИЛИ 14 и 19 и регистр 16 режимов. Изобретение обеспечивает уменьшение объема анализируемой информации благодаря фиксации в трассе программ только тех команд, которые выполняются в подпрограммах не ниже заданного до трассировки уровня вложения. 1 ил.

| Авторское свидетельство СССР 754419, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1985 |

|

SU1298752A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-30—Публикация

1988-01-07—Подача