Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих систем обработки данных.

Целью изобретения является повышение быстродействия и упрощение устройства.

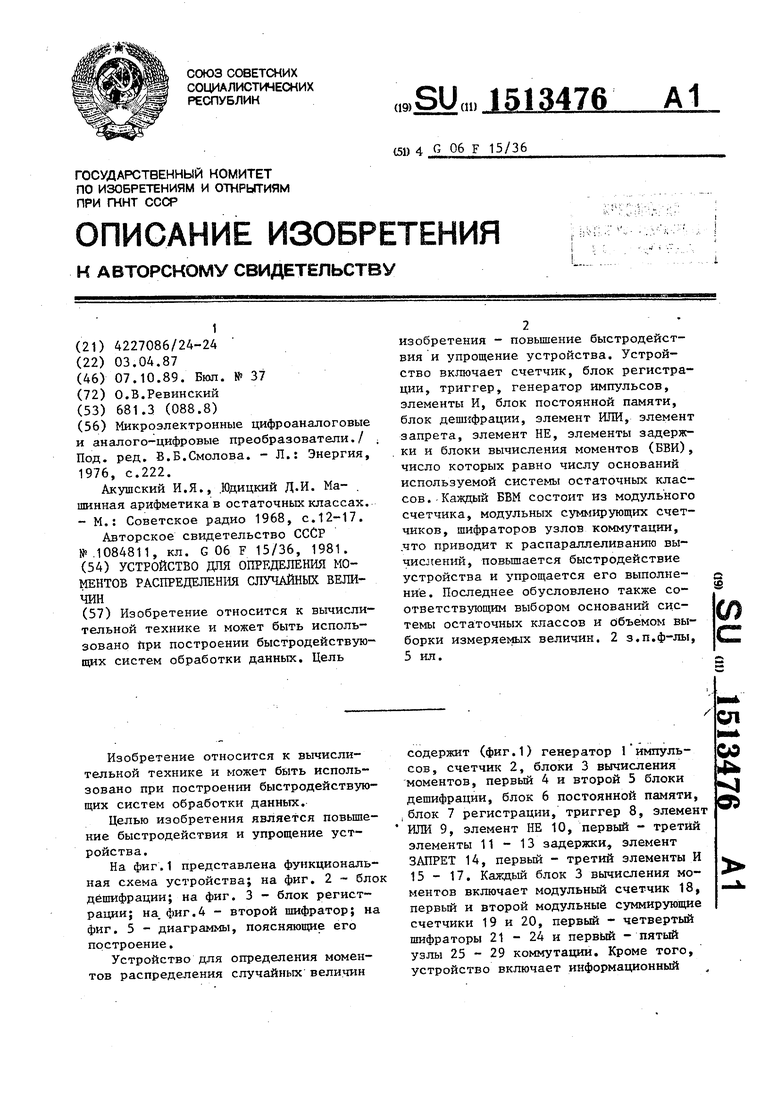

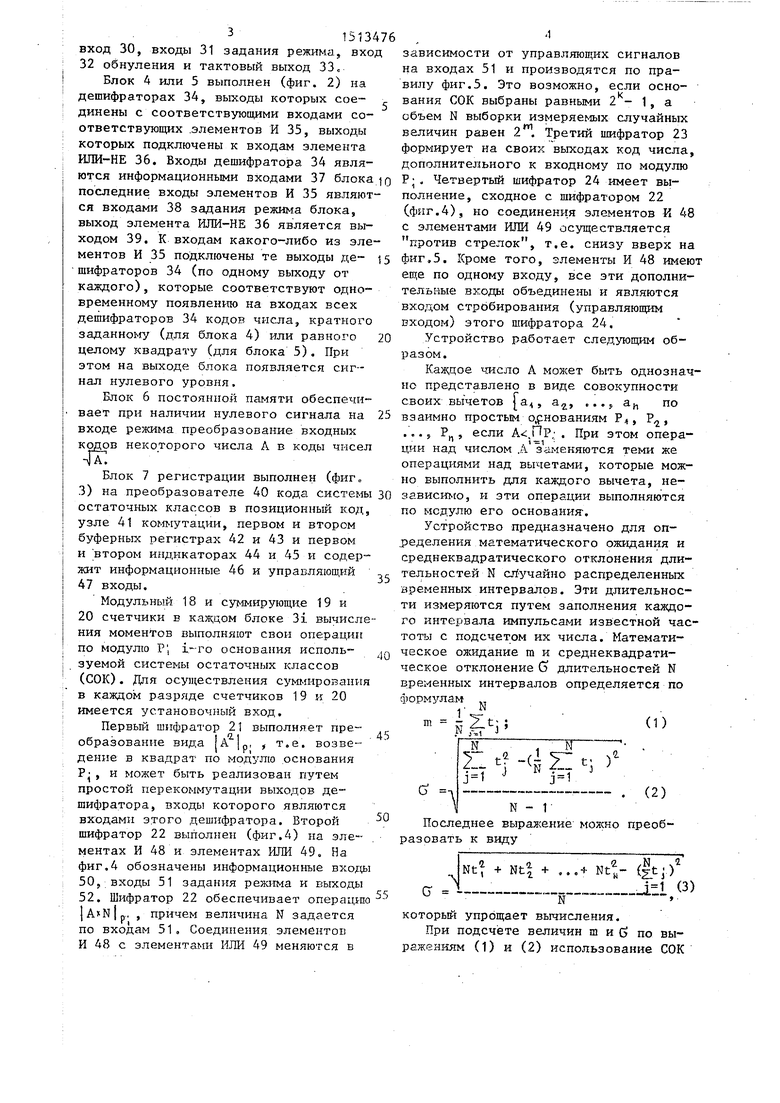

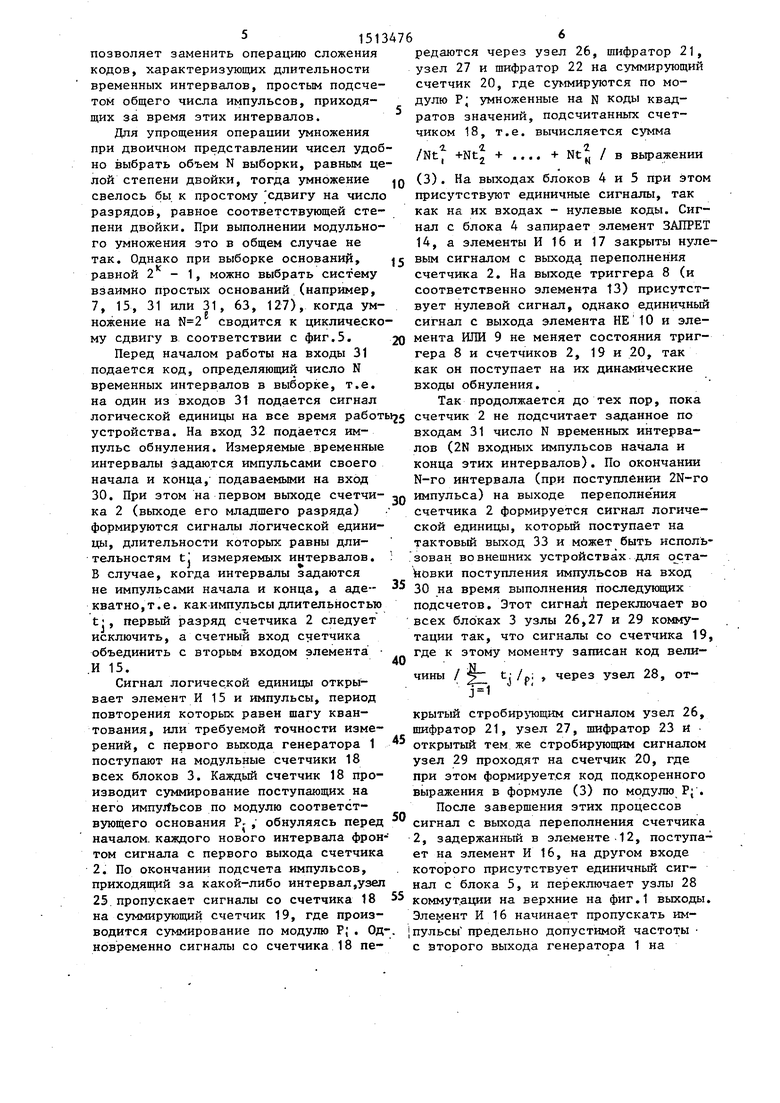

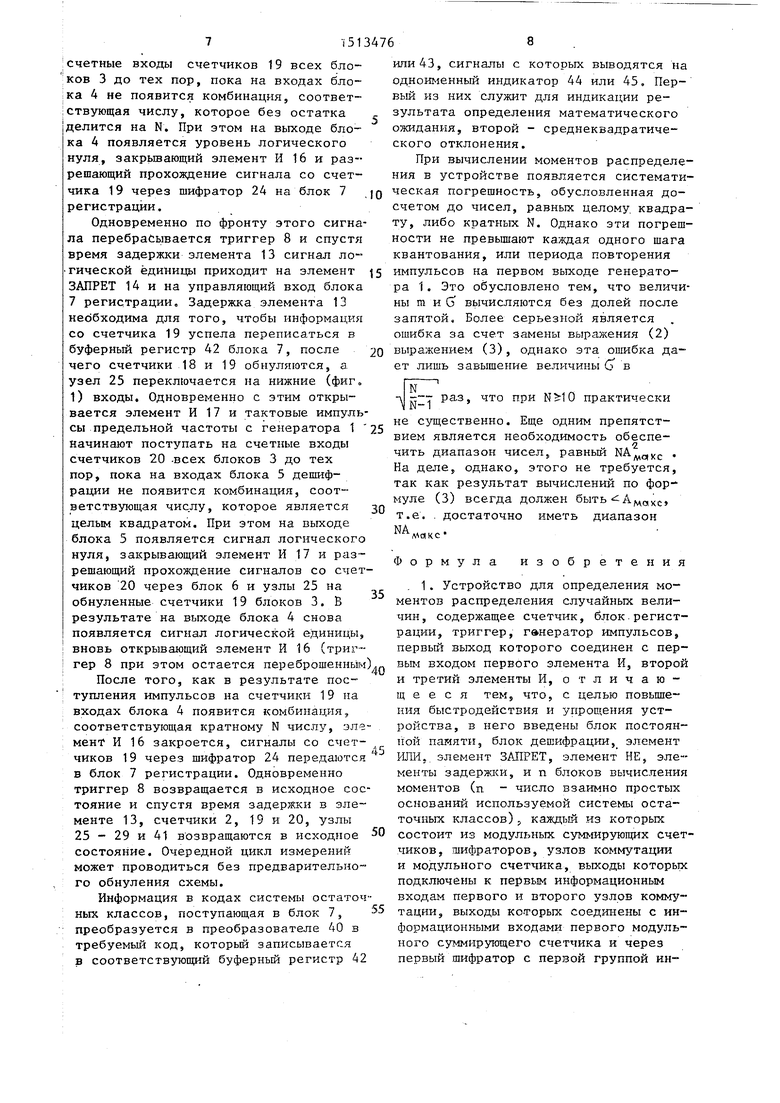

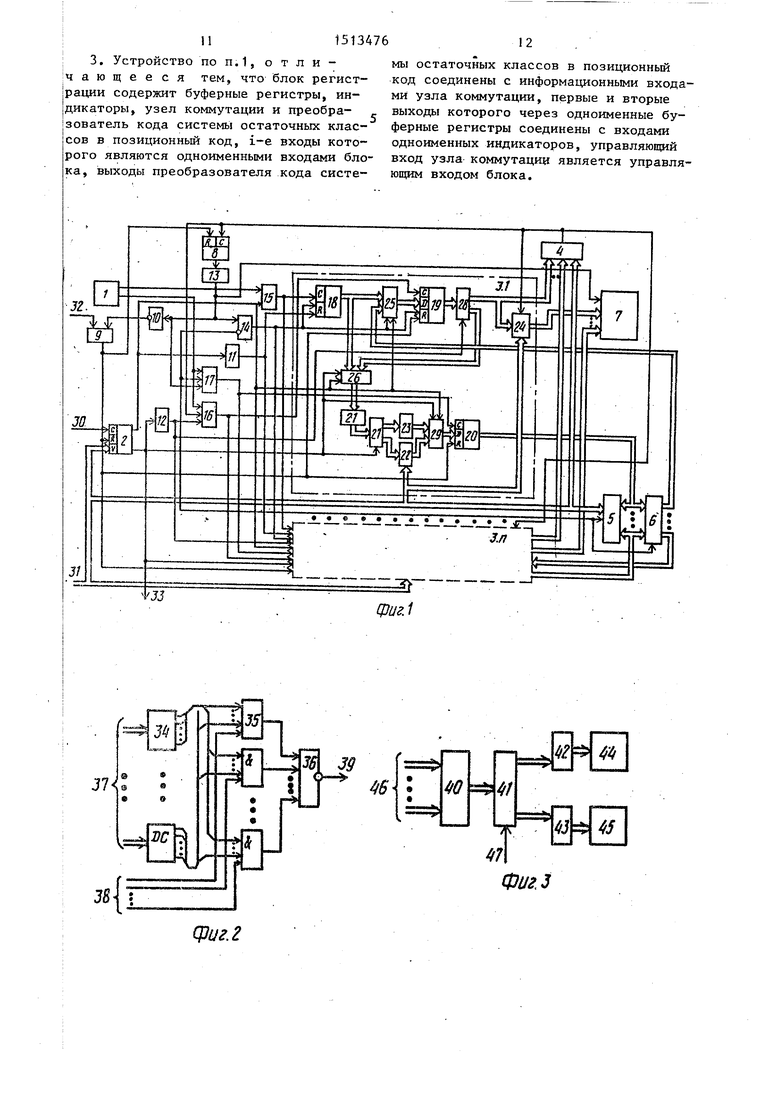

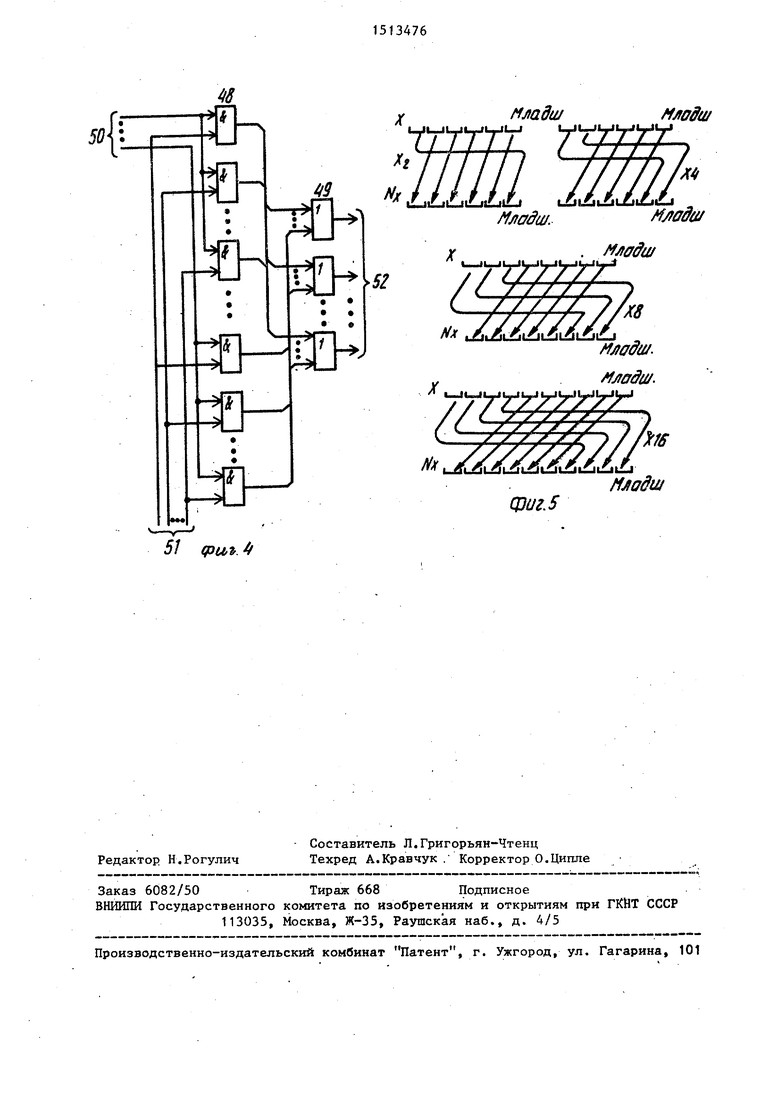

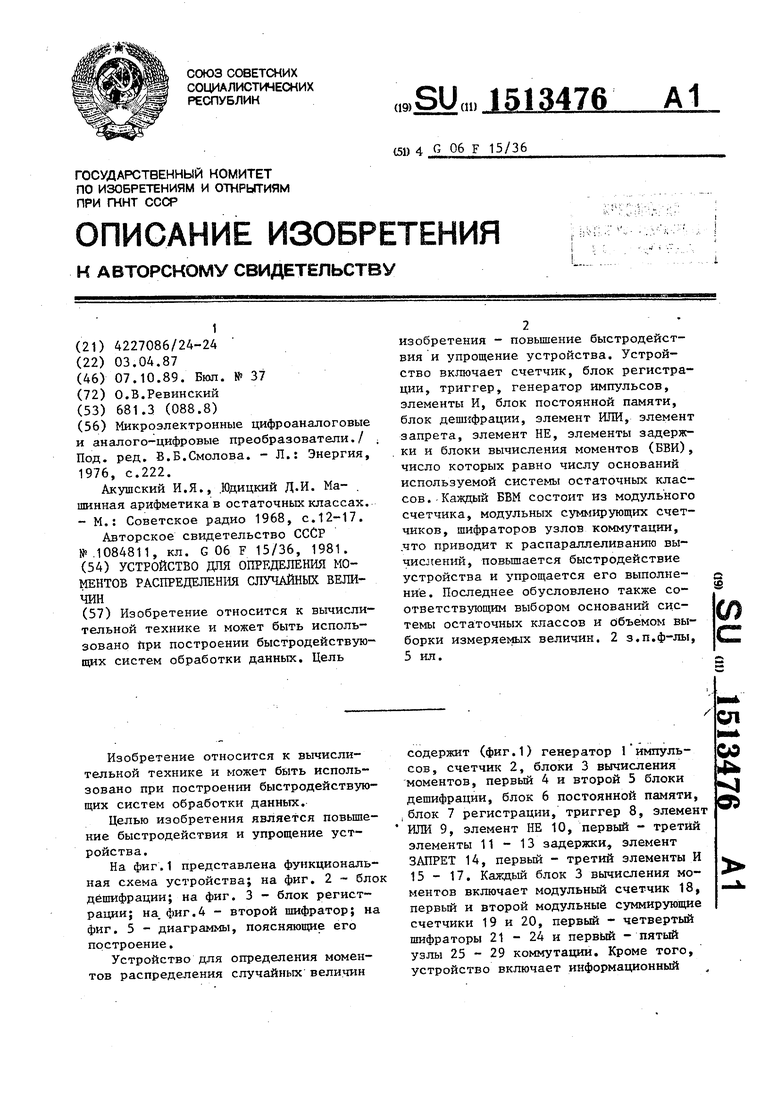

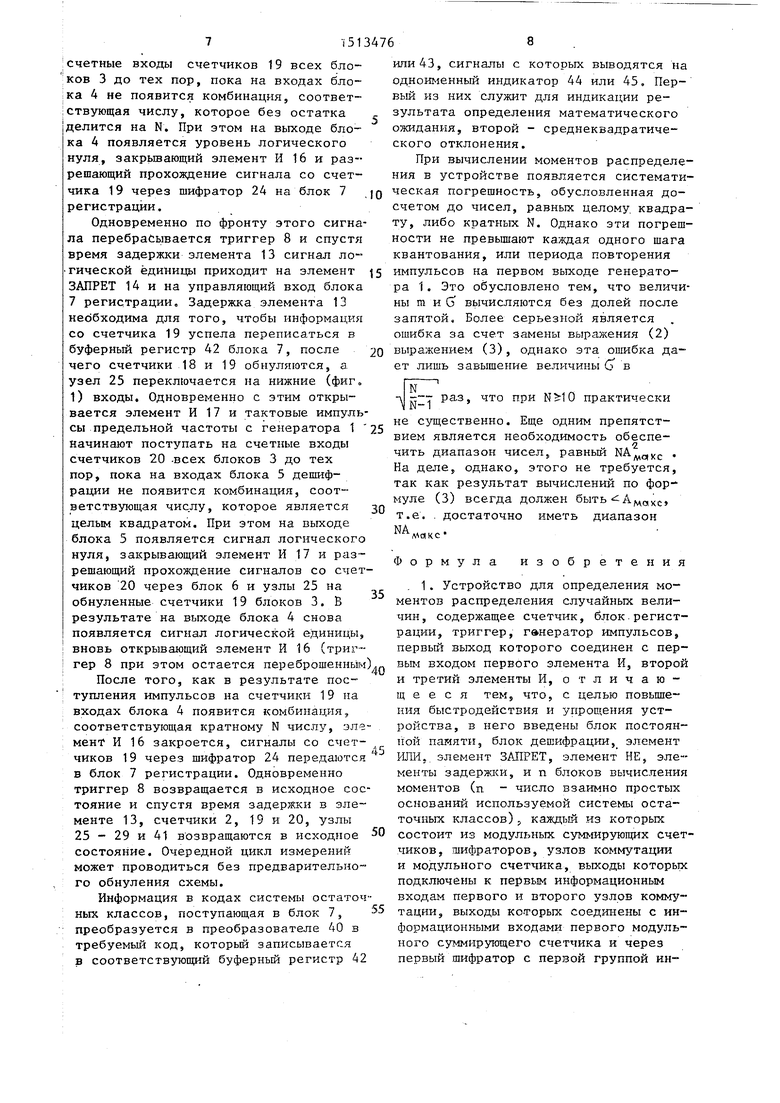

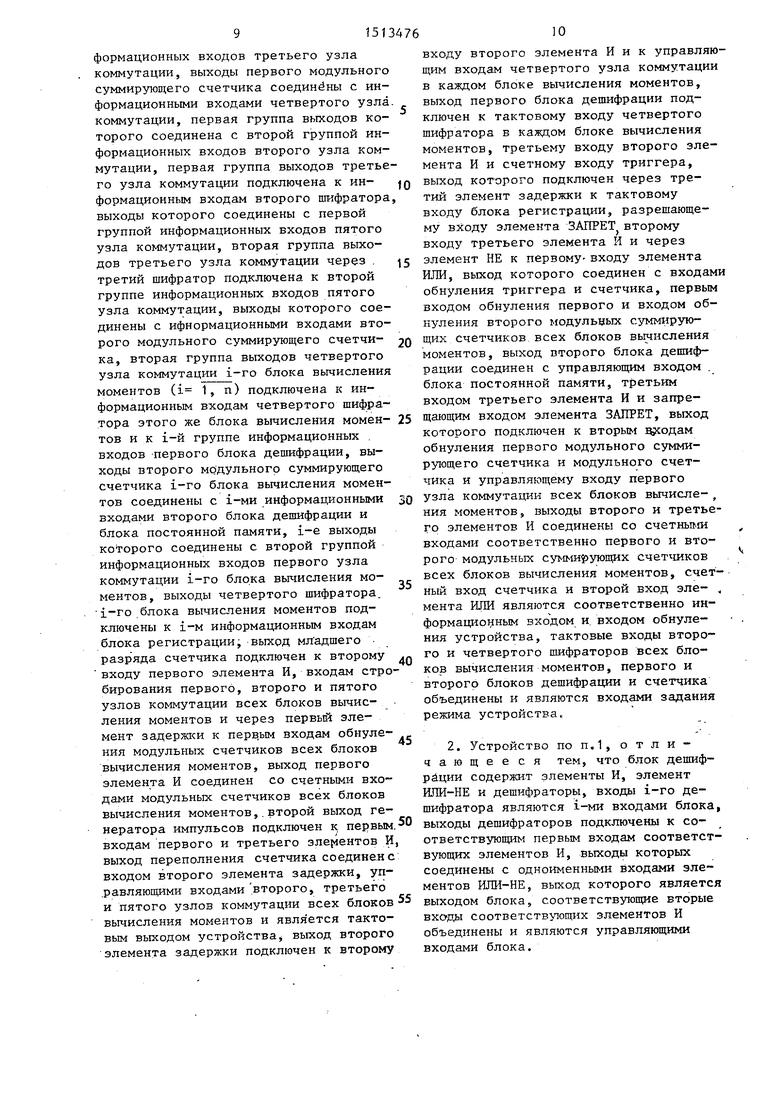

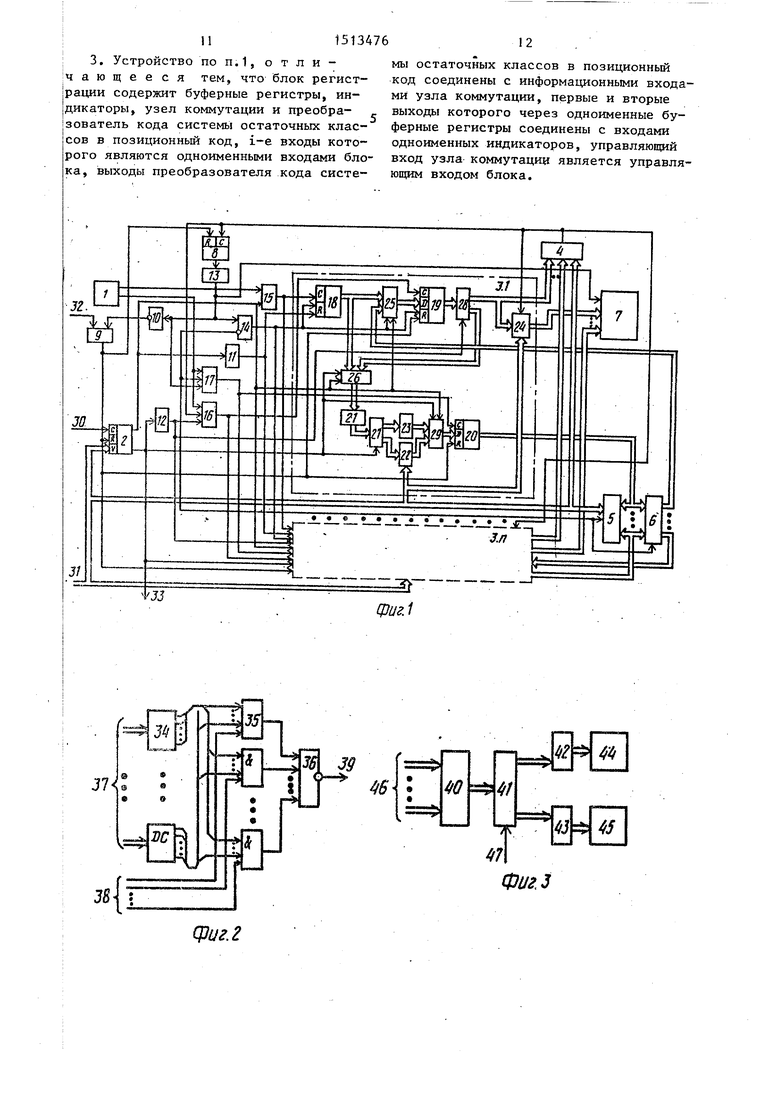

На фиг.1 представлена функциональ нал схема устройства; на фиг. 2 - блок дешифрации; на фиг. 3 - блок регистрации; на фиг.4 - второй шифратор; на фиг. 5 - диаграммы, поясняющие его построение.

Устройство для определения моментов распределения случайных величин

содержит (фиг.1) генератор Г импульсов, счетчик 2, блоки 3 вычисления моментов, первый 4 и второй 5 блоки

дешифрации, блок 6 постоянной памяти, .блок 7 регистрации, триггер 8, элемент ИЛИ 9, элемент НЕ 10, первый - третий элементы 11-13 задержки, элемент ЗАПРЕТ 14, первый - третий элементы И 15 - 17. Каждый блок 3 вычисления моментов включает модульный счетчик 18, первый и второй модульные суммирующие счетчики 19 и 20, первый - четвертый шифраторы 21 - 24 и первый - пятый узлы 25-29 коммутации. Кроме того, устройство включает информационный

СП

00

Од

315134

вход 30, входы 31 задания режима, вхо 32 обнуления и тактовый выход 33,

Блок 4 или 5 выполнен (фиг. 2) на дешифраторах 34, вьпсоды которых сое- динены с соответствующими входами соответствующих .элементов И 35, выходы которых подключены к входам элемента ИЛИ-НЕ 36. Входы дешифратора 34 являются информационными входами 37 блока последние входы элементов И 35 являются входами 38 задания режима блока, выход элемента ИЛИ-НЕ 36 является выходом 39. К входам какого-либо из элементов И 35 подключены те выходы да- шифраторов 34 (по одному выходу от каждого), которые соответствуют одновременному появлен1Ш) на входах всех дешифраторов 34 кодов числа, кратног о заданному (для блока 4) или равного целому квадрату (для блока 5). При этом на выходе блока появляется сигнал нулевого уровня.

Блок 6 постоянной памяти обеспечивает при наличии нулевого сигнала на входе режима преобразование входных кодов некоторого числа А в коды чисел

-ТА.

Блок 7 регистрации выполнен (фиг. 3) на преобразователе 40 кода системы остаточных классов в позиционный код, узле 41 коммутации, первом и втором буферных регистрах 42 и 43 и первом и втором индикаторах 44 и 45 и содержит информационные 46 и управляющий 47 входы.

Модульный 18 и суммирующие 19 и 20 счетчики в каж;а,ом блоке 31 вычисления моментов выполняют свои операции по модулю Р; основания исполь- зуемой системы остаточных классов (СОК). Дня осуществления сум -{ирования в каждом разряде счетчиков 19 и 20 имеется установочный вход.

Первый шифратор 21 выполняет пре- образование вида JA L, , т.е. возведение в квадрат по модулю основания Р , и может быть реализован путем простой перекомм тации выходов дешифратора, входы которого являются

входами этого дешифратора. Второй

50

шифратор 22 выполнен (фиг.4) на элементах И 48 и элементах ИЛИ 49. На фиг.4 обозначены информационные входа: 50, входы 51 задания режима и выходы 52. Шифратор 22 обеспечивает операцшо- - , причем величина N задается по входам 51, Соединения элементов И 48 с элементами ИЛИ 49 меняются в

0

5

О

Q

А

зависимости от управляющих сигналов на входах 51 и производятся по правилу фиг.5. Это возможно, если основания СОК выбраны равными 2 - 1, а объем N выборки измеряемых случайных величин равен 2 Третий шифратор 23 формирует на своих выходах код числа, дополнительного к входному по модулю Р-, Четвертый шифратор 24 имеет выполнение, сходное с шифратором 22 (фиг.4), но соединения элементов К 48 с элементами ИЛИ 49 осуществляется против стрелок, т.е. снизу вверх на фиг,5. Кроме того, элементы И 48 имеют еще по одному входу, все эти дополнительные входы объединены и являются входом стробирования (управляющим входом) этого шифратора 24.

Устройство работает следующим образом.

Каж,цое число А может быть однозначно представлено в виде совокупности

своих вычетов

а.

Ч

по

5

взаимно простым основаниям Р, Р,

.,. 5 -Ри J если А ПР; . При этом опера1ции над числом Л заменяются теми же

операциями над вычетами, которые можно выполнить для каждого вычета, независимо, и эти операции выполняются по модулю его основания-.

Устройство предназначено для определения математического ожидания и среднеквадратического отклонения длительностей N случайно распределенных временных интервалов. Эти длительности измеряются путем заполнения каждого интервала импульсами известной частоты с подсчетом их числа. Математическое ожидание m и среднеквадрати- ческое отклонение G длительностей N вреиенных интервалов определяется по

формулам ., 1

F It-;

. Г--1 J

-р-тг

-Ч .

m

(1)

с

0

N

Г- j 1

t J

J

)

-

-- . (2)

N - Г

Последнее выражение можно преобразовать к виду

А

СГ Л..:„ „ „ . (3)

- .N

который упрощает вычисления.

При подсчёте величин m и С по выражениям (1) и (2) использование СОК

515134766

позволяет заменить операцию сложенияредаются через узел 26, шифратор 21, кодов, характеризующих длительностиузел 27 и шифратор 22 на суммирующий временных интервалов, простым подсче-счетчик 20, где суммируются по мотом общего числа импульсов, приходя-дулю Р; умноженные на N коды квад- щих за время этих интервалов.ратов значений, подсчитанных счет- Для упрощения операции умножениячиком 18, т.е. вычисляется сумма

при двоичном представлении чисел удоб- „i „.2 ,

. - е XT «/Nt. +Nt, ....+ Nt., / в вьфажении

но выбрать объем N выборки, равным це- i z«

лой степени двойки, тогда умножение Q (3). На выходах блоков 4 и 5 при этом свелось бы к простому сдвигу на число присутствуют единичные сигналы, так разрядов, равное соответствующей сте- как на их входах - нулевые коды. Сиг- пени двойки. При выполнении модульно- нал с блока 4 запирает элемент ЗАПРЕТ го умножения это в общем случае не 14, а элементы И 16 и 17 закрыты нуле- так. Однако при выборке оснований, 5 сигналом с выхода, переполнения равной 2 - 1, можно выбрать систему счетчика 2. На выходе триггера 8 (и взаимно простых оснований (например, соответственно элемента 13) присутст- 7, 15, 31 или 31, 63, 127), когда ум- вует нулевой сигнал, однако единичный ножение на сводится к циклическо- сигнал с выхода элемента НЕ 10 и эле- му сдвигу в соответствии с фиг.5. 20 мента ИЛИ 9 не меняет состояния тригПеред началом работы на входы 31 гера 8 и счетчиков 2, 19 и 20, так подается код, определяющий число N как он поступает на их динамические временных интервалов в выборке, т.е. входы обнуления.

на один из входов 31 подается сигнал Так продолжается до тех пор, пока логической единицы на все время работы25 счетчик 2 не подсчитает заданное по устройства. На вход 32 подается им- входам 31 число N временных интерва- пульс обнуления. Измеряемые временные лов (2N входных импульсов начала и интервалы задаются импульсами своего конца этих интервалов). По окончании начала и конца, подаваемыми на вход N-ro интервала (при поступлении 2N-ro 30. При этом на первом выходе счетчи- «Q импульса) на выходе переполне ння ка 2 (выходе его младшего разряда) счетчика 2 формируется сигнал логиче- формируются сигналы логической едини- ской единицы, который поступает на цы, длительности которых равны дли- тактовый выход 33 и может быть исполь- тельностям ti измеряемых интервалов, 1 . зован во внешних устройствах для оста- В случае, когда интервалы задаются овки поступления импульсов на вход не импульсами начала и конца, а аде-- 35 зо на время выполнения последукщих кватно,т.е. как импульсы длительностью подсчетов. Этот сигнаА переключает во tj, первый разряд счетчика 2 следует всех блоках 3 узлы 26,27 и 29 комму- исключить, а счетный вход счетчика тации так, что сигналы со счетчика 19, объединить с вторым входом элемента где к этому моменту записан код вели- И 15N

Сигнал логической единицы откры- . «™ / S р; ° вает элемент И 15 и импульсы, период

повторения которых равен шагу кван- крытый стробир тощим сигналом узел 26, тования, или требуемой точности изме- шифратор 21, узел 27, шифратор 23 и рений, с первого выхода генератора 1 открытый тем же стробирующим сигналом поступают на модульные счетчики 18 узел 29 проходят на счетчик 20, где всех блоков 3. Каждый счетчик 18 про- при этом формируется код подкоренного изводит суммирование поступающих на выражения в формуле (3) по модулю Р;. него импуЯьсов по модулю соответст- После завершения этих процессов вующего основания Р , обнуляясь перед сигнал с выхода переполнения счетчика началом, каждого нового интервала фрон- 2, задержанный в элементе 12, поступа- том сигнала с первого выхода счетчика ет на элемент И 16, на другом входе 2. По окончании подсчета импульсов, . которого присутствует единичный сиг- приходяпщй за какой-либо интервал,узеп нал с блока 5, и переключает узлы 28 25. пропускает сигналы со счетчика 18 55 коммут.ации на верхние на фиг,1 выходы, на суммирующий счетчик 19, где произ- Элемент И 16 начинает пропускать им- водится суммирование по модулю Р; . Од-, |пульсы предельно допустимой частоты новременно сигналы со счетчика 18 пе- с аторого выхода генератора 1 на

счетные входы счетчиков 19 всех блоков 3 до тех пор, пока на входах блока 4 не появится комбинация, соответствующая числу, которое без остатка |делится на N. При этом на выходе блока 4 появляется уровень логического нуля, закрьшающий элемент И 16 и разрешающий прохождение сигнала со счетчика 19 через шифратор 24 на блок 7 регистрации.

Одновременно по фронту этого сигнала перебрасывается триггер 8 и спустя время задержки элемента 13 сигнал логической единицы приходит на элемент ЗАПРЕТ 14 и на управляющий вход блока 7 регистрации. Задержка элемента 13 необходима для того, чтобы информация со счетчика 19 успела переписаться в буферный регистр 42 блока 7, после чего счетчики 18 и 19 обнуляются, а узел 25 переключается на нижние (фиг. 1) входы. Одновременно с этим открывается элемент И 17 и тактовые импульсы предельной частоты с генератора 1 начинают поступать на счетные входы счетчиков 20 -всех блоков 3 до тех пор, пока на входах блока 5 дешифрации не появится комбинация, соответствующая чис.лу, которое является целым квадратом. При этом на выходе блока 5 появляется сигнал логического нуля, закрывающий элемент И 17 и раз-решающий прохождение сигналов со чиков 20 через блок 6 и узлы 25 на обнуленные счетчики 19 блоков 3. В результате на выходе блока 4 снова появляется сигнал логической единицы,

вновь открывающий элемент И 16 (триггер 8 при этом остается переброшенным)

После того, как в результате поступления импульсов на счетчики 19 на входах блока 4 появится комбинация, соответствующая кратному N числу, элемент И 16 закроется, сигналы со счетчиков 19 через шифратор 24 передаются в блок 7 регистрации. Одновременно триггер 8 возвращается в исходное состояние и спустя время задержки в элементе 13, счетчики 2, 19 и 20, узлы 25 - 29 и 41 возвращаются в исходное состояние. Очередной цикл измерений может проводиться без предварительно го обнуления схемы.

Информация в кодах системы остаточных классов, поступающая в блок 7, преобразуется в преобразователе 40 в требуемьш код, которьш записывается в соответствующий буферный регистр 42

или 43, сигналы с которых выводятся на одноименньш индикатор 44 или 45, Первый из них служит для индикации результата определения математического ожидания, второй - среднеквадратиче- ского отклонения.

При вычислении моментов распределения в устройстве появляется систематическая погрешность, обусловленная до- счетом до чисел, равных целому, квадрату, либо кратных N. Однако эти погрешности не превышают каждая одного шага квантования, или периода повторения импульсов на первом выходе генератора 1. Это обусловлено тем, что величины m и (j вь числяются без долей после запятой. Более серьезной является ошибка за счет замены выражения (2) выражением (3), однако эта ошибка дает лишь завышение величины G в

FN

раз, что при НЯО практически

не существенно. Еще одним препятствием является необходимость обеспе2чить диапазон чисел, равный НАд,,,;, .

На деле, однако, этого не требуется, так как результат вычислений по формуле (3) всегда должен быть- , т.е. NA

достаточно макс

иметь диапазон

Формула изобретения

1. Устройство для определения моментов распределения случайных величин, содержащее счетчик, блок.регистрации, триггер, ганератор импульсов, первый выход которого соединен с первым входом первого элемента И, второй и третий элементы И, отличающееся тем, что, с целью повьшхе- ния быстродействия и упрощения устройства, в него введены блок постоянной паияти, блок дешифрации, элемент

ИЛИ,, элемент ЗАПРЕТ, элемент НЕ, элементы задержки, и п блоков вычисления моментов (п - число взаимно простых оснований используемой системы остаточных классов)J каждьй из которых состоит из модульных суммирующих счетчиков, шифраторов, узлов коммутации и модульного счетчика, выходы которьтх подключены к первым информационным входам первого и второго узлов коммутации, выходы которых coeдшieны с информационными входами первого модульного суммирующего счетчика и через первый шифратор с пер}зой группой ин9151

формационных входов третьего узла коммутации, выходы первого модульного суммирующего счетчика соединены с информационными входами четвертого узла коммутации, первая группа выходов которого соединена с второй группой информационных входов второго узла коммутации, первая группа выходов третьего узла коммутации подключена к ий- формационным входам второго шифратора выходы которого соединены с первой группой информационных входов пятого узла коммутации, вторая группа выходов третьего узла коммутации через . третий шифратор подключена к второй группе информационных входов пятого узла коммутации, выходы которого соединены с ифнормационными входами второго модульного суммирующего счетчи- ка, вторая группа выходов четвертого узла коммутации i-го блока вычисления (i

моментов (.1 1, п) подключена к информационным входам четвертого шифратора этого же блока вычисления момен- тов и к i-й группе информационных входов первого блока дешифрации, выходы второго модульного суммирующего счетчика i-ro блока вычисления моментов соединены с i-ми информационными входами второго блока дешифрации и блока постоянной памяти, i-e выходы которого соединены с второй группой информационных входов первого узла коммутации i-ro блока вычисления мо

ментов, выходы четвертого шифратора. i-го блока вычисления моментов подключены к L-M информационным входам блока регистрации; выход мл адшего разряда счетчика подключен к второму входу первого элемента И, входам стро- бирования первого, второго и пятого узлов коммутации всех блоков вычисления моментов и через первьй элемент задержки к первым входам обнуле ния модульных счетчиков всех блоков вычисления моментов, выход первого элемента И соединен со счетными вхоами модульных счетчиков всех блоков вычисления моментов,.второй выход генератора импульсов подключен к первым. входам первого и третьего элер1ентов И, выход переполнения счетчика соединен с входом второго элемента задержки, управляющими входами .второго, третьего

50

2. Устройство по п.1, отличающееся тем, что блок дешнф- рйции содержит элементы И, элемент Ш1И-НЕ и дешифраторы, входь i-ro дешифратора являются i-MH входами блока, выходы дешифраторов подключены к соответствующим первым входам соответствующих элементов И, выходы которых соединены с одноименными входами элементов ИЛИ-НЕ, выход которого является

и пятого узлов коммутации всех блоков 55 выходом блока, соответствующее вторые

10

Q15 20

5 О

5

0

5

0

входу второго элемента И и к управляющим входам четвертого узла коммутации в каждом блоке вычисления моментов, выход первого блока дешифрации подключен к тактовому входу четвертого шифратора в каждом блоке вычисления моментов, третьему входу второго элемента И и счетному входу триггера, выход которого подключен через третий элемент задержки к тактовому входу блока регистрации, разрешающему ВХ.ОДУ элемента ЗАПРЕТ второму входу третьего элемента И и через элемент НЕ к первому- входу элемента ИЛИ, выход которого соединен с входами обнуления триггера и счетчика, первым входом обнуления первого и входом обнуления второго модульных суммирующих счетчиков всех блоков вычисления моментов, выход второго блока дешифрации соединен с управляющим входом блока постоянной памяти, третьим входом третьего элемента И и запрещающим входом элемента ЗАПРЕТ, выход которого подключен к вторым ц}содам обнуления первого модульного суммирующего счетчика и модульного счетчика и управляющему входу первого узла коммутации всех блоков вычисле- , ния моментов, выходы второго и третьего элементов И соединены со счетными входами соответственно первого и второго модульных сумми ующих Счетчиков всех блоков вычисления моментов, счетный вход счетчика и второй вход эле- , мента ИЛИ являются соответственно информационным входом и. входом обнуления устройства, тактовые входы второго и четвертого шифраторов всех блоков вычисления моментов, первого и второго блоков дешифрации и счетчика объединены и являются входами задания режима устройства.

2. Устройство по п.1, отличающееся тем, что блок дешнф- рйции содержит элементы И, элемент Ш1И-НЕ и дешифраторы, входь i-ro дешифратора являются i-MH входами блока, выходы дешифраторов подключены к соответствующим первым входам соответствующих элементов И, выходы которых соединены с одноименными входами элементов ИЛИ-НЕ, выход которого является

5 выходом блока, соответствующее вторые

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1985 |

|

SU1304014A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для моделирования узлов коммутации сообщений | 1985 |

|

SU1278879A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих систем обработки данных. Цель изобретения - повышение быстродействия и упрощение устройства. Устройство включает счетчик, блок регистрации, триггер, генератор импульсов, элементы И, блок постоянной памяти, блок дешифрации, элемент ИЛИ, элемент запрета, элемент НЕ, элементы задержки и блоки вычисления моментов (БВМ), число которых равно числу оснований используемой системы остаточных классов. Каждый БВМ состоит из модульного счетчика, модульных суммирующих счетчиков, шифраторов, узлов коммутации, что приводит к распараллеливанию вычислений, повышается быстродействие устройства и упрощается его выполнение. Последнее обусловлено также соответствующим выбором оснований системы остаточных классов и объемом выборки измеряемых величин. 5 ил.

вычисления моментов и является тактовым выходом устройстваj выход второго элемента задержки подключен к второму

вхо ды соответствующих элементов И объединены и являются управляющими входами блока.

и

мы остаточных классов в позиционный код соединены с информационными входами узла коммутации, первые и вторые выходы которого через одноименные буферные регистры соединены с входами одноименных индикаторов, управляющий вход узла коммутации является управляющим входом блока.

37

зв

фиг. г

фиг.1

Ii2

/

J

ж

4S

Фиг

50

51 (.

rrrr

младшМлодш

( / / /

/ч/., r.l /../..

il iiLjlLJt -j:LjiLJ L JtZjuu

Лладш.M/fOffu/

X. Jfffffa/

ЙГХТГ

4

/ / / / / ; //// /A

ГЛ r /II /II ГыГ I

Л . . Xi /II /II /It 11 I

млодш.

лодш.

fj,/77/77/,

1 Л I л rtt rit ir rttrtt i,f tir t

Нлодш фиг.5

| Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи./ ; Под | |||

| ред | |||

| В.Б.Смолова | |||

| - Л.: Энергия, 1976, с.222 | |||

| Акушский И.Я., .Юдицкий Д.И | |||

| Ма- | |||

| шинная арифметика в остаточных классах | |||

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| Устройство для определения параметров распределения случайных величин | 1981 |

|

SU1084811A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-04-03—Подача