Pui /

Изобретение относится к вычислительной технике и предназначено для работы в мультипроцессорной системе обработки данных, использующей общую информационную шину для доступа к общим ресурсам, в частности к общей памяти группы процесоров или системы в целом

Целью изобретения является повышение производительности многопроцессорной системы за счет уменьшения времени работы с общей шиной процессора и интенсивности обращения к ней

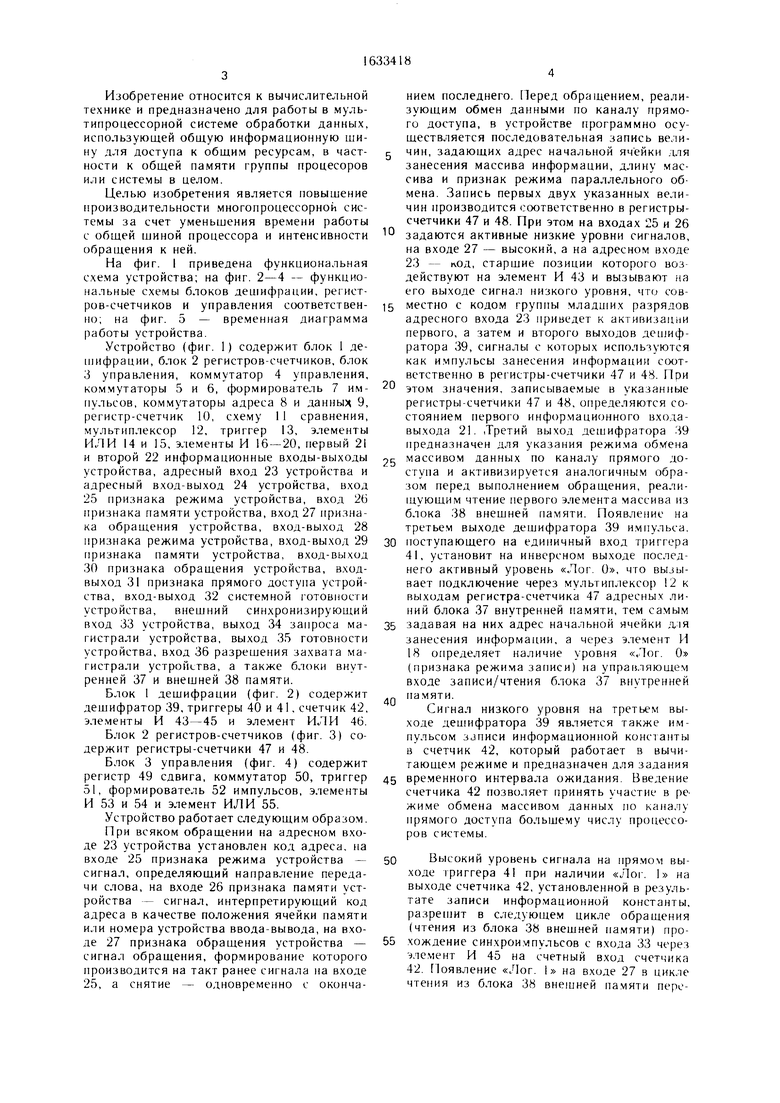

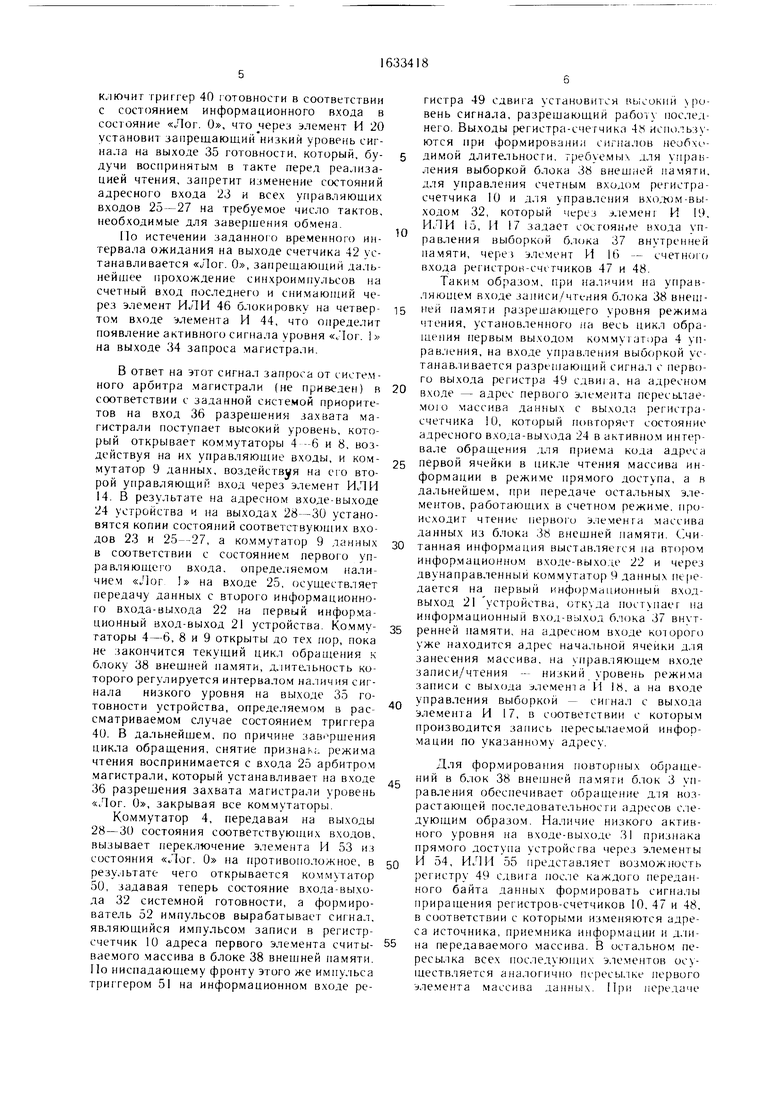

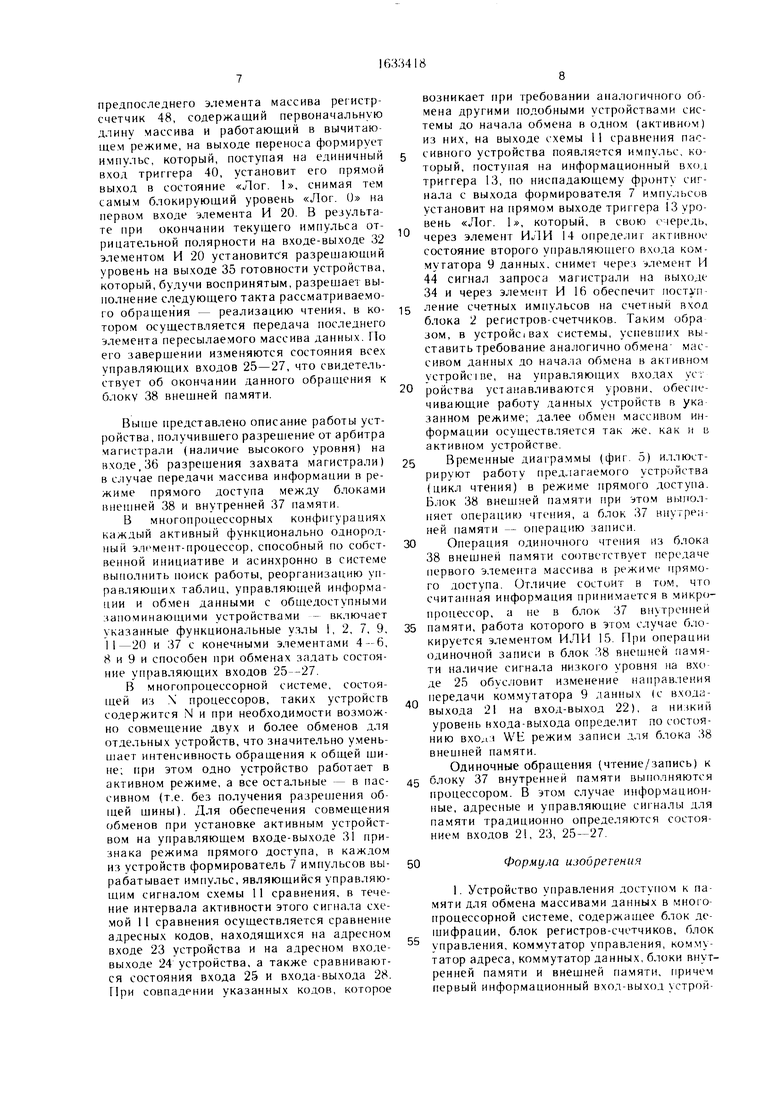

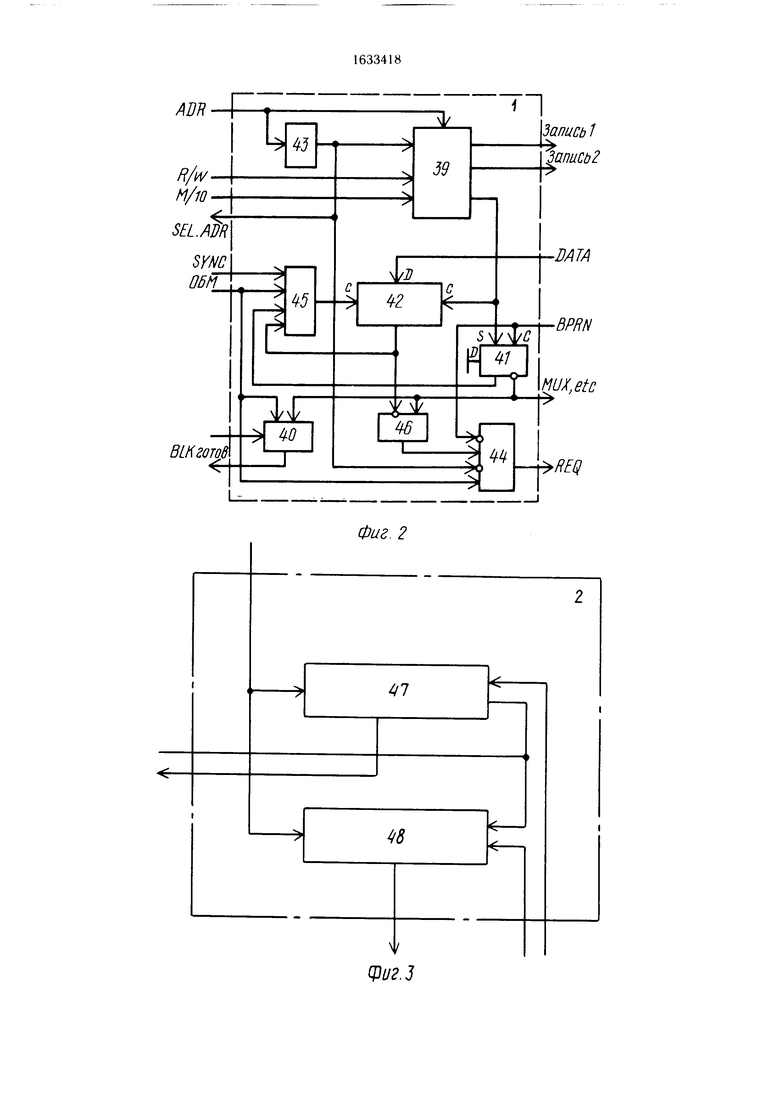

На фиг I приведена функциональная схема устройства, на фиг 2-4 - функцио нальные схемы блоков дешифрации, регистров-счетчиков и управления соответственно, на фиг 5 - временная диаграмма работы устройства

Устройство (фиг 1) содержит блок 1 дешифрации, блок 2 регистров счетчиков, блок 3 управления, коммутатор 4 управления, коммутаторы 5 и 6, формирователь 7 импульсов, коммутаторы адреса 8 и данных 9, регистр-счетчик 10, схему 11 сравнения, мультиплексор 12, триггер 13, элементы ИЛИ 14 и 15, элементы И 16 - 20, первый 21 и второй 22 информационные входы-выходы устройства, адресный вход 23 устройства и адресный вход выход 24 устройства, вход 25 признака режима устройства, вход 2Ь признака памяти устройства, вход 27 призна ка обращения устройства, вход-выход 28 признака режима устройства, вход-выход 29 признака памяти устройства, вход-выход 30 признака обращения устройства, вход- выход 31 признака прямого доступа устройства, вход-выход 32 системной IOTOBHOCTH устройства, внешний синхронизирующий вход 33 устройства, выход 34 запроса магистрали устройства, выход 35 готовности устройства, вход 36 разрешения захвата ма гистрали устройства, а также блоки внутренней 37 и внешней 38 памяти

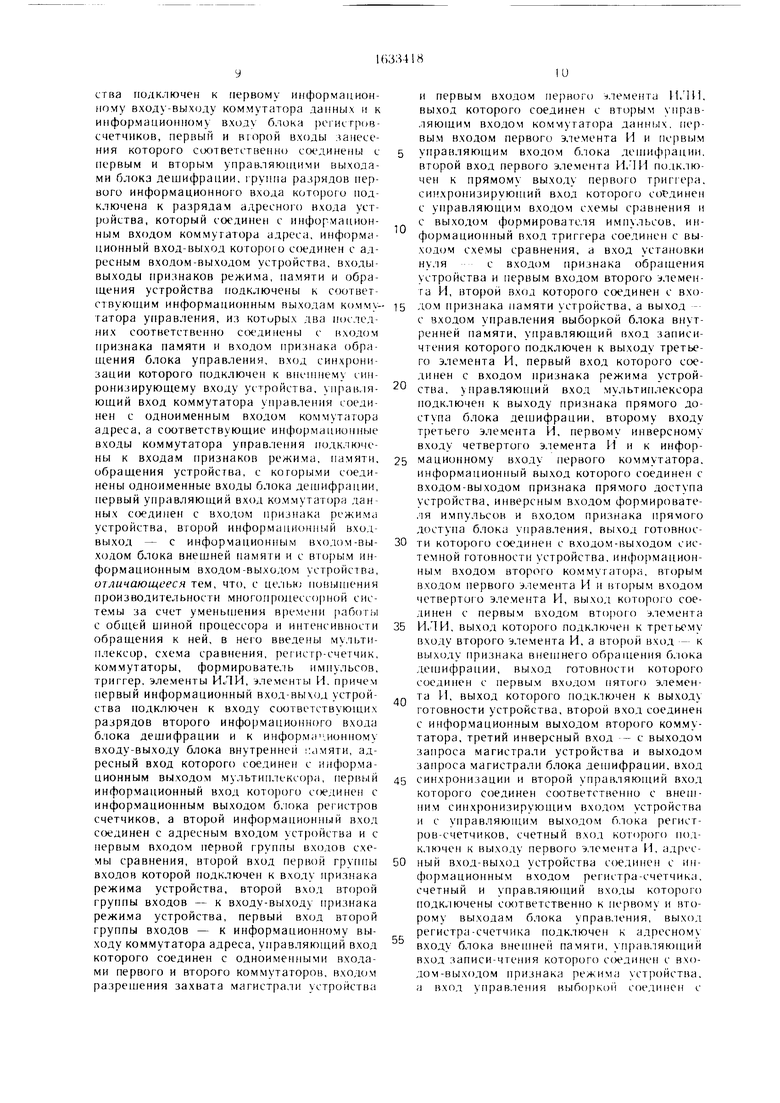

Блок 1 дешифрации (фиг 2) содержит дешифратор 39, триггеры 40 и 41, счетчик 42, элементы И 43-45 и элемент ИЛИ 4Ь

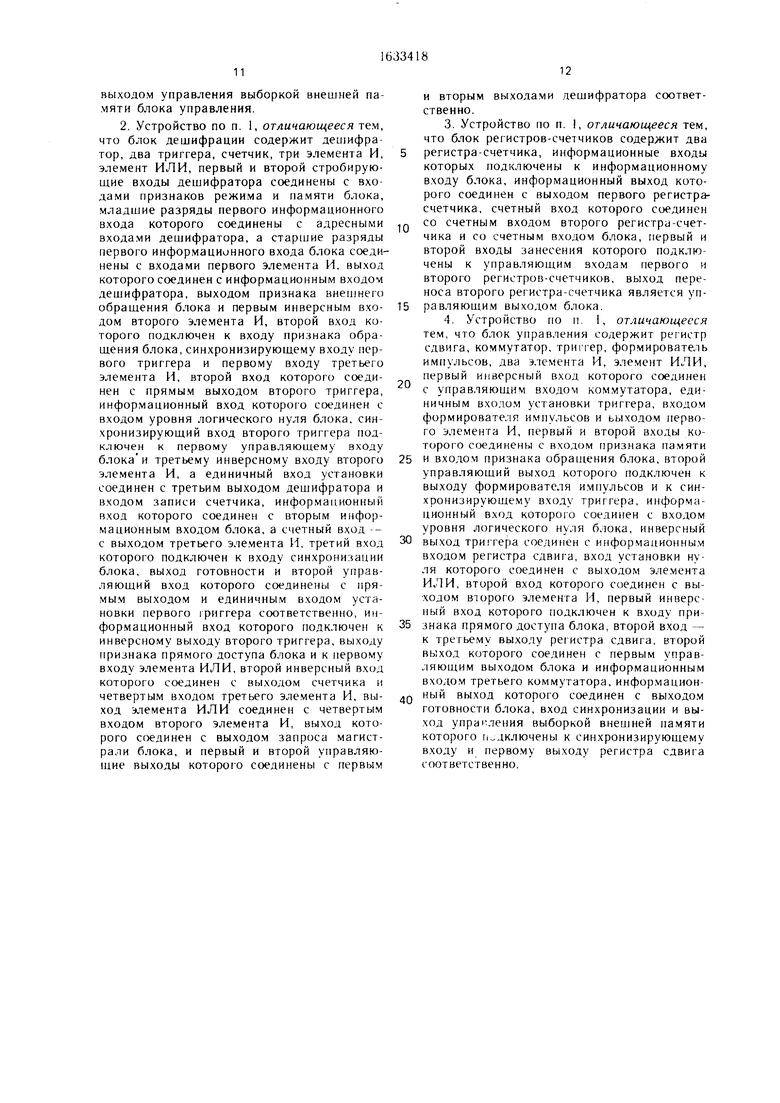

Блок 2 регистров-счетчиков (фиг 3) со держит регистры-счетчики 47 и 48

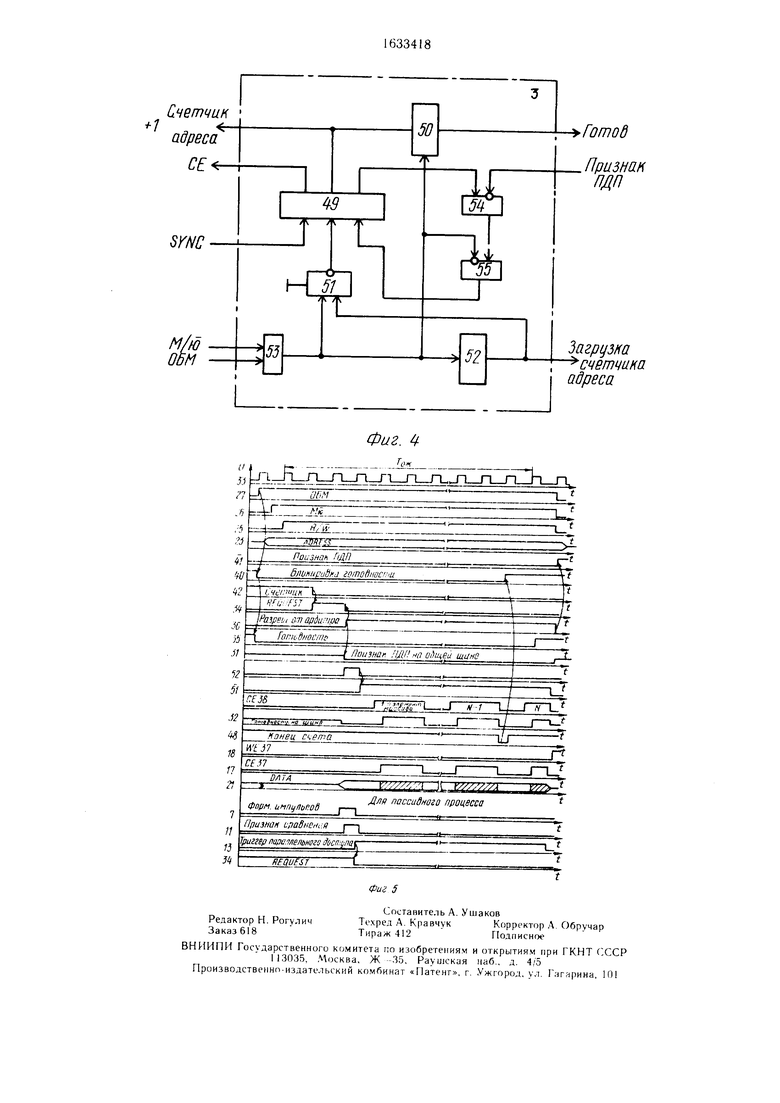

Блок 3 управления (фиг 4) содержит регистр 49 сдвига, коммутатор 50, триггер 51, формирователь 52 импульсов, элементы И 53 и 54 и элемент ИЛИ 55

Устройство работает следующим обра юм

При всяком обращении на адресном входе 23 устройства установлен код адреса, на входе 25 признака режима устройства - сигнал, определяющий направление передачи слова, на входе 26 признака памяти устройства - сигнал, интерпретирующий код адреса в качестве положения ячейки памяти или номера устройства ввода-вывода, на входе 27 признака обращения устройства - сигнал обращения, формирование которого производится на такт ранее сигнала на входе 25, а снятие - одновременно с окончанием последнего Перед обращением, реализующим обмен данными по каналу прямого доступа, в устройстве программно осуществляется последовательная запись величин, задающих адрес начальной ячейки щя занесения массива информации, длину массива и признак режима параллельного об мена Запись первых двух указанных величин производится соответственно в регистры- счетчики 47 и 48 При этом на входах 25 и 26 задаются активные низкие уровни сигналов, на входе 27 - высокий, а на адресном входе 23 - од, старшие позиции которого воз действуют на элемент И 43 и вызывают на его выходе сигнал низкого уровня, что сов

местно с кодом группы младших разрядов адресного входа 23 приведет к активи}ацпи первого, а затем и второго выходов дешиф ратора 39, сигналы с которых используются как импульсы занесения информации соответственно в pei истры-счетчики 47 и 48 При

0

этом значения, записываемые в указанные

регистры счетчики 47 и 48, определяются со стоянием первого информационного вхота выхода 21 .Третий выход дешифратора 19 предназначен для указания режима обмена

5 массивом данных по каналу прямого доступа и активизируется аналогичным образом перед выполнением обращения, реали- щующим чтение первого элемента массива из блока 38 внешней памяти Появление на третьем выходе дешифратора 39 импульса

0 поступающего на единичный вход триггера 41, установит на инверсном выходе послед него активный уровень «Ло 0, что вызывает подключение через мультиплексор 12 к выходам регистра-счетчика 47 адресных линии блока 37 внутренней памяти, тем самым

5 задавая на них адрес начальной ячейки для занесения информации, а через элемент И 18 определяет наличие уровня «Лог О (признака режима записи) на упрарпяющеч входе записи/чтения блока 37 внутренней памяти

Сигнал низкого уровня на третьем выходе дешифратора 39 является также им пульсом записи информационной константы в счетчик 42, который работает в вычитающем режиме и предназначен для задания

5 временного интервала ожидания Введение счетчика 42 позволяет принять участие в ре жиме обмена массивом данных по каналу прямого доступа большему числу процессоров системы

0Высокий уровень сигнала на прямом вы

ходе фиггера 41 при наличии «Ло| 1 на выходе счетчика 42, установленной в репгль- тате записи информационной константы, разрешит в следующем цикле обращения (чтения из блока 38 внешней памяти) про

5 хождение синхроимпульсов с входа 33 через эаемент И 45 на счетный вход счетчика 42 Появление «Лог 1 на входе 27 в цикле чтения из блока 38 внешней памяти перс

ключиг триггер 40 готовности в соответствии с состоянием информационного входа в состояние «Лог. О, что через элемент И 20 установит запрещающий низкий уровень сигнала на выходе 35 готовности, который, бу- дучи воспринятым в такте перед реализацией чтения, запретит изменение состояний адресного входа 23 и всех управляющих входов 25-27 на требуемое число тактов, необходимые для завершения обмена

По истечении заданною временного интервала ожидания на выходе счетчика 42 устанавливается «Лог. О, запрещающий дальнейшее прохождение синхроимпульсов на счетный вход последнего и снимающий через элемент ИЛИ 46 блокировку на четвер- том входе элемента И 44, что определит появление активного сигнала уровня «Лог. I на выходе 34 запроса магистрали.

В ответ на этот сигнал запроса от системного арбитра магистрали (не приведен) в соответствии с заданной системой приоритетов на вход 36 разрешения захвата магистрали поступает высокий уровень, который открывает коммутаторы 4 -6 и 8, воздействуя на их управляющие входы, и ком- мутатор 9 данных, воздействуя на ею второй управляющий вход через элемент ИЛИ 14. В результате на адресном входе-выходе 24 устройства и на выходах 28-30 установятся копии состояний соответствующих входов 23 и 25-27, а коммутатор 9 данных в соответствии с состоянием первою управляющего входа, определяемом наличием «Лог 1 на входе 25, осуществляет передачу данных с второго информационного входа-выхода 22 на первый информационный вход-выход 21 устройства Комму- гаторы 4-6, 8 и 9 открыты до тех пор, пока не закончится текущий цикл обращения к блоку 38 внешней памяти, длительность которого регулируется интервалом наличия сигнала низкого уровня на выходе 35 го-

товности устройства, определяемом в рас-

сматриваемом случае состоянием триггера 40. В дальнейшем, по причине завершения цикла обращения, снятие признак;, режима чтения воспринимается с входа 25 арбитром магистрали,который устанавливает на входе 36 разрешения захвата магистрали уровень «Лог. О, закрывая все коммутаторы

Коммутатор 4, передавая на выходы 28 - 30 состояния соответствующих входов, вызывает переключение элемента И 53 из состояния «Лог. О на противоположное, в результате чего открывается коммутатор 50, задавая теперь состояние входа-выхода 32 системной готовности, а формирователь 52 импульсов вырабатывает сигнал, являющийся импульсом записи в регистр- счетчик 10 адреса первого элемента считы- ваемого массива в блоке 38 внешней памяти. По ниспадающему фронту этого же импульса триггером 51 на информационном входе ре

0

гистра 49 сдвига установится высокий уровень сигнала, разрешающий работ последнего. Выходы регистра-счетчика 48 используются при формировании сигналов необходимой длительности, требуемых для управления выборкой блока 38 внешней памяти, для управления счетным входом регистра - счетчика 10 и для управления в.хо,юм-выходом 32, который через племен И 19, ИЛИ 15, И 17 задает состояние входа управления выборкой блока 37 внутренней памяти, через элемент И 16 - счетной; входа регистрон-сч(. тчиков 47 и 48.

Таким образом, при наличии на управляющем входе записи/чтения блока 38 внешней памяти разрешающего уровня режима чтения, установленного на весь цикл обращения первым выходом коммутатора 4 управления, на входе управления выборкой устанавливается разрешающий сигнал с первого выхода регистра 49 сдвша, на адресном входе - адрес первого элемента пересылаемою массива данных с выхода регисгра- счегчика 10, который повторяет состояние адресного входа-выхода 24 в активном интервале обращения для приема кода адреса первой ячейки в цикле чтения массива информации в режиме прямого доступа, а в дальнейшем, при передаче остальных элементов, работающих в счетном режиме, происходит чтение первого элемента массива данных из блока 38 внешней памяти. Считанная информация выставлялся на втором информационном в ходе-вы АО и 22 и через двунаправленный коммутатор 9 данных передается на первый информационный вход- выход 21 устройства, откуда поступает на информационный вход-выход блока 37 внутренней памяти, на адресном входе которого уже находится адрес начальной ячейки для занесения массива, на управляющем входе записи/чтения -- низкий уровень режима записи с выхода элемента И 18. а на входе управления выборкой - CHI нал с выхода элемента И 17, в соответствии с которым производится запись пересылаемой информации по указанному адресу.

Для формирования повторных обращений в блок 38 внешней памяти блок 3 управления обеспечивает обращение для возрастающей последовательности адресов следующим образом. Наличие низкого активного уровня на входе-выходе 31 признака прямого доступа устройства через элементы И 54, ИЛИ 55 представляет возможность регистру 49 сдвига после каждою переданного байта данных формировать сигналы приращения регистров-счетчиков 10.47 и 48. в соответствии с которыми изменяются адреса источника, приемника информации и длина передаваемого массива. В остальном пересылка всех последующих элементов осуществляется аналогично пересылке первого элемента массива данных При передаче

предпоследнего элемента массива регистр- счетчик 48, содержащий первоначальную длину массива и работающий в вычитающем режиме, на выходе переноса формирует импульс, который, поступая на единичный вход триггера 40, установит его прямой выход в состояние «Лог. 1, снимая тем самым блокирующий уровень «Лог. О на первом входе элемента И 20. В результате при окончании текущего импульса отрицательной полярности на входе-выходе 32 элементом И 20 установится разрешающий уровень на выходе 35 готовности устройства, который, будучи воспринятым, разрешает выполнение следующего такта рассматриваемого обращения - реализацию чтения, в котором осуществляется передача последнего элемента пересылаемого массива данных. По его завершении изменяются состояния всех управляющих входов 25-27, что свидетельствует об окончании данного обращения к блоку 38 внешней памяти.

Выше представлено описание работы устройства, получившего разрешение от арбитра магистрали (наличие высокого уровня) на входе.36 разрешения захвата магистрали) в случае передачи массива информации в режиме прямого доступа между блоками внешней 38 и внутренней 37 памяти.

В многопроцессорных конфигурациях каждый активный функционально однородный элемент-процессор, способный по собственной инициативе и асинхронно в системе выполнить поиск работы, реорганизацию управляющих таблиц, управляющей информации и обмен данными с общедоступными запоминающими устройствами - включает указанные функциональные узлы 1, 2, 7, 9, 11-20 и 37 с конечными элементами 4-6, 8 и 9 и способен при обменах задать состояние управляющих входов 25-27.

В многопроцессорной системе, состоящей из процессоров, таких устройств содержится N и при необходимости возможно совмещение двух и более обменов для отдельных устройств, что значительно уменьшает интенсивность обращения к общей шине; при этом одно устройство работает в активном режиме, а все остальные - в пассивном (т.е. без получения разрешения общей шины). Для обеспечения совмещения обменов при установке активным устройством на управляющем входе-выходе 31 признака режима прямого доступа, в каждом из устройств формирователь 7 импульсов вырабатывает импульс, являющийся управляющим сигналом схемы 11 сравнения, в течение интервала активности этого сигнала схемой 1 1 сравнения осуществляется сравнение адресных кодов, находящихся на адресном входе 23 устройства и на адресном входе- выходе 24 устройства, а также сравниваются состояния входа 25 и входа-выхода 28. При совпадении указанных кодов, которое

возникает при требовании аналогичного обмена другими подобными устройствами системы до начала обмена в одном (активном) из них, на выходе схемы 11 сравнения пассивного устройства появляется импульс, который, поступая на информационный BXOI триггера 13, по ниспадающему фронту сигнала с выхода формирователя 7 импульсов установит на прямом выходе триггера 13 уровень «Лог. 1, который, в свою очередь,

через элемент ИЛИ 14 определит активное состояние второго управляющего входа коммутатора 9 данных, снимет через элемент И 44 сигнал запроса магистрали на выходе 34 и через элемент И 16 обеспечит поступ

ление счетных импульсов на счетный вход блока 2 регистров-счетчиков. Таким обра зом, в устройовах системы, успевших выставить требование аналогично обмена- массивом данных до начала обмена в активном устройс ве, на управляющих входах ус;

0 ройства устанавливаются уровни, обеспечивающие работу данных устройств в ука занном режиме; далее обмен массивом информации осуществляется так же. как и в активном устройстве.

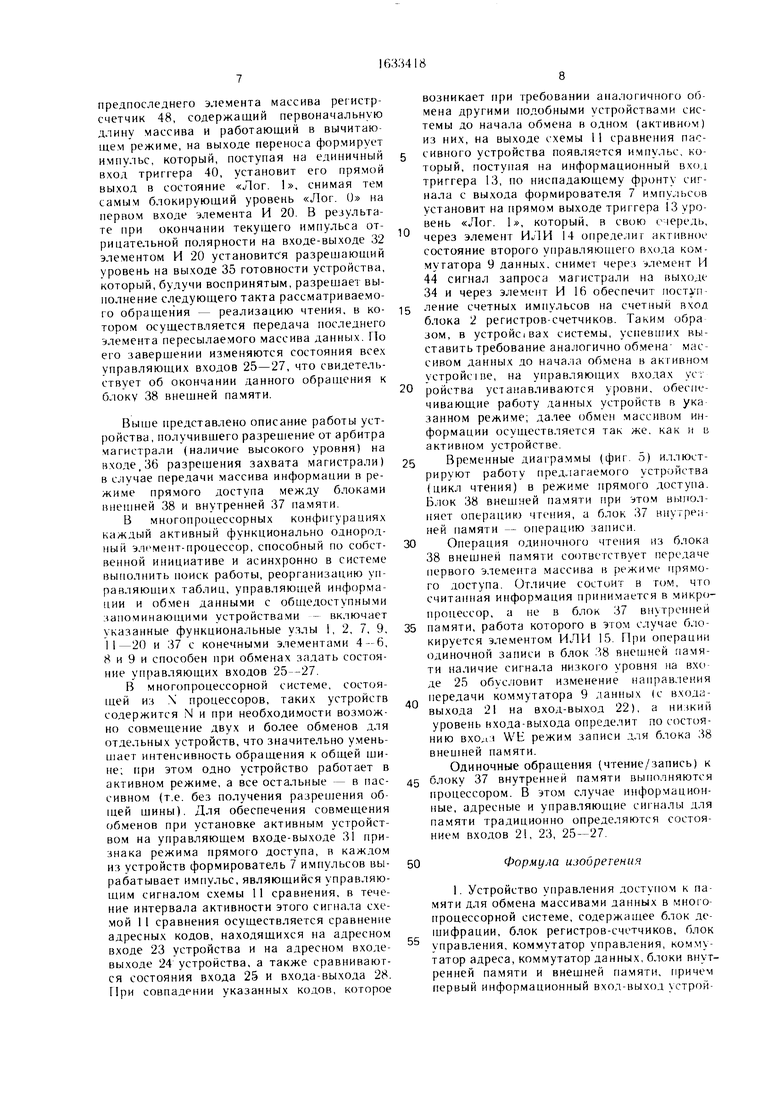

5 Временные диаграммы (фиг. 5) иллюстрируют работу предлагаемого устройства (цикл чтения) в режиме прямого доступа. Блок 38 внешней памяти при этом выполняет операцию чтения, а блок 37 miyi Peii ней памяти - операцию записи.

0 Операция одиночного чтения из блока 38 внешней памяти соответствует передаче первого элемента массива в режиме прямого доступа. Отличие состоит в том, что считанная информация принимается в микропроцессор, а не в блок 37 вн тренней

5 памяти, работа которого в этом случае блокируется элементом ИЛИ 15. При операции одиночной записи в блок 38 внешней памяти наличие сигнала низкого уровня на входе 25 обусловит изменение направления передачи коммутатора 9 данных (с входа- выхода 21 на вход-выход 22), а низкий уровень входа-выхода определит по состоянию WE режим записи для блока 38 внешней памяти.

Одиночные обращения (чтение/запись) к

5 блоку 37 внутренней памяти выполняются процессором. В этом случае информационные, адресные и управляющие сигналы для памяти традиционно определяются состоянием входов 21, 23, 25-27.

Формула изобретения

1. Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе, содержащее блок дешифрации, блок регистров-счетчиков, блок управления, коммутатор управления, коммутатор адреса, коммутатор данных, блоки внутренней памяти и внешней памяти, причем первый информационный вход-выход стройУ

IU

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

Изобретение относится к вычислительной технике и предназначено для работы в мультипроцессорной системе обработки данных, использующей общую информационную шину для доступа к общим ресурсам, 3/00, 3/04, ДОв частности к общей памяти группы процессоров или системы в целом. Цель изобретения - повышение производительности многопроцессорной системы за счет уменьшения времени работы с общей шиной процессора и интенсивности обращения к ней. Устройство содержит блок 1 дешифрации, блок 2 регистров-счетчиков, блок 3 управления, коммутатор 4 управления, коммутатор 8 адреса, коммутатор 9 данных, блоки 37 и 38 внутренней и внешней памяти. Устройство дополнительно содержит мультиплексор 12, схим I 1 сравнения, регистр-счегчик 10, коммутаторы 5. 6, формирователь 7 импульсов, триггер 13, элементы ИЛИ 14,15, элементы И 16-20. Это позволяет исключить буферизацию передаваемых из памяти-источника к памяти-приемнику данных, что уменьшает время загрузки массива за счет уменьшения интенсивности обращения процессора к общей шине. 3 з.п. ф-лы, 5 ил. & (Л

ства подключен к первому информационному входу-выходу коммутатора данных и к информационному входу блока регисгров- счетчиков, первый и вюрой входы занесения которого соответственно соединены с первым и вторым управляющими выходами блока дешифрации, группа разрядов первого информационного входа которого подключена к разрядам адресного входа устройства, который соединен с информационным входом коммутатора адреса, информационный вход-выход которою соединен с адресным входом-выходом устройства, входы- выходы признаков режима, памяти и обращения устройства подключены к соответствующим информационным выходам коммутатора управления, из которых два последних соответственно соединены с входом признака памяти и входом признака обращения блока управления, вход синхронизации которого подключен к внешнему син- ронизирующему входу устройства, управляющий вход коммутатора управления соединен с одноименным входом коммутатора адреса, а соответствующие информационные входы коммутатора управления подключены к входам признаков режима, памяти, обращения устройства, с которыми соединены одноименные входы блока дешифрации, первый управляющий вход коммутатора данных соединен с входом признака режима устройства, второй информационный вход- выход - с информационным входом-выходом блока внешней памяти и с вюрым информационным входом-выходом устройства, отличающееся тем, что, с целью повышения производительности многопроцессорной системы за счет уменьшения времени работы с общей шиной процессора и интенсивности обращения к ней, в него введены мультиплексор, схема сравнения, регистр-счетчик, коммутаторы, формирователь импульсов, триггер, элементы ИЛИ, элементы И, причем первый информационный вход-выход устройства подключен к входу соответствующих разрядов второго информационного входа блока дешифрации и к информационному входу-выходу блока внутренней памяти, адресный вход которого соединен с информационным выходом мультиплексора, первый информационный вход которого соединен с информационным выходом блока регистров счетчиков, а второй информационный вход соединен с адресным входом устройства и с первым входом первой группы входов схемы сравнения, второй вход первой группы входов которой подключен к входу признака режима устройства, второй вход второй группы входов - к входу-выходу признака режима устройства, первый вход второй группы входов - к информационному выходу коммутатора адреса, управляющий вход которого соединен с одноименными входами первого и второго коммутаторов, входом разрешения захвата магистрали устройства

0

5

0

5

0

0

5

0

и первым входом первого элемента ИЛИ. выход которого соединен с вторым управляющим входом коммутатора данных, первым входом первого элемента И и первым управляющим входом блока дешифрации, второй вход первого элемента ИЛИ подключен к прямому выходу первого триггера, синхронизирующий вход которого соединен с управляющим входом схемы сравнения и с выходом формирователя импульсов, информационный вход триггера соединен с выходом схемы сравнения, а вход установки нуляс входом признака обращения

устройства и первым входом второго элемента И, второй вход которого соединен с входом признака памяти устройства, а выход - с входом управления выборкой блока внутренней памяти, управляющий вход записи- чтения которого подключен к выходу третьего элемента И, первый вход которого соединен с входом признака режима устройства, управляющий вход мультиплексора подключен к выходу признака прямого доступа блока дешифрации, второму входу третьего элемента И, первому инверсному входу четвертого элемента И и к информационному входу первого коммутатора, информационный выход которого соединен с входом-выходом признака прямого доступа устройства, инверсным входом формирователя импульсов и входом признака прямого доступа блока управления, выход готовности которого соединен с входом-выходом системной готовности устройства, информационным входом второго коммутатора, вторым входом первого элемента И и вторым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к третьему входу второго элемента И, а второй вход - к выходу признака внешнего обращения блока дешифрации, выход готовности которого соединен с первым входом пятого элемента И, выход которого подключен к выходу готовности устройства, второй вход соединен с информационным выходом второго коммутатора, третий инверсный вход - с выходом запроса магистрали устройства и выходом запроса магистрали блока дешифрации, вход синхронизации и второй управляющий вход которого соединен соответственно с внешним синхронизирующим входом устройства и с управляющим выходом блока регистров-счетчиков, счетный вход которого подключен к выходу первого элемента И, адресный вход-выход устройства соединен с информационным входом регистра-счетчика, счетный и управляющий входы которого подключены соответственно к первому и второму выходам блока управления, выход регистра-счетчика подключен к адресному входу блока внешней памяти, управляющий вход записи-чтения которого соединен с входом-выходом признака режима устройства, а вход управления выборкой соединен с

11

выходом управления выборкой внешней памяти блока управления

2 Устройство по п 1, отличающееся тем, что блок дешифрации содержит дешифра гор, два триггера, счетчик, три элемента И, элемент ИЛИ, первый и второй стробирую- щие входы дешифратора соединены с вхо дами признаков режима и памяти блока, младшие разряды первого информационного входа которого соединены с адресными входами дешифратора, а старшие разряды первого информационного входа блока соединены с входами первого элемента И, выход которого соединен с информационным входом дешифратора, выходом признака внешнего обращения блока и первым инверсным входом второго элемента И, второй вход которого подключен к входу признака обращения блока, синхронизирующему входу первого триггера и первому входу третьего элемента И, второй вход которого соединен с прямым выходом второго триггера, информационный вход которого соединен с входом уровня логического нуля блока, синхронизирующий вход второго триггера подключен к первому управляющему входу блока и третьему инверсному входу второго элемента И, а единичный вход установки соединен с третьим выходом дешифратора и входом записи счетчика, информационный вход которого соединен с вторым информационным входом блока, а счетный вход - с выходом третьего элемента И, третий вход которого подключен к входу синхронизации блока, выход готовности и второй управляющий вход которого соединены с прямым выходом и единичным входом установки первого ipurrepa соответственно, информационный вход которого подключен к инверсному выходу второго триггера, выходу признака прямого доступа блока и к первому входу элемента ИЛИ, второй инверсный вход которого соединен с выходом счетчика и четвертым входом третьего элемента И, выход элемента ИЛИ соединен с четвертым входом второго элемента И, выход которого соединен с выходом запроса магистрали блока, и первый и второй управляющие выходы которою соединены с первым

12

и вторым выходами дешифратора соответственно.

3Устройство по п 1, отличающееся тем, что блок регистров-счетчиков содержит два

регистра-счетчика, информационные входы которых подключены к информационному входу блока, информационный выход которого соединен с выходом первого регистра- счетчика, счетный вход которого соединен

со счетным входом второго регистра-счетчика и со счетным входом блока, первый и второй входы занесения которого подклю чены к управляющим входам первого ч второго регистров-счетчиков, выход переноса второго регистра-счетчика является управляющим выходом блока

4Устройство по п I, отличающееся тем, что блок управления содержит регистр сдвига, коммутатор, трииер, формирователь ИМПУЛЬСОВ, два элемента И, элемент ИЛИ, первый инверсный вход которого соединен с управляющим входом коммутатора, единичным входом установки триггера, входом формирователя ИМПУЛЬСОВ и ьыходом первого элемента И, первый и второй входы которого соединены с входом признака памяти

5 и входом признака обращения блока, второй управляющий выход которого подключен к выходу формирователя импульсов и к синхронизирующему входу триггера, информационный вход которою соединен с входом уровня логического нуля блока, инверсный

0 выход триггера соединен с информационным входом регистра сдвига, вход установки н ля которого соединен г выходом элемента ИЛИ, второй вход которого соединен с выходом вюрого элемента И, первый инверс ный вход которого подключен к входу при5 знака прямого доступа блока, второй вход - к третьему выходу регистра сдвига, второй выход которого соединен с первым управляющим выходом блока и информационным входом третьего коммутатора, информацией

0 ный выход которого соединен с выходом готовности блока, вход синхронизации и выход управления выборкой внешней памяти которого подключены к синхронизирующему входу и первому выходу регистра сдвига соответственно

-

-

Фиг 2

41

48

у

Фиг.З

Фиг. 4

ra«

| Патент США „Чд 4481578, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Самонаклад книжных блоков | 1956 |

|

SU108969A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-20—Подача