Л

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах на основе микроэвм для увеличения объема непосредственно адресуемой памяти Целью изобретения является расширение области применения за счет увеличения объема подключаемой оперативной памяти.

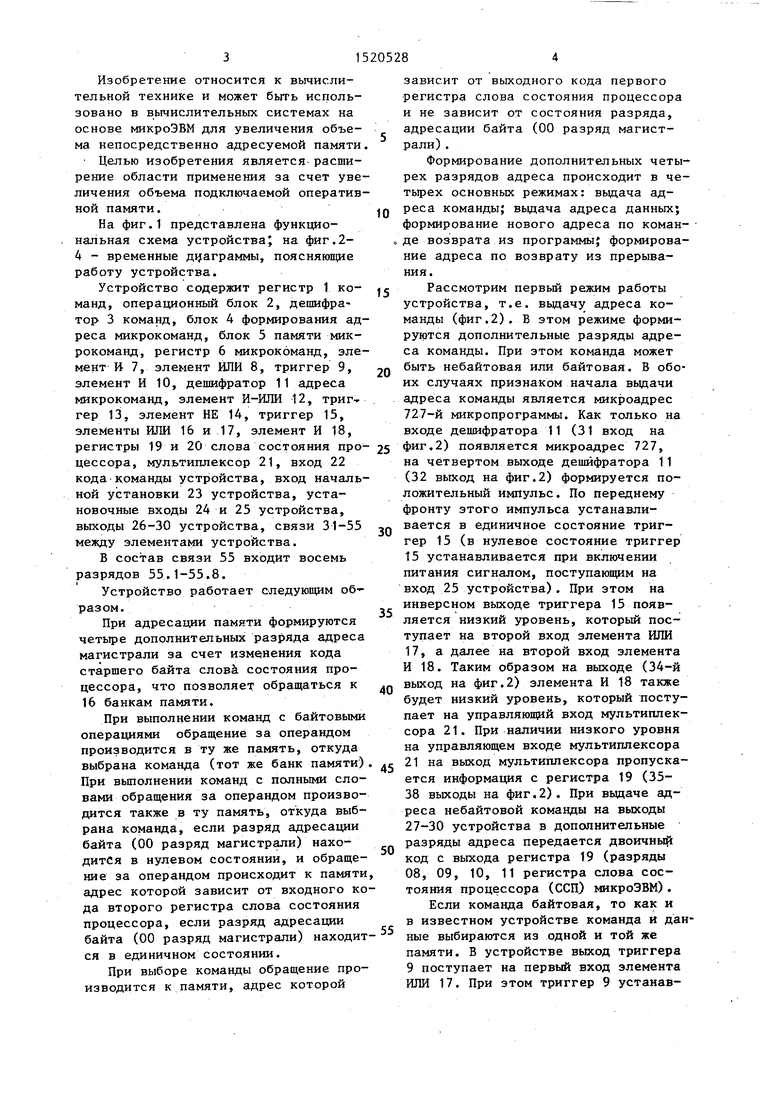

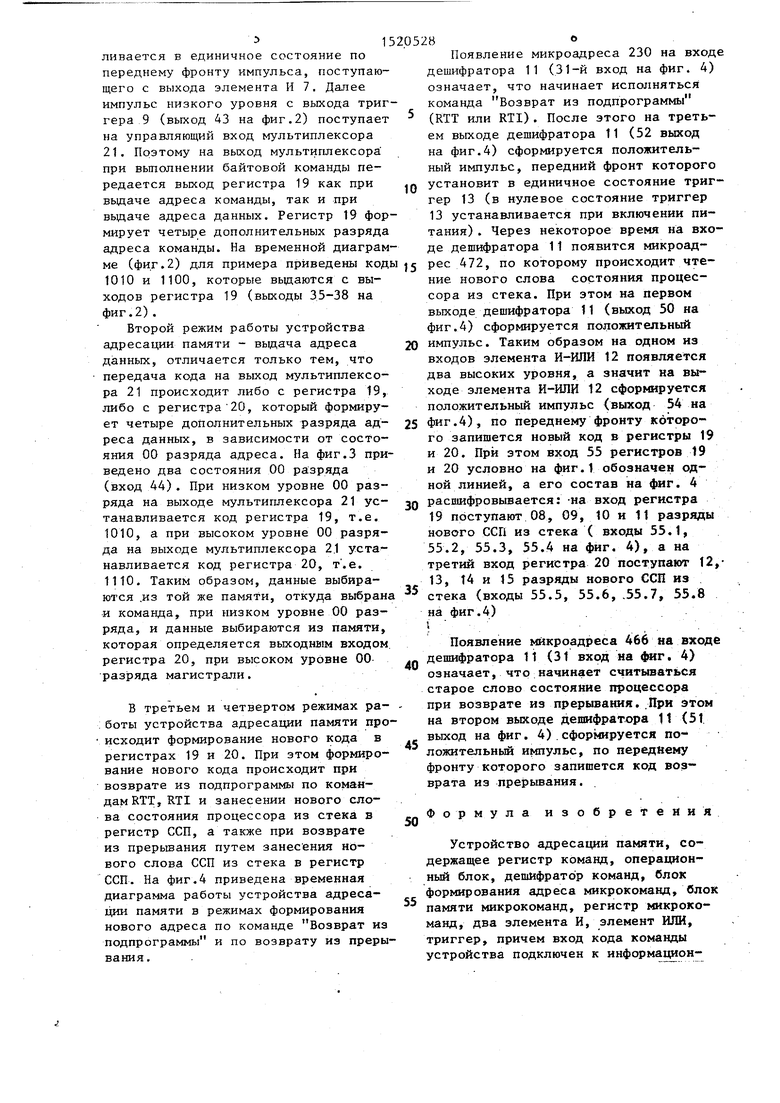

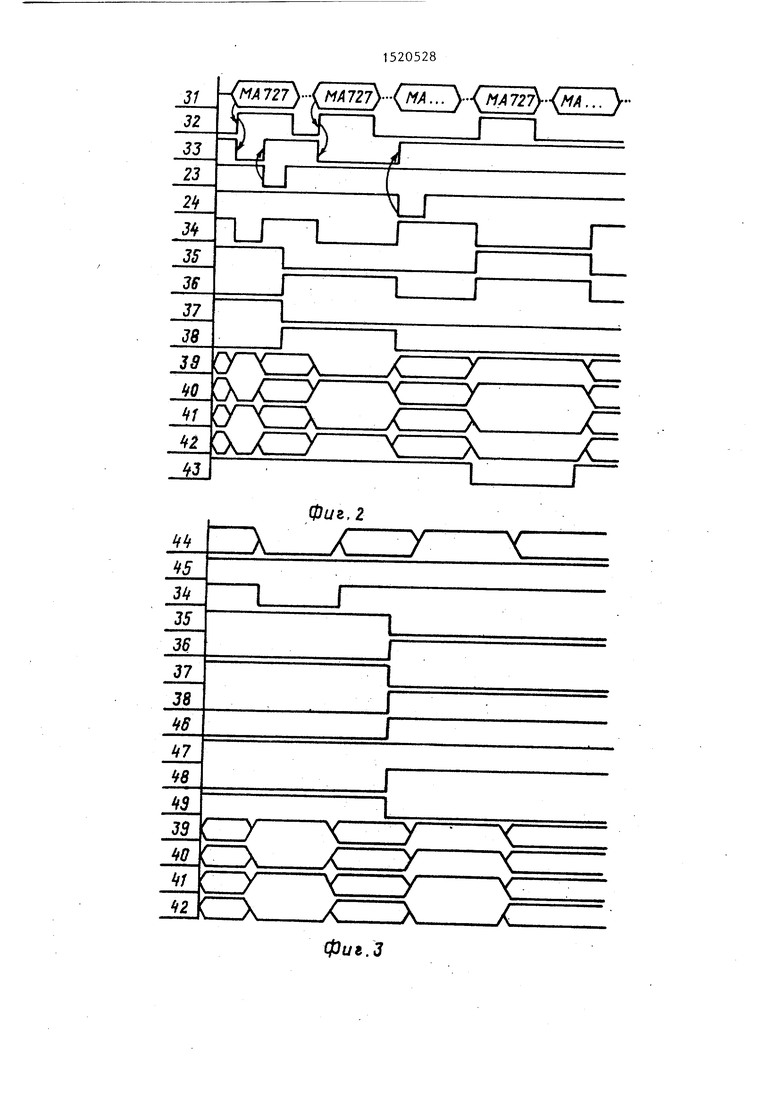

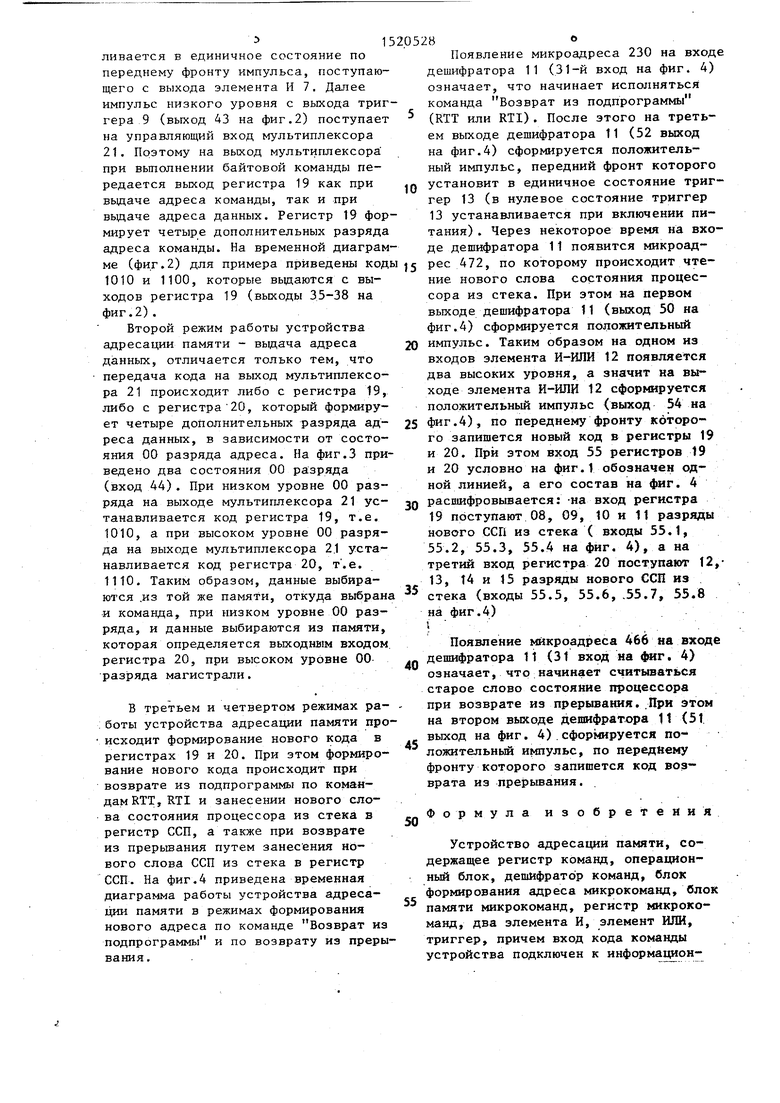

На фиг.1 представлена функциональная схема устройства; на фиг.2- 4 - временные дI aгpaммы, поясняющие работу устройства.

Устройство содержит регистр 1 команд, операционный блок 2, дешифратор 3 команд, блок 4 формирования адреса микрокоманд, блок 5 памяти микрокоманд, регистр 6 микрокоманд, элемент И 7, элемент ИЛИ 8, триггер 9, элемент И 10, дешифратор 11 адреса микрокоманд, элемент И-ИЛИ 12, триггер 13, элемент НЕ 14, триггер 15, элементы ИЛИ 16 и 17, элемент И 18, регистры 19 и 20 слова состояния процессора, мультиплексор 21, вход 22 кода команды устройства, вход начальной установки 23 устройства, установочные входы 24 и 25 устройства, выходы 26-30 устройства, связи 31-55 между элементами устройства.

В состав связи 55 входит восемь разрядов 55.1-55.8.

Устройство работает следующим образом.

При адресации памяти формируются четьфе дополнительных разряда адреса магистрали за счет изменения кода старшего байта слов& состояния процессора, что позволяет обращаться к 16 банкам памяти.

При выполнении команд с байтовыми операциями обращение за операндом производится в ту же память, откуда выбрана команда (тот же банк памяти) При вьшолнении команд с полными словами обращения за операндом производится также в ту память, откуда выбрана команда, если разряд адресации байта (00 разряд магистрали) находится в нулевом состоянии, и обращение за операндом происходит к памяти адрес которой зависит от входного кода второго регистра слова состояния процессора, если разряд адресации байта (00 разряд магистрали) находится в единичном состоянии.

При выборе команды обращение производится к памяти, адрес которой

0

5

0

5

0

5

0

5

зависит от выходного кода первого регистра слова состояния процессора и не зависит от состояния разряда, адресации байта (00 разряд магистрали) .

Формирование дополнительных четырех разрядов адреса происходит в четырех основных режимах: выдача адреса команды; выдача адреса данных; формирование нового адреса по команде возврата из программыJ формирование адреса по возврату из прерывания.

Рассмотрим первый режим работы устройства, т.е. вьщачу адреса команды (фиг.2). В этом режиме формируются дополнительные разряды адреса команды. При этом команда может быть небайтовая или байтовая. В обоих случаях признаком начала выдачи адреса команды является микроадрес 727-й микропрограммы. Как только на входе дешифратора 11 (31 вход на фиг.2) появляется микроадрес 727, на четвертом выходе дешифратора 11 (32 выход на фиг.2) формируется положительный импульс. По переднему фронту этого импульса устанавливается в единичное состояние триггер 15 (в нулевое состояние триггер 15 устанавливается при включении питания сигналом, поступаюпщм на вход 25 устройства), При этом на инверсном выходе триггера 15 появляется низкий уровень, который поступает на второй вход элемента ИЛИ 17, а далее на второй вход элемента И 18. Таким образом на выходе (34-й выход на фиг.2) элемента И 18 также будет низкий уровень, который поступает на управляющими вход мультиплексора 21. При наличии низкого уровня на управляющем входе мультиплексора 21 на выход мультиплексора пропускается информащя с регистра 19 (35- 38 выходы на фиг.2). При вьздаче адреса небайтовой команды на выходы 27-30 устройства в дополнительные разряды адреса передается двоичный код с выхода регистра 19 (разряды 08, 09, 10, 11 регистра слова состояния процессора (ССП) микроЭВМ).

Если команда байтовая, то как и в известном устройстве команда и дан- йые выбираются из одной и той же памяти. В устройстве выход триггера 9 поступает на первый вход элемента ИЛИ 17. При этом триггер 9 устанавливается в единичное состояние по переднему фронту импульса, поступающего с выхода элемента И 7, Далее импульс низкого уровня с выхода триггера 9 (выход 43 на фиг.2) поступает на управляющий вход мультиплексора 21. Поэтому на выход мультиплексора при вьшолнении байтовой команды передается выход регистра 19 как при выдаче адреса команды, так и при вьщаче адреса данных. Регистр 19 формирует четыре дополнительных разряда адреса команды. На временной диаграмме (фиг.2) для примера приведены коды j pec 472, по которому происходит чте1010 и 1100, которые вьвдаются с выходов регистра 19 (выходы 35-38 на фиг.2).

Второй режим работы устройства адресации памяти - выдача адреса данных, отличается только тем, что

передача кода на выход мультиплексора 21 происходит либо с регистра 19, либо с регистра 20, который формирует четыре дополнительных разряда адреса данных, в зависимости от состояния 00 разряда адреса. На фиг.З приведено два состояния 00 разряда (вход 44). При низком уровне 00 разряда на выходе мультиплексора 21 устанавливается код регистра 19, т.е. 1010, а при высоком уровне 00 разряда на выходе мультиплексора 2.1 устанавливается код регистра 20, т .е. 1110. Таким образом, данные выбираются .из той же памяти, откуда выбрана и команда, при низком уровне 00 разряда, и данные выбираются из памяти, которая определяется выходнвм входом, регистра 20, при высоком уровне 00- разряда магистрали.

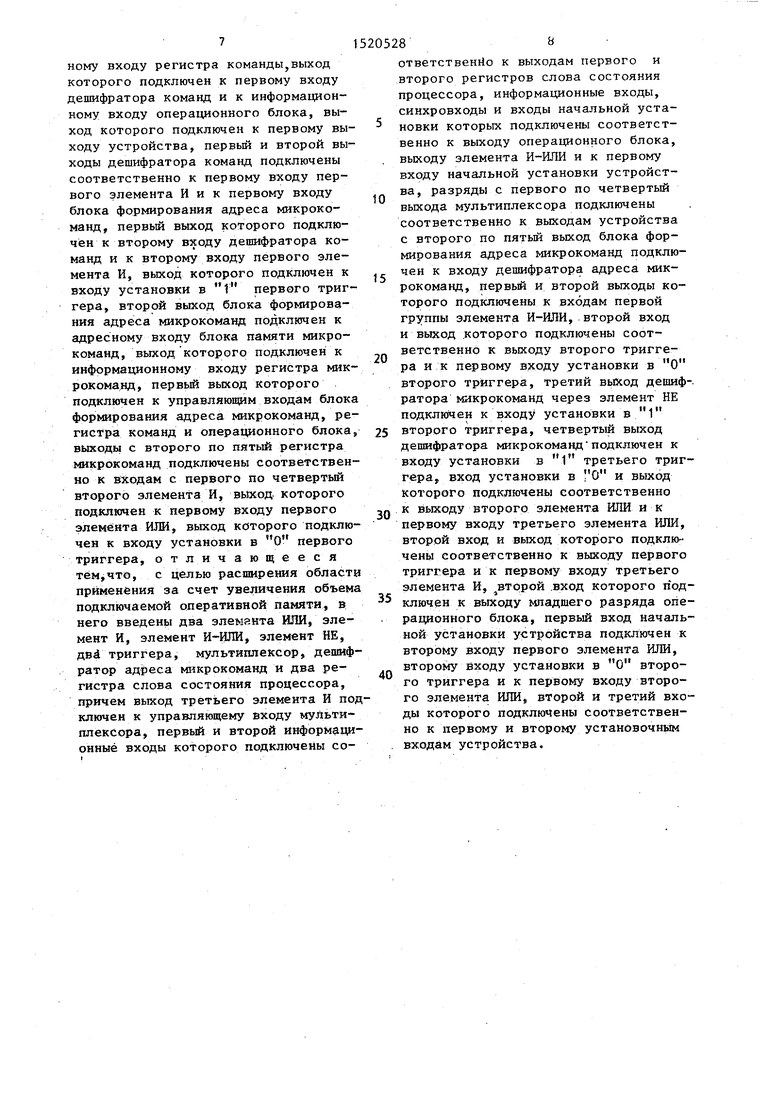

В третьем и четвертом режимах ра- :боты устройства адресации памяти происходит формирование нового кода в регистрах 19 и 20. При этом формирование нового кода происходит при возврате из подпрограммы по командам RTT,RTI и занесении нового слова состояния процессора из стека в регистр ССП, а также при возврате

из прерьюания путем занес ения нового слова ССП из стека в регистр ССП. На фиг.4 приведена временная диаграмма работы устройства адресации памяти в режимах формирования нового адреса по команде Возврат из подпрограммы и по возврату из прерывания.

ние нового слова состояния процессора из стека. При этом на первом выходе дешифратора 11 (выход 50 на фиг.4) сформируется положительный

20 импульс. Таким образом на одном из входов элемента И-ИЛИ 12 появляется два высоких уровня, а значит на выходе элемента И-ИЛИ 12 сформируется положительный импульс {выход 54 на

25 фиг.4), по переднему фронту которого запишется новый код в регистры 19 и 20. При этом вход 55 регистров 19 и 20 условно на фиг.1 обозначен одной линией, а его состав на фиг. 4

30 расшифровывается: -на вход регистра 19 поступают 08, 09, 10 и 11 разряды нового ССП из стека ( входы 55.1, 55.2, 55.3, 55.4 на фиг. 4), а на третий вход регистра 20 поступают 12,- 13, 14 и 15 разряды нового ССП из

35

40

45

50

55

стека (входы 55.5, 55.6, .55.7, 55.8 на фиг.4)

Появление микроадреса 4б6 на входе дешифратора 11 (31 вход на г. 4) означает, что начинает считываться старое слово состояние процессора при возврате из прерывания..При этом на втором выходе дешифратора Ц (51 выход на фиг. 4).сформируется положительный импульс, по переднему фронту которого запишется код воз врата из прерьшания.

Формула изобретения

Устройство адресации памяти, содержащее регистр команд, операционный блок, дешифратор команд, блок формирования адреса микрокоманд, блок памяти микрокоманд, регистр микрокоманд, два элемента И, элемент ИЛИ, триггер, причем вход кода команды устройства подключен к информацион-

2,0528о

Появление микроадреса 230 на входе дешифратора 11 (31-й вход на фиг. 4) означает, что начинает исполняться команда Возврат из подпрограммы (RTT или RTI). После этого на третьем выходе дешифратора 11 (52 выход на фиг.4) сформируется положительный импульс, передний фронт которого .Q установит в единичное состояние триггер 13 (в нулевое состояние триггер 13 устанавливается при включении питания) . Через некоторое время на входе дешифратора 11 появится микроадние нового слова состояния процессора из стека. При этом на первом выходе дешифратора 11 (выход 50 на фиг.4) сформируется положительный

0 импульс. Таким образом на одном из входов элемента И-ИЛИ 12 появляется два высоких уровня, а значит на выходе элемента И-ИЛИ 12 сформируется положительный импульс {выход 54 на

5 фиг.4), по переднему фронту которого запишется новый код в регистры 19 и 20. При этом вход 55 регистров 19 и 20 условно на фиг.1 обозначен одной линией, а его состав на фиг. 4

0 расшифровывается: -на вход регистра 19 поступают 08, 09, 10 и 11 разряды нового ССП из стека ( входы 55.1, 55.2, 55.3, 55.4 на фиг. 4), а на третий вход регистра 20 поступают 12,- 13, 14 и 15 разряды нового ССП из

5

0

5

0

5

стека (входы 55.5, 55.6, .55.7, 55.8 на фиг.4)

Появление микроадреса 4б6 на входе дешифратора 11 (31 вход на г. 4) означает, что начинает считываться старое слово состояние процессора при возврате из прерывания..При этом на втором выходе дешифратора Ц (51 выход на фиг. 4).сформируется положительный импульс, по переднему фронту которого запишется код воз врата из прерьшания.

Формула изобретения

Устройство адресации памяти, содержащее регистр команд, операционный блок, дешифратор команд, блок формирования адреса микрокоманд, блок памяти микрокоманд, регистр микрокоманд, два элемента И, элемент ИЛИ, триггер, причем вход кода команды устройства подключен к информацион-

ному входу регистра команды,выход которого подключен к первому входу дешифратора команд и к информационному входу операционного блока, выход которого подключен к первому выходу устройства, первый и второй выходы дешифратора команд подключены соответственно к первому входу первого элемента И и к первому входу блока формирования адреса микрокоманд, первый выход которого подключен к второму входу дешифратора команд и к второму входу первого элемента И, выход которого подключен к входу установки в 1 первого триггера, второй выход блока формирования адреса микрокоманд подклкгчен к адресному входу блока памяти микрокоманд, выход которого подключен к информационному входу регистра микрокоманд, первый выход которого подключен к управляющим входам блока фop шpoвaния адреса микрокоманд, регистра команд и операционного блока, выходы с второго по пятый регистра микрокоманд подключены соответственно к входам с первого по четвертый второго элемента И, вьйсод которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к входу установки в О первого триггера, отличающееся тем,что, с целью расширения области применения за счет увеличения объема подключаемой оперативной памяти, в него введены два элемента ИЛИ, элемент И, элемент И-ЩТИ, элемент НЕ, двй триггера, мультиплексор, дешифратор ад|реса микрокоманд и два регистра слова состояния процессора, причем выход трет1эего элемента И подключен к управляющему входу мульти плексора, первый и второй ннформ ци- онныё входы которого подключены со10

15

520528В

ответственйо к выходам первого и второго регистров слова состояния процессора, информационные входы, синхровходы и входы начальной установки которых подключены соответственно к выходу операционного блока, выходу элемента И-ИЛИ и к первому входу начальной установки устройства, разряды с первого по четвертый выхода мультиплексора подключены соответственно к выходам устройства с второго по пятый выход блока формирования адреса микрокоманд подключен к входу дешифратора адреса микрокоманд, первьй и второй выходы которого подключены к входам первой группы элемента И-ИЛИ,.второй вход и выход которого подключены соответственно к выходу второго триггера и к первому входу установки в О второго триггера, третий вькод дешифратора микрокоманд через элемент НЕ подклнзчен к входу установки в 1 второго триггера, четвертый выход дешифратора микрокоманд подключен к входу установки в 1 третьего триггера, вход установки в 0 и выход которого подключены соответственно к выходу второго элемента ИЛИ и к первому входу третьего элемента ИЛИ,

второй вход и выход которого ПОДКЛЮ

чены соответственно к выходу первого триггера и к первому входу третьего элемента И, второй .вход которого п од- ключен к выходу младшего разряда операционного блока, первый вход начальной установки устройства подключен к второму входу первого элемента ИЛИ, второму входу установки в О второго триггера и к первому входу второго элемента ИЛИ, второй и третий входы которого подключены соответственно к первому и второму установочным входам устройства.

20

25

30

35

40

Фи&,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1984 |

|

SU1265776A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство адресации памяти | 1984 |

|

SU1251076A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство адресации памяти | 1986 |

|

SU1410039A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах на основе микроЭВМ. Цель изобретения - расширение области применения. Устройство содержит регистр 1 команд, операционный блок 2, дешифратор 3 команд, блок 4 формирования адреса микрокоманд, блок 5 памяти микрокоманд, регистр 6 микрокоманд, элементы И 7, 10, 18, элементы ИЛИ 8, 16, 17, элемент НЕ 14, триггеры 9, 13, 15, дешифратор 11 адреса микрокоманд, элемент И-ИЛИ 12, регистры 19, 20 слова состояния процессора, мультиплексор 21. Поставленная цель достигается за счет расширения области адресуемой памяти. 4 ил.

фиг.З

фцг. fy

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство адресации памяти | 1986 |

|

SU1410039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1988-04-29—Подача