Изобретение относится к вычислительной технике и может быть использовано для увеличения объема оперативной Пс1мяти при построении цифровых систем обработки данных на базе мини{микро-)-ЭВМ.

Известно устройство управления памятью со страничной организацией, содержащее регистры адреса страниц, регистры признака страниц, сумматоры и коммутатор 1.

Недостатками устройства являются большой объем оборудования и невысокое быстродействие за счет потерь времени в каждом цикле обращения к памяти на преобразование виртуального адреса в физический.

Наиболее близким к предлагаемому по технической сущности является устройство для связи запоминающего и арифметического устройств при формате адреса запоминающего устройства, превышающего.формат адреса арифметического устройства, содержащеекоммутатор, последовательно соединенные дешифратор, шифратор, регистры, выходы KOTOjxjx подключены к группе адресных входов запоминающего устройства и к управляющим входам коммутатора 2 .

Однако известное устройство не обеспечивает возможность работы од.новременно с разными областями памяти, находящимися в разных ее страницах без переключения регистра номера массива, что снижает быстродействие и ограничивает функциональные возможности устройства.

Цель изобретения - повышение

10 быстродействия устройства.

Поставленная цель достигается тем, что в устройство для сопряжения процессора с многоблочной памятью, содержащее регистр номера массива и блок памяти, входы/выходы которого являются информационными входами/выходами устройства, введены блок дешифраторов, группа канальных приемо-передатчиков,

20 дешифратор адреса, триггер, дешифратор управляющих сигналов,первый и второй входы которых подключены к группе управляющих входов/выходов устройства, а третий вход 25к выходу триггера, синхровход которого подключен к группе управляющих входов/выходов устройства, а информационный вход - к выходу дешифратора адреса, группа входов

30 которого соединена с группой вы-

ходов группы канальных приемо-передатчиков и группой входов регистра номера массива, группа выходов которого соединена с группой входов блока дшиифраторов и первой группой входов группы канальных приемо-передатчиков, вторая группа входов которых соединена с группой управляющих входов/выходов устройства, группа выходов блока дешифраторов соединена с группой управляющих входов блока памяти, второй выход дешифратора управляющих сигналов соединен с входом группы канальных приемо-передатчиков.

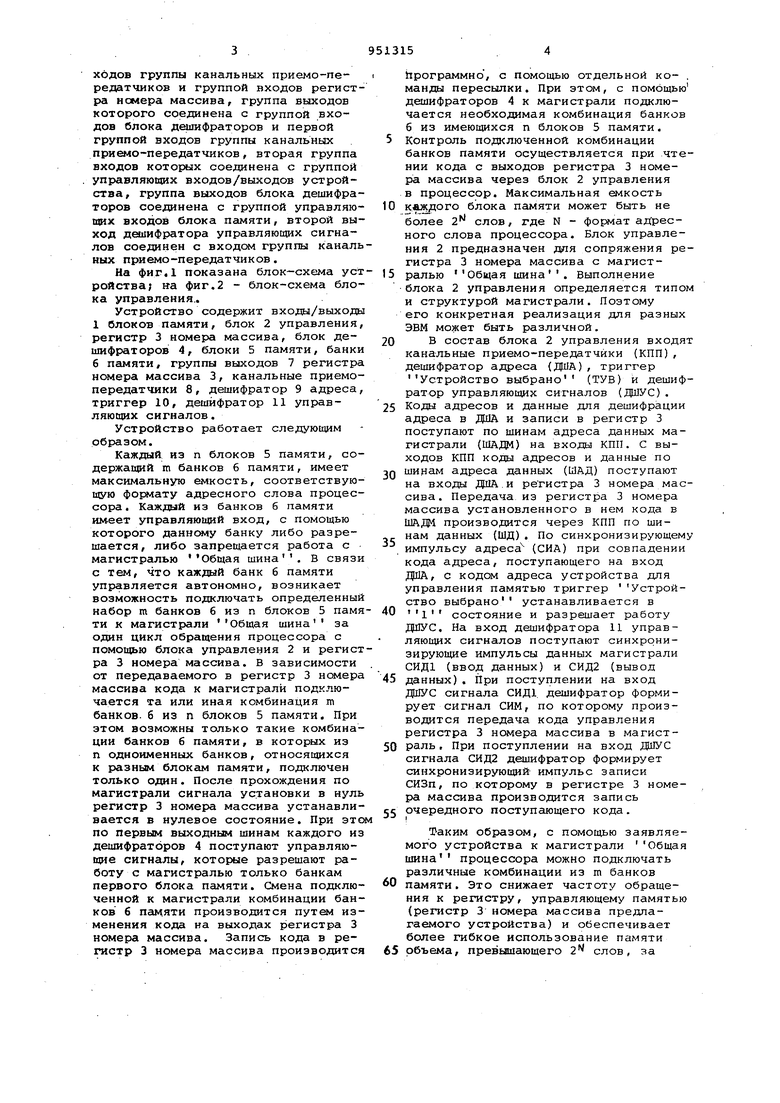

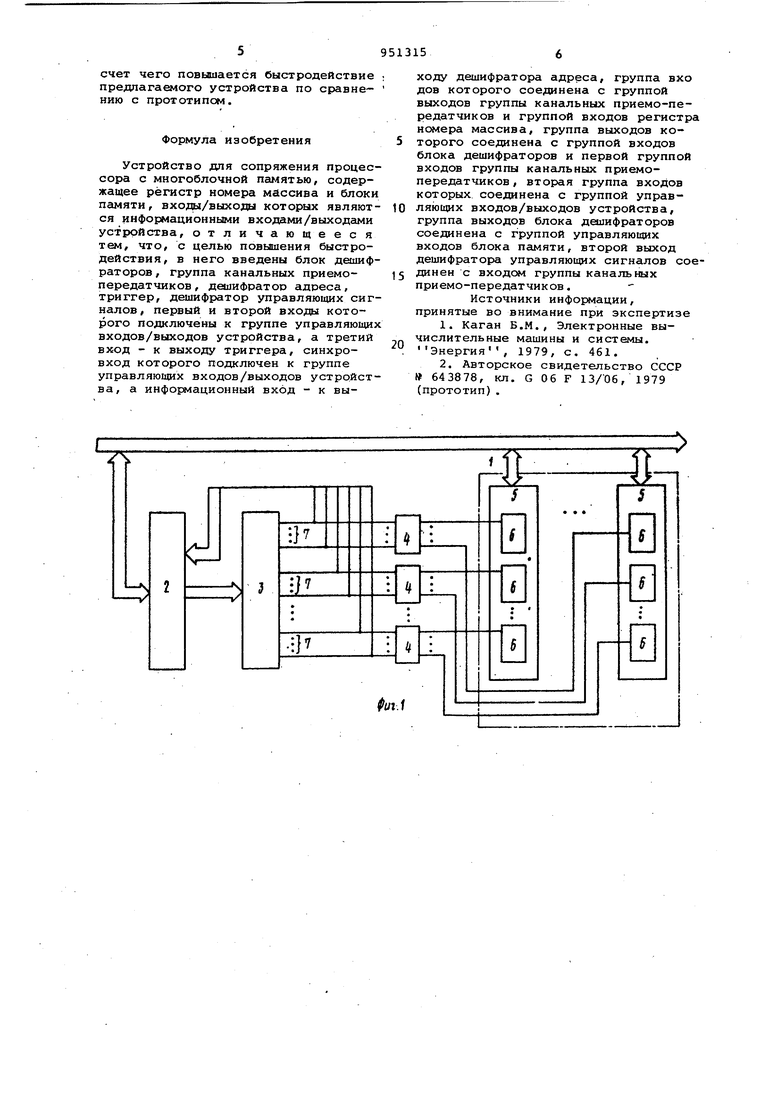

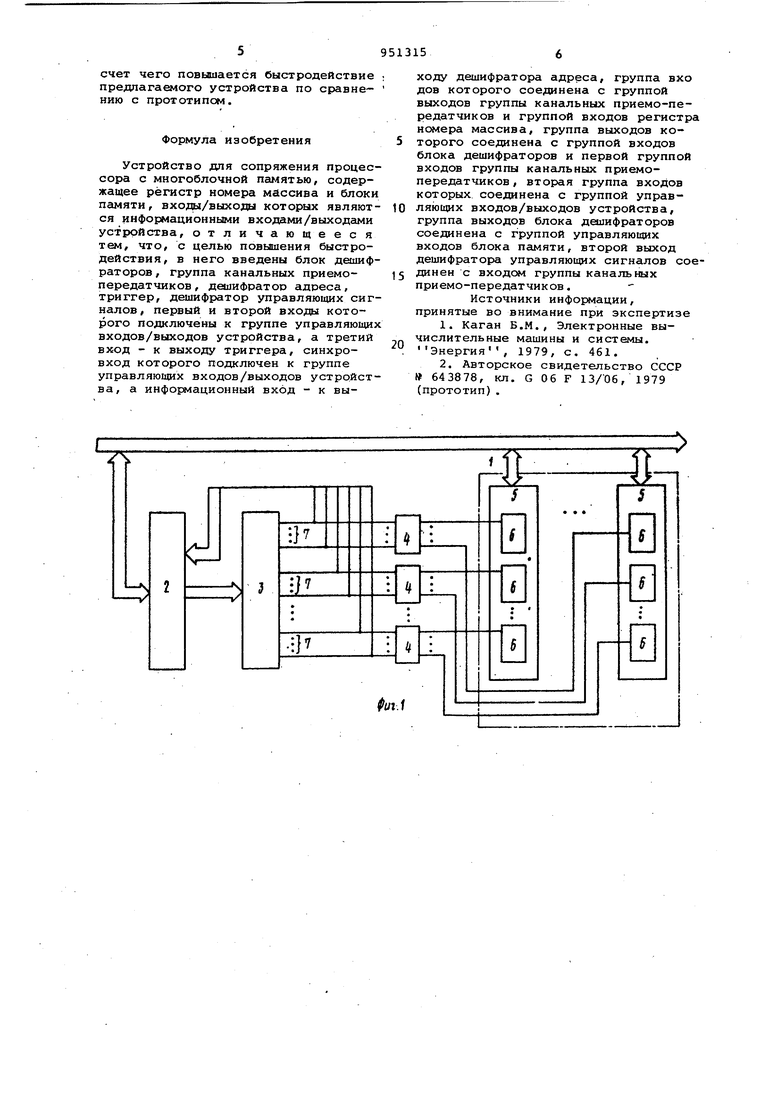

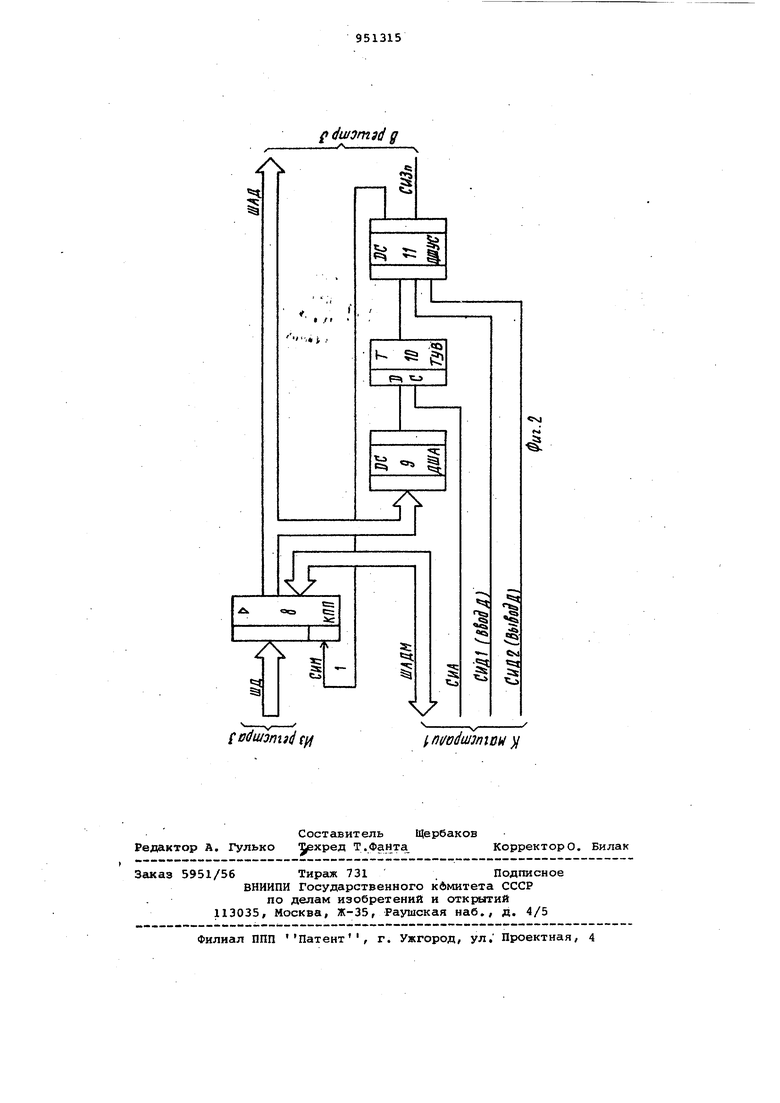

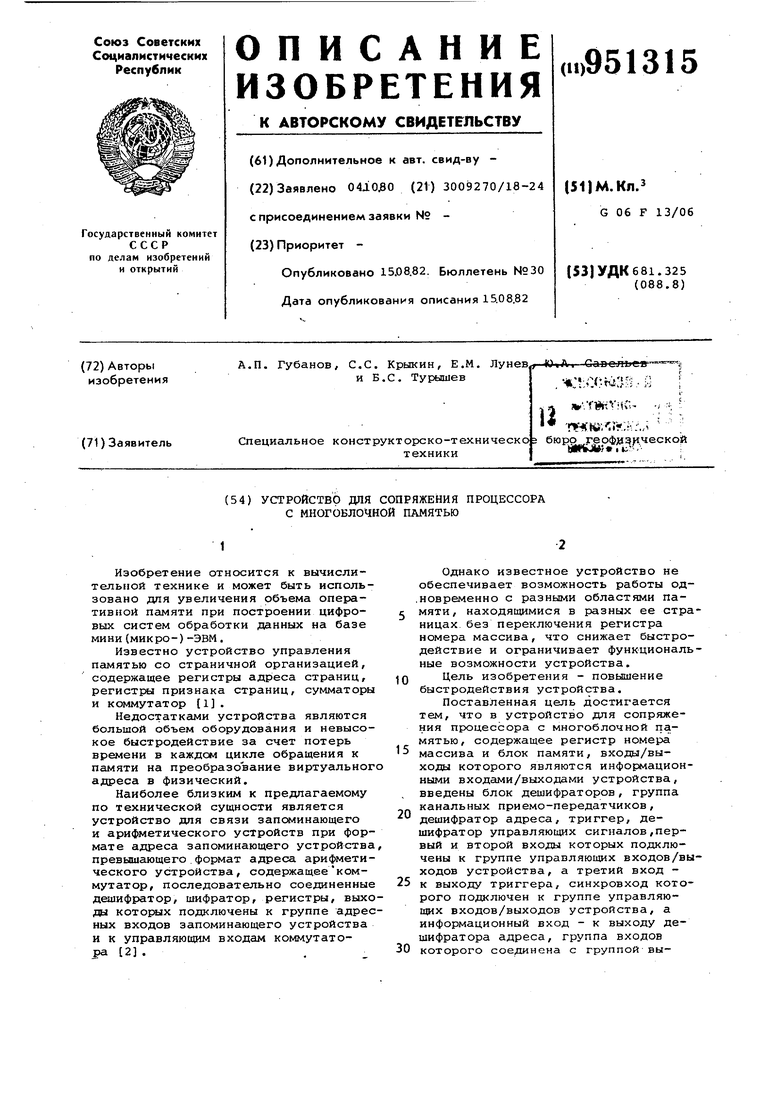

На фиг.1 показана блок-схема устройства; на фиг.2 - блок-схема блока управления..

Устройство содержит входы/выходы 1 блоков памяти, блок 2 управления, регистр 3 номера массива, блок дешифраторов; 4, блоки 5 памяти, банки 6 памяти, группы выходов 7 регистра номера массива 3, канальные приемопередатчики 8, дешифратор 9 адреса, триггер 10, дешифратор 11 управляющих сигналов.

Устройство работает следующим образом.

Каждый из п блоков 5 памяти, содержащий m банков 6 памяти, имеет максимальную емкость, соответствующую формату адресного слова процессора. Каждый из банков 6 памяти имеет управляющий вход, с помощью которого данному банку либо разрешается, либо запрещается работа с магистралью Общая шина . В связи с тем, что каждый банк 6 памяти управляется автономно, возникает возможность подключать определенный набор m банков б из п блоков 5 памяти к магистрали Общая шина за один цикл обращения процессора с помощью блока управления 2 и регистра 3 номера массива, в зависимости от передаваемого в регистр 3 номера массива кода к магистрали подключается та или иная комбинация т банков, б из п блоков 5 памяти. При этом возможны только такие комбинации банков 6 памяти, в которых из п одноименных банков, относящихся к разным блокам памяти, подключен только один. После прохождения по магистрали сигнала установки в нуль регистр 3 номера массива устанавливается в нулевое состояние. При этсм по первым выходным шинам каждого из дешифраторов 4 поступают управляющие сигналы, которые разрешают работу с магистралью только банкам первого блока памяти. Смена подключенной к магистрали комбинации банков б памяти производится путем изменения кода на выходах регистра 3 номера массива. Запись кода в регистр 3 номера массива производится

йрограммно, с помощью отдельной ко- . манды пересылки. При этом, с помощью дешифраторов 4 к магистрали подключается необходимая комбинация банков б из имеющихся п блоков 5 памяти. Контроль подключенной комбинации

банков памяти осуществляется при чтении кода с выходов регистра 3 номера массива через блок 2 управления в процессор. Максимальная емкость

каадого блока памяти может быть не более 2 слов, где N - формат адресного слова процессора. Блок управления 2 предназначен для сопряжения регистра 3 номера массива с магистралью Общая шина . Выполнение

блока 2 управления определяется типом и структурой магистрали. Поэтому его конкретная реализация для разных ЭВМ может быть различной.

В состав блока 2 управления входят канальные приемо-передатчйки (КПП), дешифратор адреса (ДША), триггер Устройство выбрано (ТУБ) и дешифратор управляющих сигналов (ДШУС).

Коды адресов и данные для дешифрации адреса в ДНА и записи в регистр 3 поступают по шинам адреса данных магистрали (ШАДМ) на входы КПП. С выходов КПП коды адресов и данные по

шинам адреса данных (ШАД) поступают на входы ДНА. и регистра 3 номера массива. Передача из регистра 3 номера массива установленного в нем кода в ШАДМ производится через КПП по шинам данных (ШД). По синхронизирующему импульсу адреса (СИА) при совпадении кода адреса, поступающего на вход дал, с кодом адреса устройства для управления памятью триггер Устройство выбрано устанавливается в

t I I I состояние и разрешает работу ДШУС. На вход дешифратора 11 управляющих сигналов поступают синхронизирующие импульсы данных магистрали СИД1 (ввод данных) и СИД2 (вывод

данных). При поступлении на вход ДШУС сигнала СИД1 дешифратор формирует сигнал СИМ, по которому производится передача кода управления регистра 3 номера массива в магистраль. При поступлении на вход ДШУС сигнала СИД2 дешифратор формирует синхронизирующий импульс записи СИЗп, по которому в регистре 3 номера массива производится запись

очередного поступающего кода.

Таким образом, с помощью заявляемого устройства к магистрали Общая шина процессора можно подключать различные комбинации из m банков

Пс1мяти. Это снижает частоту обращения к регистру, управляющему памятью (регистр 3 номера массива предлагаемого устройства) и обеспечивает более гибкое использование памяти

объема, превышающего слов, за

счет чего повышается быстродействие предлагаемого устройства по сравнению с прототипом.

Формула изобретения

Устройство для сопряжения процессора с многоблочной пзллячью, содержащее регистр номера массива и блоки памяти, входы/выходы которых являются информационными входами/выходами устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены блок дешифраторов, группа канальных приемопередатчиков, дешифратор адреса, триггер, дешифратор управляющих сигналов, первый и второй входы которого подключены к группе управляющих входов/выходов устройства, а третий вход - к выходу триггера, синхровход которого подключен к группе управляющих входов/выходов устройства, а информационный вход - к выходу дешифратора адреса, группа вхо дов которого соединена с группой выходов группы канальных приемо-передатчиков и группой входов регистра номера массива, группа выходов которого соединена с группой входов блока дешифраторов и первой группой входов группы канальных приемопередатчиков, вторая группа входов которых соединена с группой управляющих входов/выходов устройства, группа выходов блока дешифраторов соединена с группой управляющих входов блока памяти, второй выход дешифратора управляющих сигналов соединен с входом группы канальных приемо-передатчиков.

Источники информации, принятые во внимание при экспертизе

1.Каган Б.М., Электронные вычислительные машины и системы.

Энергия, 1979, с. 461.

2.Авторское свидетельство СССР 643878, кл. G Об F 13/0б, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

41п

41:

f duiomad g

/

f odujsmid ({/I

n{/0tlu/3ni0lii )j

Авторы

Даты

1982-08-15—Публикация

1980-10-04—Подача