Изобретение относится к вычислительной технике и может быть исполь- .зовано Б системах сбора информации.

Целью изобретения является повышение пропускной способности устройства.

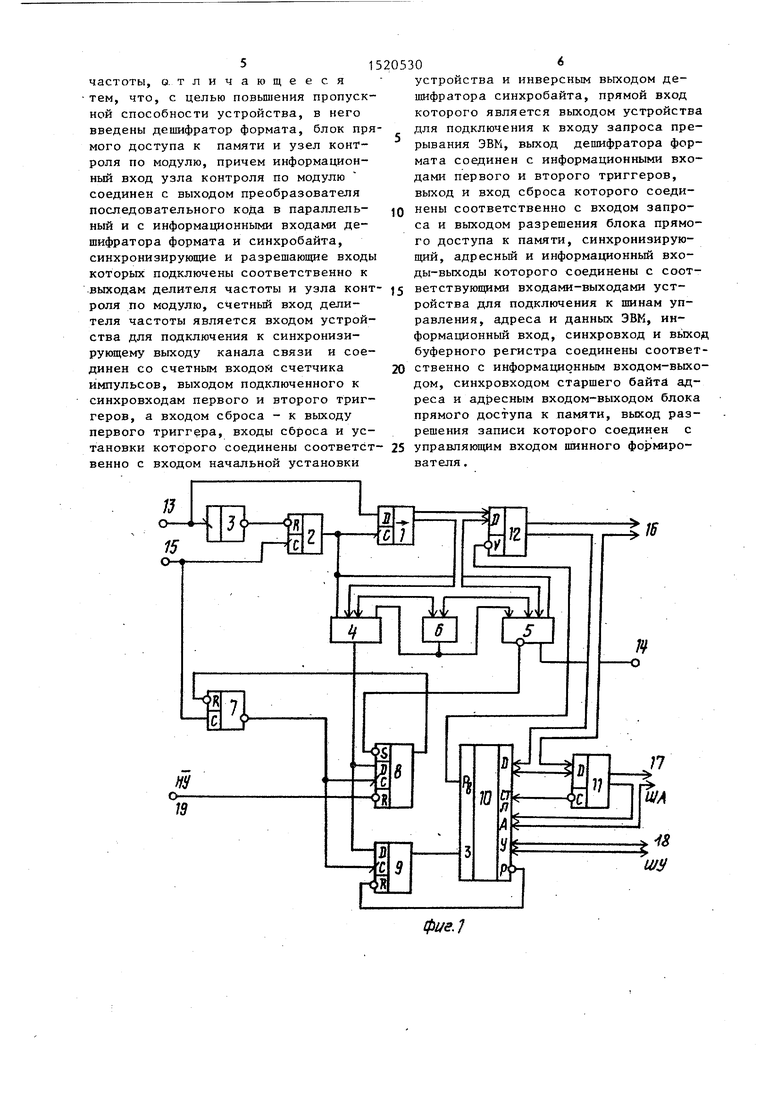

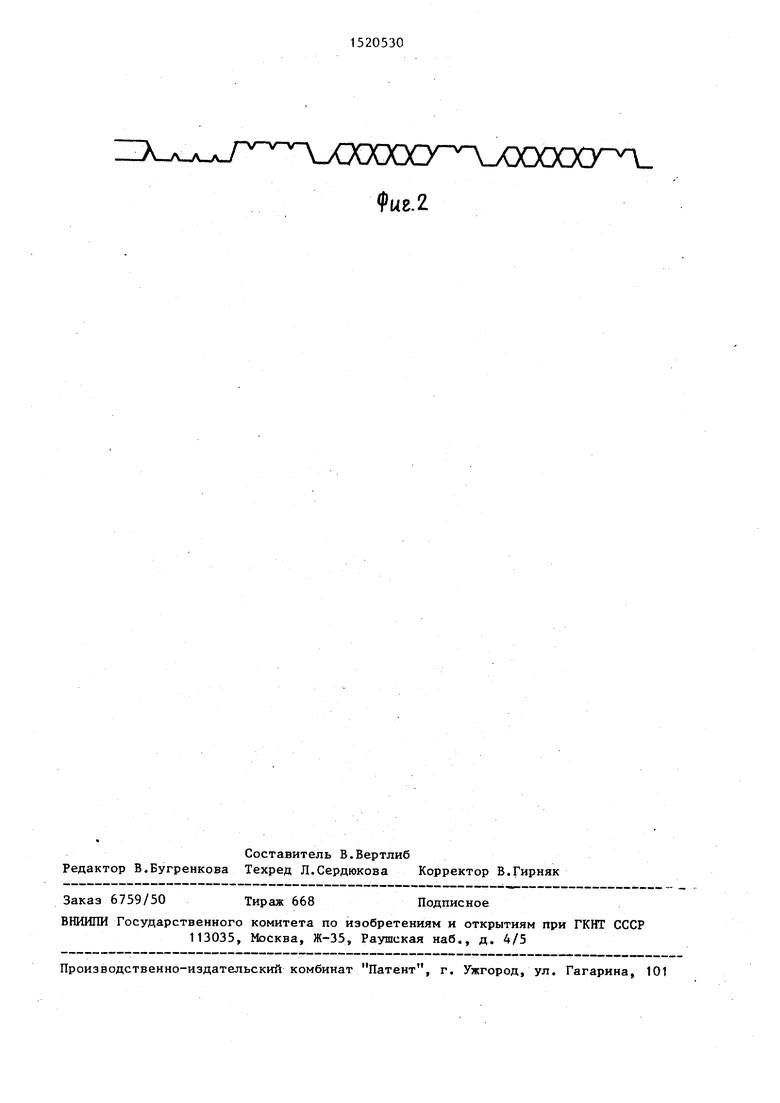

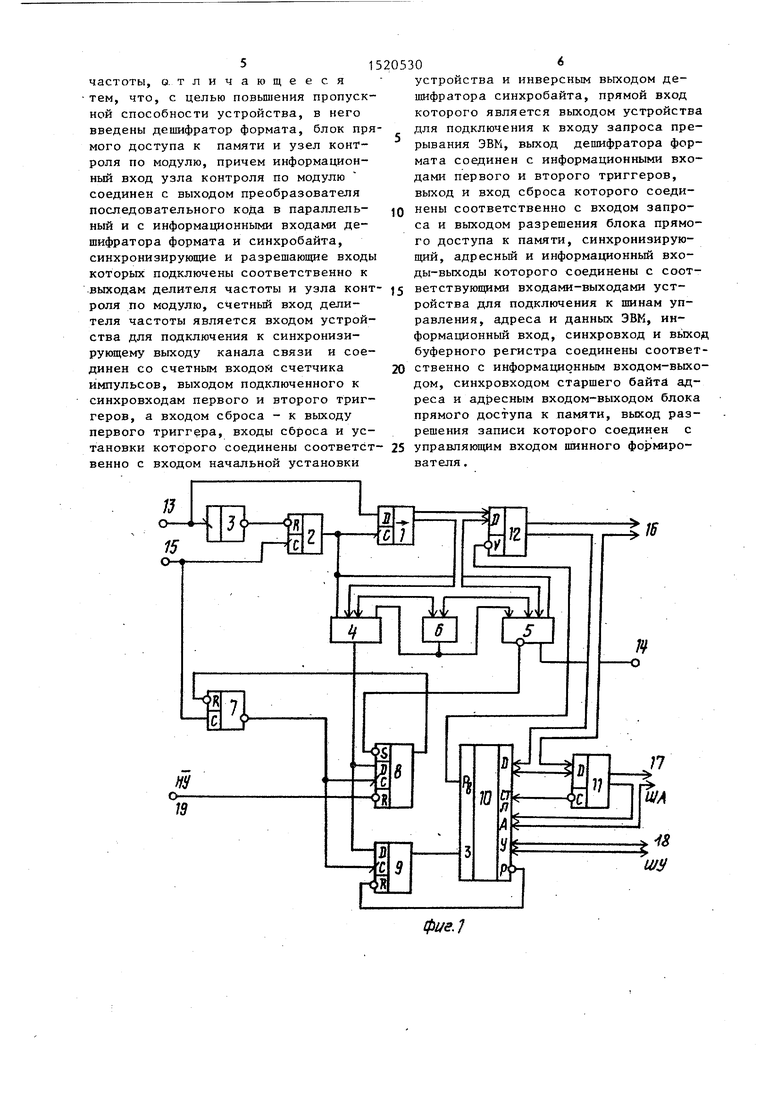

На фигЛ представлена функциональная схема устройства; на фиг.2 - пример принимаемой кодовой последовательности.

Устройство содержит (фиг. 1) преобразователь 1 последовательного да в параллельный (регистр сдвига), делитель 2 частоты,формирователь 3 импульсов, дешифраторы 4 и 5 формата и синхробайта, узел 6 контроля по модулю, счетчик 7 импульсов, триггеры 8 и 9, блок .10 прямого доступа к памяти, выполненный на микросхеме К580 ВТ 57, буферный регистр 11 и шинный формирователь 12, линии 13-19 внешних связей устройства.

Устройство функционирует следующим образом.

Пусть устройство принимает кодо вую последовательность типа (фиг, 2), состоящую из синхробайта (00001111) и информационных байтов, каждый из которых имеет нулевой стартовый бит, два единичных стоповых бита и один бит контроля по нечетности.

Приход первого нулевого бита при- нимаемой кодовой последовательности на вход 13 устройства вызывает появление импульса на выходе формирователя 3, который сбрасывает в нулевое состояние делитель 2. На выходе делителя 2 формируются импульсы (меандр) с частотой, равной частоте передачи кодовой последовательности. Таким образом благодаря сбросу в нулевое состояние делителя 2 по спаду входного сигнала, фронт сигнала на выходе делителя 2 приходится примерсл

ND

:п

со

но на середину каждого бита принимаемой кодовой последовательности. По этому фронту, информация с входа 13 устройства проталкивается в регистр 1. Как только в последнем окажется записанным код синхробайта, на выходе дешифратора 5 появится сигнал О, который установит триггер 8 в единичное состояние, разрешив тем самым работу счетчика 7. Одновременно на прямом выходе дешифратора 5 появится сигнал 1, котррый поступит на выход 14 запроса прерывания. Получив этот сигнал, процессор должен подготовить к работе блок 10, записав в него начальный адрес памяти, открытой для прямого доступа и длину вводимого в эту память массива информации, соответствующую принимаемой кодовой последовательности. Сигнал переполнения счетчика 7 формируется в тот момент, когда очередной байт вытолкнет из регистра 1 предыдущий байт. Если при этом в очередном байте первьй бит окажется нулевым (стар- товьй бит), два последних бита - единичными (стоповые биты), а проверка нечетности, осуществляемая узлом 6, даст положительный результат, то на выходе дешифратора 4 появится сигнал 1, который по окончании сигнала переполнения счетчика 7 будет записан в триггер 9, т.е. последний пе-. рейдет в единичное состояние и на его выходе сформирует -- сигнал запроса прямого доступа к памяти. Блок 10 по управляющей шине 18 запрашивает разрешение на прямой доступ к памяти и, получив по этой же шине разреше- ние, транслирует его на выход разрешения, сбрасывая тем самым триггер 9 в нулевое состояние. После этого на адресную шину 17 выставляется адрес записи в память, формируемый блоком 10 (при этом старшие разряды вьщают- ся по входам-выходам данных блока 10 и по стробу адреса записываются в регистр 11), и через шииньш формирователь 12 на ширину данных 16 вьщается бай, имеющийся в регистре 1.

; Появление в регистре 1 следующего байта (переполнение счетчика 7) вызывает повторение описанной процедуры, при этом блок 10 модифицирует адрес до тех пор, пока не будет введена в память вся принимаемая кодовая последовательность.

5

0

5

0

5

0

5

0

Пусть теперь в очередном байте, поступившем в регистр 1, имеется ошибка: несовпадение стартового или стопового битов с заданными значениями (нулевым и единичным соответственно) или проверка нечетности,осуществляемая узлом 6, даст отрицательный результат. Тогда на выходе дешифратора 4 к моменту появления сигнала переполнения счетчика 7 сохранится сигнал О в результате чего в триггере 9 сохранится нулевое состояние, а триггер 8 перейдет в нулевое - состояние, вызвав тем самым сброс и блокировку дальнейшего счета счетчика 7. Таким образом будет прервана запись кодовой последовательности в память при обнаружении ошибки хотя бы в одном из ее байтов. После этого обнаружение синхробайта вновь вызывает прерывание и процессор снова инициирует ввод по прямому доступу в память принимаемой кодовой последовательности .

Если, например, noMeJoi, имеющие место в канале передачи данных, будут интерпретированы как синхробайт, что, очевидно, инициирует прием ложной кодовой последовательности, то как только в этой последовательности будет обнаружена ошибка, ее прием будет прекращен, а настояш 1й синхробайт независимо от этого инициирует прием настоящей кодовой последовательности, поскольку появление синхробайта в середиие правильной кодовой последовательности невозможно.

Формула изобретения

Устройство для сопряжения ЭВМ с каналом связи, содержащее делитель частоты, выходом подключенный к син- хровходу преобразователя последовательного кода в параллельный, информационный вход которого соединен с входом формирователя импульса и является входом устройства для подключения к информационному выходу канала связи, а выход соединен с информационным входом шинного формирователя, выход которого соединен с входом-выходом устройства для подключения к шине данных ЭВМ, дешифратор синхробайта, буферный регистр, два триггера и счетчик импульсов, причем выход формирователя импульсов соединен с входом сброса делителя

частоты, о.тличающеес. я тем, что, с целью повышения пропускной способности устройства, в него введены дешифратор формата, блок прямого доступа к памяти и узел контроля по модулю, причем информационный вход узла контроля по модулю соединен с выходом преобразователя последовательного кода в параллельный и с информационными входами дешифратора формата и синхробайта, синхронизирующие и разрешающие входы которых подключены соответственно к выходам делителя частоты и узла контроля по модулю, счетный вход делителя частоты является входом устройства для подключения к синхронизирующему выходу канала связи и соединен со счетным входой счетчика импульсов, выходом подключенного к синхровходам первого и второго триггеров, а входом сброса - к выходу первого триггера, входы сброса и установки которого соединены соответственно с входом начальной установки

устройства и инверсным выходом дешифратора синхробайта, прямой вход которого является выходом устройства для подключения к входу запроса прерывания ЭВМ, выход дешифратора формата соединен с информационными входами первого и второго триггеров, выход и вход сброса которого соеди0 йены соответственно с входом запроса и выходом разрешения блока прямого доступа к памяти, синхронизирующий, адресньш и информационный входы-выходы которого соединены с соот5 ветствующими входами-выходами устройства для подключения к шинам управления, адреса и данных ЭВМ, информационный вход, синхровход и вькод буферного регистра соединены соответ0 ственно с информационным входом-выходом, синхровходом старшего байтй адреса и адресным входом-выходом блока прямого доступа к памяти, выход разрешения записи которого соединен с

5 управляющим входом шинного формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналом связи | 1989 |

|

SU1656546A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство ввода-вывода информации | 1988 |

|

SU1619283A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

Изобретение относится к вычислительной технике может быть использовано в системах передачи данных. С целью повышения пропускной способности в устройство для сопряжения ЭВМ с каналом связи, содержащее преобразователь последовательного кода в параллельный, делитель частоты, формировательимпульсов, дешифратор синхробайта, счетчик импульсов, два триггера, буферный регистр и шинный формирователь, введены узел контроля, блок прямого доступа к памяти и дешифратор формата. 2 ил.

фиеЛ

./v.)(xxxy xxDoocr

Pue-Z

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1983 |

|

SU1160426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1987-09-14—Подача