Изобретение относится к вычислительной технике и может найти применение при создании специализированных и универсальных одно- и многопроцессорных высокопроизводительиых цифровых вычислительных машин.

Известен микропрограммный процессор, в котором переход в режим прерывания и возврат из него осуществляется в основном програкмными или микропрограммными методами ГИ.

Недостатком данного процессора является снижение быстродействия процессора с микропрограммным управлением при обработке прерываний.

Наиболее близким к предлагаемому является микропрограммный процессор, содержащий операционный .блок, соединенный двусторонней связью с оперативной памятью, выходы которой и стековой памяти соединены с первым входом блока микропрограммного управления, выход которого соединен с входом постоянной памяти, выход которой соединен с первым входом дешифратора микрокоманд, первый выход которого соединен с входом оперативной памяти и первым входом стековой памяти, второй выход дешифратора микрокоманд соединен с

вторым входом блока микропрограммного управления, третий выход дешифратора микрокоманд соединён с входе операционного блока, выход которого срединен с третьим входом блока микропрограммного управления, четвертый вход которого соединен с первым выходом первого коммутатора, первый вход которого соединен с

10 первым выходом триггера, первый вход которого соединен с четвертым выходом дешифратора микрокоманд, приоритетный шифратор, второЯ коммутатор, два регистра, дешифратор (2.

15

Однако в известном процессоре процедуры обработки прерываний осуществляются на уровне микропрргрецим. Наибольшие временные затраты необ20ходимы для запоминания состояния прерванной микропрограмма, определяемого содержимым эпемвнгов памяти блока микропрограммного управления , а именую регистра микропрог25раммного адреса и триггеров признаков результата. Вследствие этого, такой процесс перехода в режим прерывания и возврат из него снижает быстродействие- микропрограммного

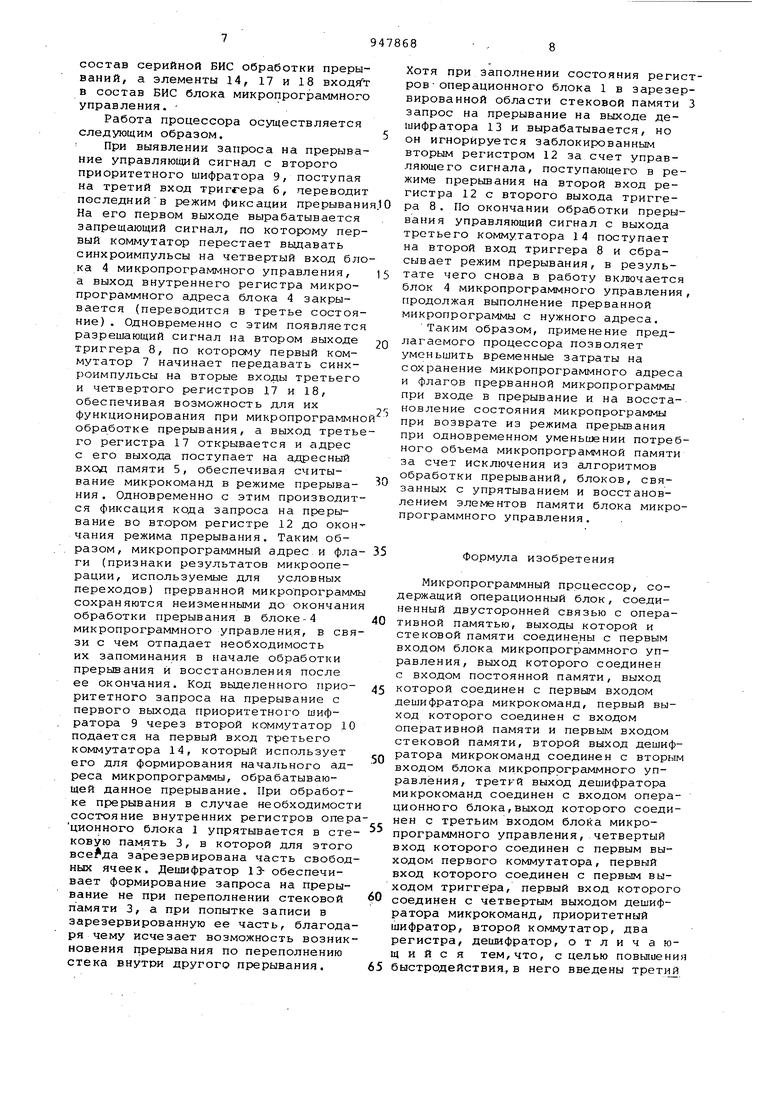

30 процессора. Цель изобретения - повьпяение быстродействия микропрограммного процессора за счет уменьшения времени перехода в режим прерывания и возврата из него. .. Поставленная цель достигается .тем, что в микропрограммный процессор, содержащий операционный блок, .соединенный двусторонней связью с оперативной памятью, выходы которой и стековой памяти соединены с первым входом блока микропрограммного управления, выход которого соединен с входом постоянной памяти, выход которой соединен с первым входом дешифратора микрокоманд, первый выход которого соединен с входом оперативной памяти и первым входом стековой памяти, второй выход дешифратора микрокоманд соединен с вторым входом блока микропрограммного управления, третий выход дешифратора микрокоманд соединен с входом операционного блока, выход которого соединен с третьим входом блока микропрограммного управления четвертый вход которого соединен с первым выходом первого коммутатора первый вход которого соединен с первым выходом триггера, первый вхо которого соединен с четвертым выходом дешифратора микрокоманд, приоритетный шифратор, второй коммутатор, два регистра, дешифратор, введены третий коммутатор, четвертый коммутатор, счетчик, третий и четвертый регистры, причем первый выхо дешифратора микрокоманд соединен с входом счетчика и с первыми входами первого регистра, дешифратора и вто рого коммутатора, выход которого соединен с вторым входом первого регистра, выход которого соединен с входом четвертого коммутатора, чере который вход -процессора соединен с первьм входом второго регистра, выход которого соединен с первым вход приоритетного шифратора, второй вхо которого соединен с пятым выходом д шифратора микрокоманд, второй выход которого соединен с первым входом третьего регистра, соединенного дву сторонней связью с третьим коммутатором, выход которого соединен с вторым входом триггера, первый выхо которого соединен с вторым входом дешифратора микрокоманд и пятым вхо домблока микропрограммного управления--, выходы второго коммутатора, стековойпамяти и оперативной памят соединены с первым входом третьего коммутатора и вторым входом операционного блока, выход которого сое динен с,первым входом четвертого ре гистра, выход которого соединен с вторым входом третьего коммутатора второй выход первого коммутатора соединен с5 вторыми входами третьего и четвертого регистров, второй выход триггера соединен с вторыми входами первого коммутатора и второго регистра и с третьим входом третьего регистра, выход которого соединен с входом постоянной памяти,выход счетчика соединен с вторыми входами стековой памяти и дешифратора, выход которого соединен с третьим входом второго регистра, выходы приоритетного шифратора соединены соответс;гвенно с вторым входом второго коммутатора и с третьим входсм триггера. Предлагаемый процессор позволяет избежать временных затрат на сохранение и восстановление значения текущего микропрограммного адреса, признаков результата микроопераций, определяющих состояние прерванной микропрограммы, что повыиает его быстродействие при обработке прерываний и способствует уменьшению объема микропрограммной памяти для хранения микропрограмм обработки прерываний, вследствие сокращения их длины. На чертеже изображена блок-схема микропрограммного процессора,одна из возможных реализаций. Процессор содержит операционный блок 1, оперативную память 2, стековую память 3, блок 4 микропрограммного управления, постоянную память 5, дешифратор 6 микрокоманд, первый коммутатор 7, триггер 8, приоритетный шифратор 9, второй коммутатор 10, первый регистр И, второй регистр 12, дешифратор 13, третий кот мутатор 14, четвертый коммутатор 15, счетчик 16, третий регистр 17, четвертый регистр 18. Операционный блок 1, обеспечивающий арифметическую обработку информации и содержащий регистр результата, регистр адреса и ряд регистров общего назначения, имеет возможность адресовать через двусторонние связь оперативную память 2 и записывать в адресуемые ее ячейки данные с вьлхода регистра результата, являющегося одним из выходов операционного блока 1. Кроме того, выход регистра результата блока 1 связан с информационным входом стековой памяти 3 (не показана), которая обеспечивает хранение данных, а также состояния регистров блока 1 при обработке прерывания. С другого выхода блока 1 признак результата микрооперации поступает на третий вход блока 4 микропрограммного управления и первый вход четвертого регистра 18 для запоминания в качестве условий для выполнения условных переходов в микропрограмме. На первый вход бло, ка 1 с третьего выхода дешифратора 6 микрокоманд поступает код микрооперации, которая выполняется над данными, хранящимися во внутренних регистрах операционного блока 1, а также над данными, поступающими с выходов стековой и оперативной памяти 3 и 2 на второй вход блока 1. Блок 4 микропрограммного управления обеспечивает выработку последовательнэсти адресов микрокоманд при выполнении рабочих микропрограмм в основном режиме с учетом или без учета признаков результатов микроопераций, выполненных блоком 1. Блок 4 содержит регистр микропрограммного адреса, коммутатор адреса и триггеры признаков результатов, обеспечивающих их запоминание. Код адреса следукадей микрокоманды, считываемый из постоянной памяти 5, поступает на второй вход блока 4 и на первый вход третьего регистра 17 со второго выхода дешифратора 6 микрокоманд. На первый вход блока 4 с выходов стековой и оперативной памяти 3 и 2 подается начальный микропрограммы. Вход постоянной памяти 5, предназначенной для хранения микропрограмм, является адресным и соединен с выходами блока 4 и третьего регистра 17. Считываемая микрокоманда с выхода памяти 5 поступает на первый вход дешифратора 6 микрокоманд, который предназначен для декодирования отдельных полей микрокоманды и выработки управляющих микроопераций, поступающих с выходов дешифратора 6 на остальные элементы процессора. С первого выхода дешифратора 6 управляющие сигналы поступают на первые входы стековой памяти 3, первого регистра 11, второго коммутатора 10, дешифратора 13, на входы оперативной памяти 2 и счетчика 16, обеспечивая управление этими элементами процессора. С пятого выхода дешифратора б микрокоманд управляющий сигнал поступает на второй вход приоритетного шифратора 9, разрешая выдачу управляющего сигнала на его второй выход. Первый коммутатор 7 обеспечивает выдачу синхронизирующих тактовых импульсов либо на четвертый вход блока 4 со своего первого выхода в основном режиме, либо на вторые входы третьего и четвертого регистро1В со своего второго выхода в режиме прерывания. Тактовые синхроимпульсы поступают на вход первого коммутатора, также как и на синхронизирующие входы других элементов процессора с выхода генератора синхросигналов (не показан). Состояние триггера 8 определяет режим работы процессора.

Управляющий сигнал поступает либо с первого выхода триггера 8 на

первый вход первого коммутатора 1, на второй вхац дешифратора 6 микрокоманд и пятый вход блока 4 микропрограммного управления в основном режиме работы, либо с второго выхода, триггера 8 на вторые входы первого коммутатора 7 и второго регистра 12 и третий вход -третьего регистра в режиме прерывания. Приоритетный шифратор 9 предназначендля выделения самого приоритетного запроса на прерывание и формирование его кода, который с первого выхода поступает на второй вход второго коммутатора 10. Управляющий сигнал с второго выхода приоритетного шифратора 9 подается на третий вход триггера 8, обеспечивающего фиксацию режима прерывания. Второй коммутатор 10 обеспечивает выдачу кода выделенного запроса на прерывание на первый вход третьего коммутатора 14. Первый регистр 11 предназначен для хранения статуса прерывания, разрешенного к обработке. Код статуса прерывания поступает на второй вход первого регистра 11 с выхода оперативной памяти 2. Второй регистр 12 обеспечивает фиксацию запросов на прерывание, поступающих на первый вход с выхода четвертого коммутатора 15 и на третий вход с выхода дешифратора 13. Выход второго регистра 12 соединен с первым входом приоритетного шифратора 9. Дешифратор 13 обеспечивает формирование запроса на прерывание при частично заполненном стеке. На второй вход дешифратора 13 и второй вход стековой памяти 3 подается адрес с выхода счетчика 16, предназначенного для формирования (указателя свободной ячейки стековой памяти 3. Четвертый коммутатор 15 обеспечивает выделение тех запросов на прерывание, поступающих с входа процессора, статус КОТОЕЖЛХ выше статуса, поступающего с выхода первого регистра 11 на управляющий вход четвертого коммутатора 15. Третий коммутатор 14 обеспечивает выбор кода адреса с учетом или без учета условий, поступающих с выхода чет0вертого регистра 16, обеспечивающего запоминание признаков результатов микроопераций, выполняемых операционным блоком 1. Третий коммутатор 14 связан двусторонней связью с третьим регистром 17. Управляющий сигнал конца обработки прерывания с вь1хода третьего коммутатора 14 поступает на второй вход триггера 8.Третий регистр 17 обеспечивает формирование адреса следующей микрокоман:Ды в режиме прерывания. Следует отметить, что структура предлагаемого процессора ориентирована на использование микропроцессорных БИС, напри5мер элементы 9-12 и 15, входят в состав серийной БИС обработки прерываний, а элементы 14, 17 и 18 входяГт в состав БИС блока микропрограммного управления. Работа процессора осуществляется следующим образом. При выявлении запроса на прерывание управляющий сигнал с второго приоритетного шифратора 9, поступая на третий вход триггера 6, переводит последнийв режим фиксации прерывани На его первом выходе вырабатывается запрещающий сигнал, по которому первый коммутатор перестает выдавать синхроимпульсы на четвертый вход бло ка 4 микропрограммного управления, а выход внутреннего регистра микропрограммного адреса блока 4 закрывается (переводится в третье состояние) . Одновременно с этим появляется разрешающий сигнал на втором выходе триггера 8, по которому первый коммутатор 7 начинает передавать синх1:)оимпульсы на вторые входы третьего и четвертого регистров 17 и 18, обеспечивая возможность для их функционирования при микропрограммн обработке прерывания, а выход треть го регистра 17 открывается и адрес с его выхода поступает на адресный вход памяти 5, обеспечивая считывание микрокоманд в режиме прерыва ния. Одновременно с этим производит ся фиксация кода запроса на прерывание во втором регистре 12 до окон чания режима прерывания. Таким образом, микропрограммный адрес и фла ги (признаки результатов микрооперации, используемые для условных переходов) прерванной микропрограмм сохраняются неизменными до окончани обработки прерывания в блоке - 4 микропрограммного управления, в свя зи с чем отпадает необходимость их запоминания в вшчале обработки прерывания и восстановления после ее окончания. Код выделенного приоритетного запроса на прерывание с первого выхода приоритетного шифратора 9 через второй коммутатор 10 подается на первый вход третьего коммутатора 14, который использует его для формирования начального адреса микропрограммы, обрабатывающей данное прерывание. При обработке прерывания в случае необходимост состояние внутренних регистров опер ционного блока 1 упрятывается в сте ковую память 3, в которой для этого всегда зарезервирована часть свобод Htjx ячеек. Дешифратор 13- обеспечивает формирование запроса на прерывание не при переполнении стековой памяти 3, а при попытке записи в зарезервированную ее часть, благода ря чему исчезает возможность возник новения прерывания по переполнению стека внутри другого прерывания. Хотя при заполнении состояния регистров операционного блока 1 в зарезервированной области стековой памяти 3 запрос на прерывание на выходе дешифратора 13 и вырабатывается, но он игнорируется заблокированным вторым регистром 12 за счет управляющего сигнала, поступающего в режиме прерывания на второй вход регистра 12 с второго выхода триггера 8. По окончании обработки прерывания управляющий сигнал с выхода третьего коммутатора 14 поступает на второй вход триггера 8 и сбрасывает режим прерывания, в результате чего снова в работу включается блок 4 микропрограммного управления, продолжая выполнение прерванной микропрограммы с нужного адреса, Таким образом, применение предлагаемого процессора позволяет уменьшить временные затраты на сохранение микропрограммного адреса и флагов прерванной микропрограммы при входе в прерывание и на восстановление состояния микропрограммы при возврате из режима прерывания при одновременном уменьЕиении потребного объема микропрограммной памяти за счет исключения из алгоритмов обработки прерываний, блоков, связанных с упрятыванием и восстановлением элементов памяти блока микропрограммного управления. Формула изобретения Микропрограммный процессор, содержащий операционный блок, соединенный двусторонней связью с оперативной памятью, выходы которой и стековой памяти соединены с первым входом блока микропрограммного управления, выход которого соединен с входом постоянной памяти, выход которой соединен с первым входом дешифратора микрокоманд, первый выход которого соединен с входом оперативной памяти и первым входом стековой памяти, второй выход дешифратора микрокоманд соединен с вторым входом блока микропрограммного управления, треткй выход дешифратора микрокоманд соединен с входом операционного блока,выход которого соединен с третьим входом блока микропрограммного управления, четвертый вход которого соединен с первым выходом первого коммутатора, первый вход которого соединен с первым выходом триггера, первый вход которого соединен с четвертым выходом дешифратора микрокоманд, приоритетный шифратор, второй коммутатор, два регистра, дешифратор, отличающийся тем, что, с целью повьлиения быстродействия, в него введены TpeTiij

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

Авторы

Даты

1982-07-30—Публикация

1980-10-23—Подача