соеоинен с вторым управляющим вхоаом блока, а прямой и инверсный выходы с вторым и первым выхоцами блока соот

ветственно, первый уп| вляюший вхоа блока соеаинен с управляющим вхоаом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

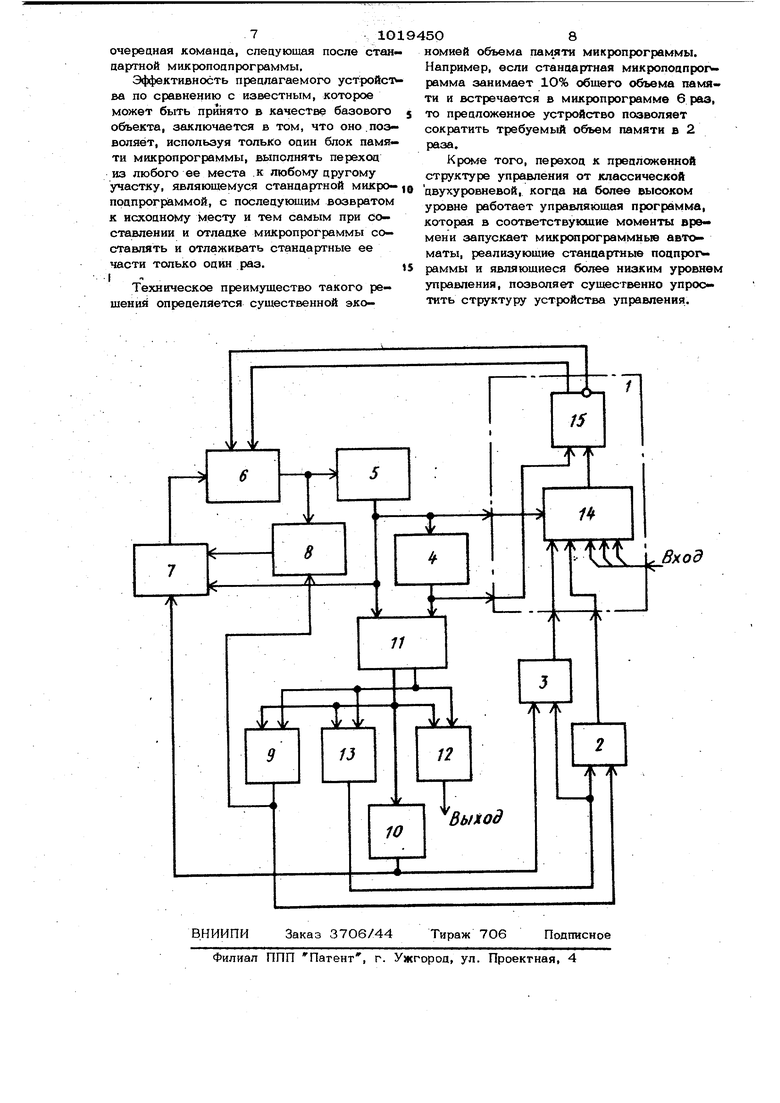

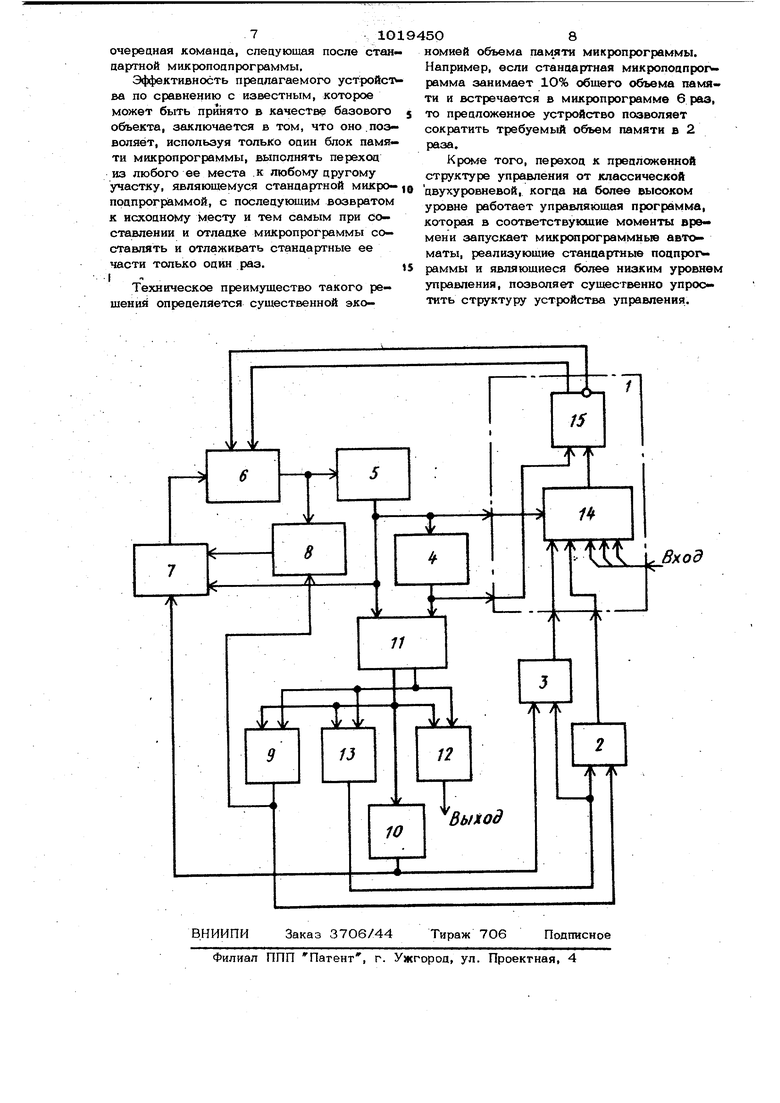

1. МИКРОПРОГРАММНСЕ УСТРОЙСТВО УПРАВЛЕНИЯ, сопержащее блок па:мяти микропрограмм, выхоц которого соединен с первым информационным вхоцом регистра микрокомана, блок проверки условий, первый информационный ахоц которого соецинен с выхоцом триггера перехода, установочный вхоа которого соецинен с выходом дешифратор команды перехода, регистр адреса возврата, отличающееся тем, что, с целью сокращения оборудования, оно содермсит счетчик адреса, коммутатор, триггер возврата, цещнфр(аторы микроопераций, признака условного перехода, команды послеврзвратных операций и команды возврата, причем выход дешифратора команд послевоавратных операций соединен с входами сброса триггеров перехода и возврата, выход последнего подключен к второму информационному нхоцу блока проверки условий, первый и второй выходы которого подключены соответственно к счетному и установочному входам счетчика адреса, выход которого соецинен с информационным входом регистра адреса возврата и адресным входом блока памяти возврата и адресным входом блока памяти микропрограмм, выход .которого соединен с первым управляющим входом блока проверки условий, с первым информационным входом коммутатора и с входом дешифратора пряэна са условного перехода, выход которого соединен с BTOf,iM управляющим вхоаом блока проверки условий и с вторым информационным ВХОДСЖ1 регистра микрЕжоманц, первый выход которого соединен с информационными входами аешифраторсш команды перехода, команды nocqeBoaapaiw ных операций, команды возврата и микроопераций, второй выхоц - с управляющими входами дешифраторов команды перехода, послевозвратных операций и микроопераций, выход последнего соединен с операционным выходом устройства, выхос) дешифратора команды возврата соединен с установочным входом триггера возврата и с управляющим входом коммутатора, выход которого соединен с информацнсж- ным входом счетчика адреса, а второй инфо Ж1ационный вход соединен с выходом регистра адреса возврата, управляющий вход которого соединен с выходом дешнф-. СО ратора команды перехода, третий инфор и ел мационный вход блока проверки условий соединен с входом устройства. 2. Устройство по п. 1, отличающееся тем, что блок прюверки условий содерисит коммутатор и элемент И, причем первый, второй и третий инфор мационные входы блока соединены соответственно с первым, вторым и третьим информационным входами коммутатора, выход которого соединен с первым входом элемента И, второй вход которого

Изобретение относится к автоматике и вычислительной технике и может бьггь использовано в специализированных про цессах.

Известно микропрограммное устройств. во управления, соцержашее соециненные в кольцо первый регистр ацреса, первый блок памяти, первый блок проверки , второй регистр адреса, группу элементов И, второй блок памяти, вторс блок проверки условий, причем вхоа запи си устройства подключен к входу записи первого регистра непосредственно, а с входом записи второго регистра связан через элемент И, подключенный к управляющему и установочным входам устройства. Управляющий вход устройства под- ключей при этом к входам группы элементов И. В этом устройстве поочередно работают первый и вторсЛ блоки памяти, выходы которых подключены к выходу устройства, а блоки пр юеркн условий поочередно формируют сигналы для записи в соответствующие регистры адреса. При поступлении управляющего сигнала на

установочный вход устройства элемент И запирается и во второй регистр адреса новый сигнал не записывается. Выполнение микропрограммы прёрьюается, а во втором регистре адреса сохраняется значение адреса, на котором прервалось вьшолнение микропрограммы. При поступи лении управляющего сигнала на управлякядий вход ycTpcdtcTBa адресный сигнал, хранящийся ёо втором регистре адреса, поступает через группу элементов И на второй блок памяти, и выполнение микропрограммы возобновляется с того места, где оно прервалось .l3 .

Недостатком этого устройства являетс то, что при прерывании исполнения микропрограммы выклюяается из работы весь блок памяти, поэтому невозможно органи. зовать в таком устройстве прерывание микропрограммы и переход к вьшолнению ее часто встречающейся части стандартной микроподпрограммы - хранящейся в

том же блоке памяти, что и микропрограм ма, и последукяций возврат к вьтолнению микропрограммы. Указанный недостаток вызьшает необходимость многократно повторять в микропрограмме станда1зтные части, что усложняет процесс составления и отладки микропрограммы и увеличивает требуемый объем памяти.

Наиболее близким к. предлагаемому по технической сущности и достигаемому результату является устройство, содержащее соединенные в кольцо первый блок памяти микропрограммы, регистр микрокоманд и счетчик адреса, второй вход .; которого через блок э юментов И, тригj«p и дёщифратор связан с операционным входом устройства, выход регистра микрокоманд является выходом микроопераций устройства, а другой его выход подключен к модификатору адреса, второй вход которого через регистр входного адреса связан с адресным входом устройства, а выход является адресным выходом устрой ства, который при подключается к второму блоку памяти микропрограммы, выход которого через блок Проверки условий подк.лючается к регистру входного адреса, а второй выход - к операционному входу устройства. При этом выбор во втором блоке памяти микропрограммы команды обращения к микропрограммному устройству управления вызьшает срабатывание дещифратора и триггера и поступление сигнала с операционного входа уст ройства через блок элементов И в регистр адреса. Одновременно в регистре входного адреса запоминается адрес команды, в которой происходит обращение к микропрограммному устройству управления. Далее микропрограммное устройство управления выполняет свою микропрограмму путем последовательного перебора микрокоманд первого блока памяти микропрограммы и выдачи ш: в регистр микро команд, а в конце выполнения микропрог раммы и регистре мик|х команд вырабатывается сигнал, открь1вающий моцифи- катор ацреса. При этом сигнал регистра вхоцйого адреса через .моцификатор адреса поступает на второй блок памяти микропрограммы и выполнение мнкропрог раммы, записанной во втором блоке памя ти, проаолжается с того места, на котором оно прервалось f 2 . Таким образом, в известном устройст ве можно обращаться из любого места второго блока памяти к микропрограм1 1в, записанной в первом блоке памяти, которую можно считать стандартной микропоапрограммой, однако невозможно обратиться из первого блока памяти микропрограммы к некоторой ее части, являющейся стандартной мнкропоцпрограммой, с последующим возвратом в исходное место мшсропрограммы. Это вызывает необходимость многократного повторения в микропрограмме ее стандартных частей что усложняет прсинесс составления и отладки микропрограммы и увеличивает требуемый объем памяти. Сущность изобретения заключается в том, что при переходе к стандартной микроподпрограмм из произвольного места микропрограммы фиксируют это место в регистре адреса возврата и запоминают признак перехода к стандарт ной мнкроподпрограмме, в какие стандар ной микроподпрограммы анализируют признак перехода и при его наличии переписывают в счетчик адреса содержк мое регистра адреса возврата и запоминают признак возврата от стандартной микрсжодпрограммы, после возврата в исходное место микропрограммы аналиэируют признак возврата и при его нали чии стирают оба признака и продолжают выпоишеиие микропрограммы. Цель изобретения - сокращение обору дования. Поставленная цель дсютигается тем, что в MHKfiQnporpaMMHoe устройство упра ления, содержащее блок.памяти микропрограмм, выход которого соединен с первым информационным входом регистра мик.рокоманд, блок проверки условий, пе|шый информационный вход которого соединен с выходом триггера перехода, установочный вход которого соединен с выходом деиГифратора команды перехода, регистр адреса возврата, введены счепчик адреса, коммутатор, триггер возврата, дещифраторы микроопераций, признака условного перехода, команды после- возвратных операций и команды возврата причем выход дешифратора команд после возвратных операций соединен с входами броса триггеров перехода и возврата, ыход последнего подключен к второму нформационному входу блока проверки условий, первый и второй выходы которого подключены соответственно к счетному и установочному входам счетчика адреса, выход которого соединен с информационным входом регистра адреса возврата и адресным входом блока памяти микропрограмм, выход которого соединен с первым управляюцим входом блока проверки условий, с первым информацисшньсм входом коммутатора и с входом дешифратора признака условного перехода, выход которого соединен с вторым управляющим входом блока проверки условий и с вторым информационным входом регистра мик-рокоманд, первьШ выход которого соединен с информационными входами дешифраторов команды перехода, команды послевозвратных операций, команды возврата и микроопераций, второй выход - с управляющими входами дешифраторов команды перехода, послевозвратных операций и микроопераций, выход последнего соединен с операционным выходом устройства, выход дешифратора команды возврата соединен с установочным входом триггера возврата и с управляющим входом коммутатора, выход которого соединен с информационным входом счетчика адреса, а второй информационный вход соединен с выходом регистра адреса возврата, управляющий вход которого соединен с выходом дешифратора команды перехода, третий информационный вход блока проверки условий соединен с входом устройства. Блок, проверки условий содержит коммутатор и элемент И, причем первый, второй и третий информационные выходы блока соединены соответственно с первым, вторым и третьим информационными входами коммутатора, выход которого соединен с первым входом элемента И, второй вход которого соединен с вторым управля- кнцим входом блока, а прямой и инверсный выходы - с вторым и первым выходами блока соответственно, первый управляющий вход блока соединен с управляющим входом коммутатора. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит блок 1 проверки условий, триггер 2 перехода, триггер 3 возврата, дешифратор 4 признака условного перехода, блок 5 памяти микропрог рамм, счетчик 6 адреса, коммутатор 7, регистр 8 адреса возврата, дешифратор 9команды .перехоца, дешифратор Ю коман цы возврата, регистр 11 микрокомашц, аешифратор 12 мшсроопераций, цешифратор 13 команды послевозвратных операций. Блок 1 состоит из коммутатора 14 и элe feнтa И 15, Устройство действует следующим образонРабота устройства организована по микротактам. В каждом микротакте ац- рее, сформированный в счетчике 6 адреса, поступает на блок 5 памяти микропрогрфимы, из которого выбирается код очередной микрокоманды, который записы вается в регистр 11 микрокоманд, расшифровывается дешифратором 12 мщс операций, сигналы которого поступают на выход устройства. Одновременно сигнал кода очередной микрокоманды с выхода блока 5 памяти микропрограмм поступае на дешифратор 4 признака условного перехода. Если.в очередном коде микрокоманды закодирован условный переход, то на выходе дешифратора 4 формируется сигнал, приводящий в действие блок 1 проверки условий. Последний проверяет условие, HOKfep которого закодирован в очередной микрокоманде и поступает на его вход с блока 5 памяти микропрограм мы, а само условие поступает на один из его трех и формационных входов. В случае выполнения условия блок 1 формирует сигнал, поступающий на установочный вход счетчика 6 адреса, в котор)1й при этом записывается адрес условного перехода, закодированный в микрокоманде и поступающий на счетчик 6 адреса и блока S памяти микропрограммы через коммутатор 7, находящийся в своем основном состоянии. Таким образом, выпо няется условный переход. В случае, если проверяемое условие не выполнено или в очередной микрокоманде закодирована не команда условного перехода, блок 1 проверки условий вырабатывает управляющий сигнал на своем втором выходе, .поступающий на счетный вход счетчика б адреса, в котором к текущему адресу добавляется ещшица. Сигнал кода очередной микрокоманды с выхода регистра 11 поступает также на дешифраторы 9, 10 и 13, причем, в случае, если закодирована команда услов ного пер(зхоаа, то сигнал с выхода дешиф ратора 4 через второй вход регистра 11 микрокоманд поступает на его второй вы ход, откуца на запрещающие входы .дешифраторов 9, 12 и 13, предотвращая их ложное срабатывание. Если в очередной микрокоманде блока 5 памйти закодирована команда перехода к стандартной микроподпрограмме, то срабатывает дешифратор 9 перехода к стандартной микропрограмме, сигнал которого поступает на управляющий вход регистра 8 адреса возврата и записывает в него текущее значение адреса в счетчике 6, а также поступает на установочный вход триггера 2 признака перехода и устанавливает его в состояние хранения призн зка перехода. В следующей ячейке блока 5 памяти микропрограммы кодируется микрокоманда условного перехода в зависимости от состояния триггера 3 возврата. Вследствие того, что триггер 3 находится в исходном состоянии,- выполняется условный переход по адресу начала стандартной микроподпрограммы. В последующих микротактах выполняется стандартная микроподпрограмма, в конце которой кодируется команда условного перехода по условию триггера 2 перехода. Вследствие того, что триггер 2 установлен в-режим хргшения признака перехода, Бьиолняется лереход к команде возврата. При поступлении в регистр 11 микрокоманд команды возврата срабатывают дешифраторы 4 и 10. При этом сигналом дешифратора Ю коммутатор 7 переводится в режим проттускания сигнала от регистра 8 адреса возврата, триггер 3 устанавливается в режим хранения признака возврата, и выполняется безусловный переход по адресу регистра 8, После перехода к команде, адрес которой записан в регистре 8, эта команда повторяется, а после нее повторяется команда условного пере.хода по условию триггера 3 возврата. Вследствие того,, что триггер 3 установлен в режим хр«шения признака возврата, поворотный переход к стандартной микропоцпрограмме не происходит, а устройство выполняет команду послевозвратных операций, при поступлении кото- рой в регистр 11 микрокоманд срабатывает дешифратор 13, выходной сигнал которого устанавливает триггеры 2 и 3 в исходное состояние. Далее выполняется последующая часть микропрограммы. Если стандартная микроподпрограмма выполняется не после пере.хоца из произвольного места микропрограммы, а в порядке своей очереди, то в ее конце при выполнении команды условного перехода по условию триггера 2 перехода последний оказывается в исходном состоянии и поэтому переход к команде возврата не выполняетс:я, а выполняется

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройствоупРАВлЕНия | 1977 |

|

SU840904A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1979 |

|

SU826348A1 |

Авторы

Даты

1983-05-23—Публикация

1982-02-11—Подача