Изобретение относится к вычислительной технике и может использоваться при проектировании цифровых интегральных микросхем и электронных вы- числительных машин„

Цель изобретения - упрощение устройства

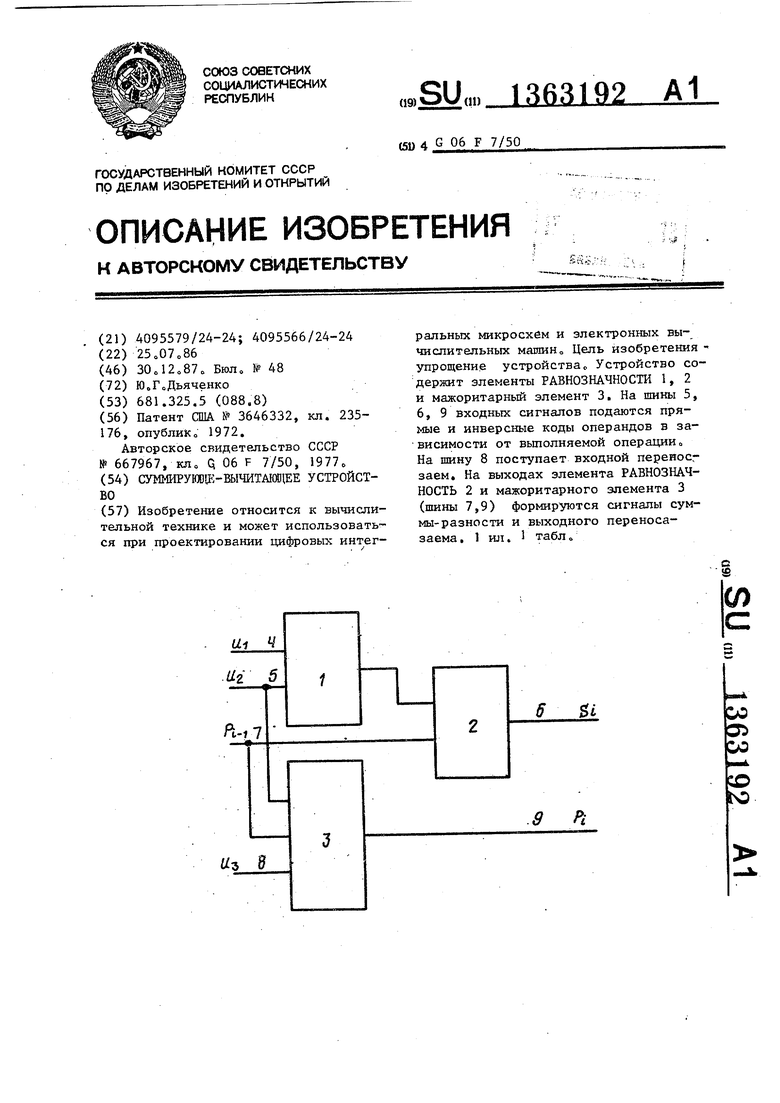

На чертеже представлена функциональная схема устройства

Устройство содержит элементы РАВНОЗНАЧНОСТЬ 1 и 2 и мажоритарный элемент 3, входы элемента РАВНОЗНАЧНОСТЬ 1 подключены к шинам А и 5 первого

лов.

и. и второго и,

входных сигнаа выход его - к первому входу элемента РАВНОЗНАЧНОСТЬ 2, выход которого соединен с шиной 6 выхода суммы-разности S; устройства, второй вход элемента РАВНОЗНАЧНОСТЬ 2 подключен к шине 7 входного переноса- заема Р и входу мажоритарного элемента 3, другие входы которого подключены соответственно к шинам 5 и 8 второго Uj и третьего U, входных сигналов устройства, а выход подключен к шине 9 выходного переноса-зае- ма устройства,

Схема устройства работает следующим образом

На входы 4 и 8 коммутируется прямой или инверсный код первого операнда (А;), а на вход 5 - прямой или инверсный код второго операнда (В;) в зависимости от выполняемой операции. В результате на выходе элемента РАВНОЗНАЧНОСТЬ 2 формируется значение суммы-разности (S ), а на выходе мажоритарного элемента 3 - значение сигнала выходного переноса- заема (Р. ),

Функция мажоритарного элемента 3 описывается формулой

М аЬ + с(а + Ь),

где а,Ь,с - входы мажоритарного элемента„

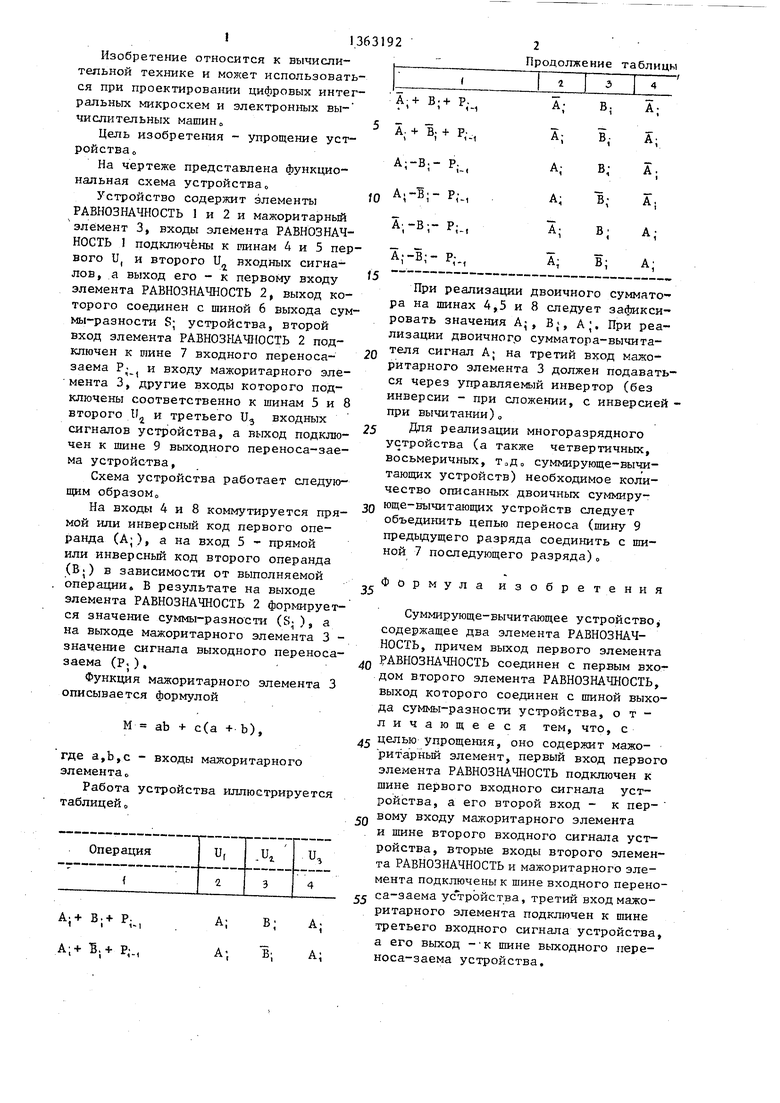

Работа устройства иллюстрируется таблицей о

Продолткение таблицы

5 Д 4. П

15

При реализации двоичного сумматора на шинах 4,5 и 8 следует зафиксировать значения А:, В

При реа

лизации двоичногр сумматора-вычита- теля сигнал А; на третий вход мажоритарного элемента 3 должен подаваться через управляемый инвертор (беэ инверсии - при сложении, с инверсией - при вычитании)о

Для реализации многоразрядного устройства (а также четвертичных, восьмеричных, ТоД суммирующе-вычи- тающих устройств) необходимое количество описанных двоичных суммиру- юще-вычитающих устройств следует объединить цепью переноса (шину 9 предыдущего разряда соединить с шиной 7 последующего разряда)о

Формула изобретения

Суммирующе-вычитающее устройство содержащее два элемента РАВНОЗНАЧНОСТЬ, причем выход первого элемента

РАВНОЗНАЧНОСТЬ соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с шиной выхода суммы-разности устройства, отличающееся тем, что, с

с целью упрощения, оно содержит мажо- ритарньш элемент, первый вход первого элемента РАВНОЗНАЧНОСТЬ подключен к шине первого входного сигнала устройства, а его второй вход - к пер- вому входу мажоритарного элемента и шине второго входного сигнала устройства, вторые входы второго элемента РАВНОЗНАЧНОСТЬ и мажоритарного элемента подключены к шине входного перено- са-заема ус трЬйства, третий вход мажоритарного элемента подключен к шине третьего входного сигнала устройства, а его выход - к шине выходного пере- носа-заема устройства.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Одноразрядный двоичный сумматор | 1987 |

|

SU1411736A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Арифметическое устройство | 1984 |

|

SU1290298A1 |

| Арифметическое устройство | 1989 |

|

SU1635172A1 |

| Устройство для вычитания | 1985 |

|

SU1277097A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

Изобретение относится к вычислительной технике и может использоваться при проектировании цифровых интегUi Ч Мг 5 ft-;7 Иъ В ральных микросхем и электронных вычислительных машино Цель изобретения - упрощение устройства„ Устройство со- держит элементы РАВНОЗНАЧНОСТИ 1, 2 и мажоритарный элемент 3. На шины 5, 6, 9 входных сигналов подаются прямые и инверсные коды операндов в зависимости от вьтолияемой операции На шину 8 поступает входной переносг заем. На выходах элемента РАВНОЗНАЧНОСТЬ 2 и мажоритарного элемента 3 (шины 7,9) формируются сигналы суммы-разности и выходного переноса- заема, 1 ил. 5 табл. Si 00 о: со .ff Pi ю

| Патент США № 3646332, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-25—Подача