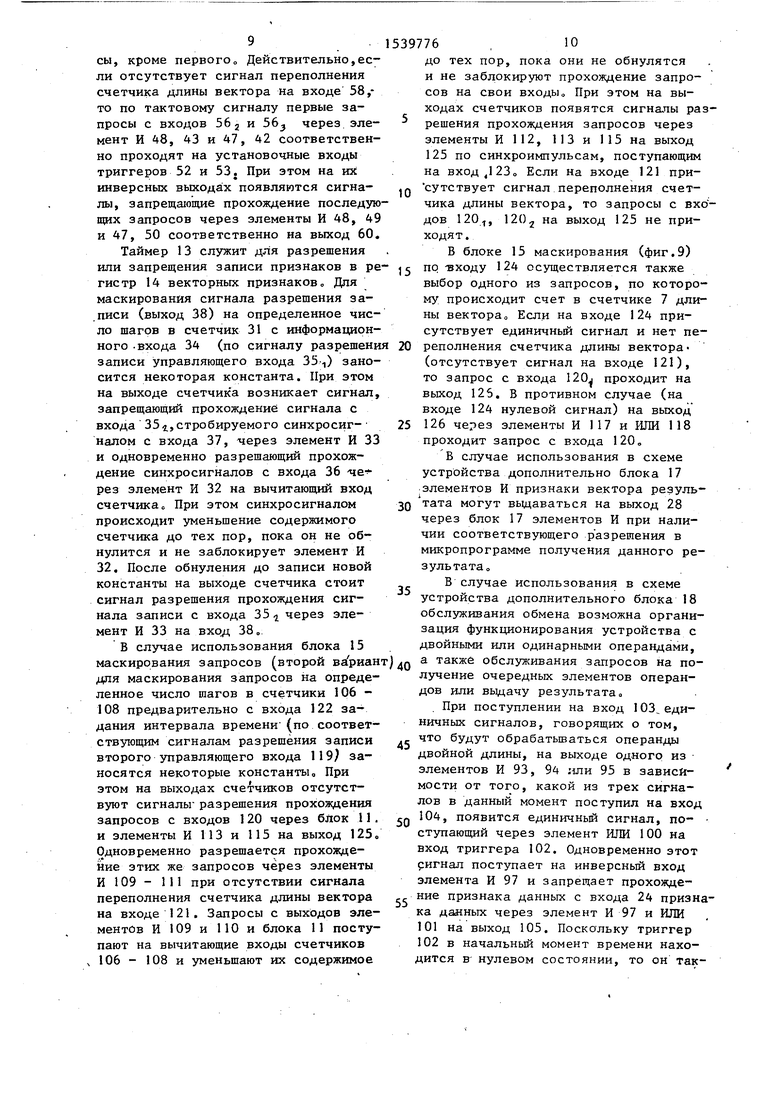

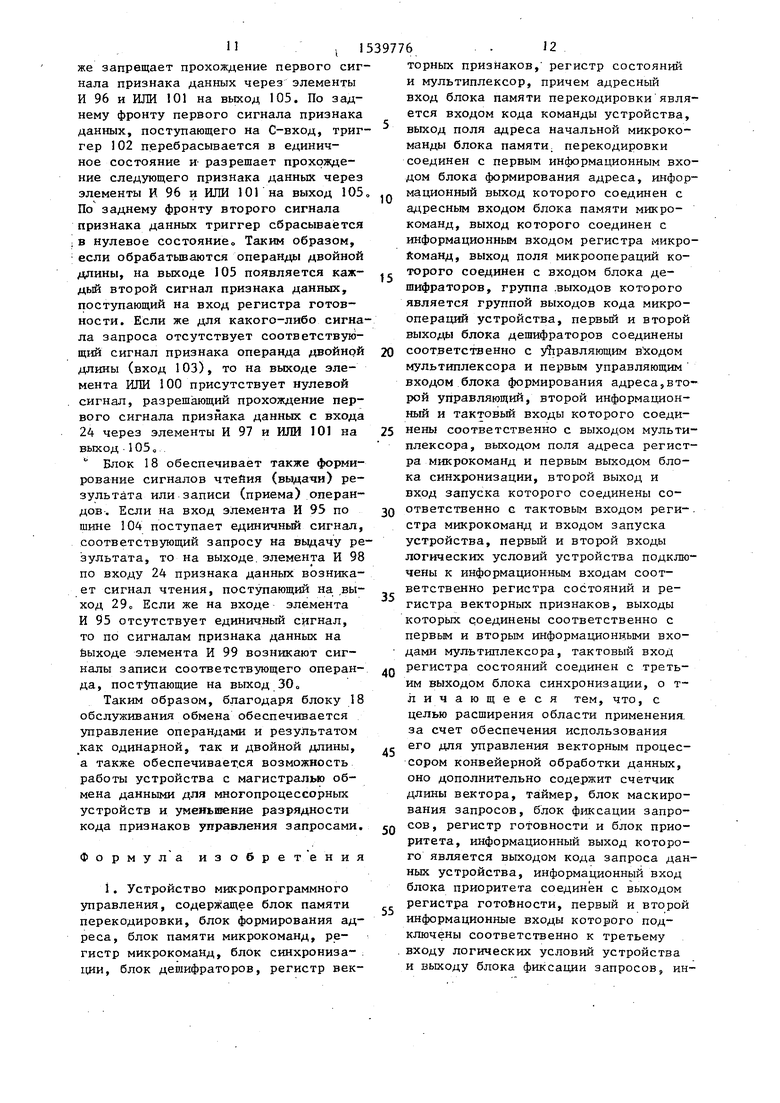

манд, блок 4 дешифраторов, блок 5 синхронизации, регистр 6 состояния, счетчик 7 длины вектора, мультиплексор 8, блок 9 приоритета, блок 10 фиксации запросов, блок 11 памяти перекодировки, вход 12 начальной установки устройства, таймер 13, регистр 14 векторных признаков, блок 15 маскирования запросов, регистр 16 готовности, блок 17 элементов И,/блок 18 обслуживания обмена, вход 19 кода команд, вход 20 кода задания длины вектора, первый 21 и второй 22 входы логических условий, вход 23 запуска, вход 24 признака данных, первая группа выходов 25 кода микроопераций, выход 26 кода запроса данных, вторая группа выходов 27 кода микроопераций, выход 28 векторных признаков, первый 29 и второй 30 выходы синхронизации запросов о

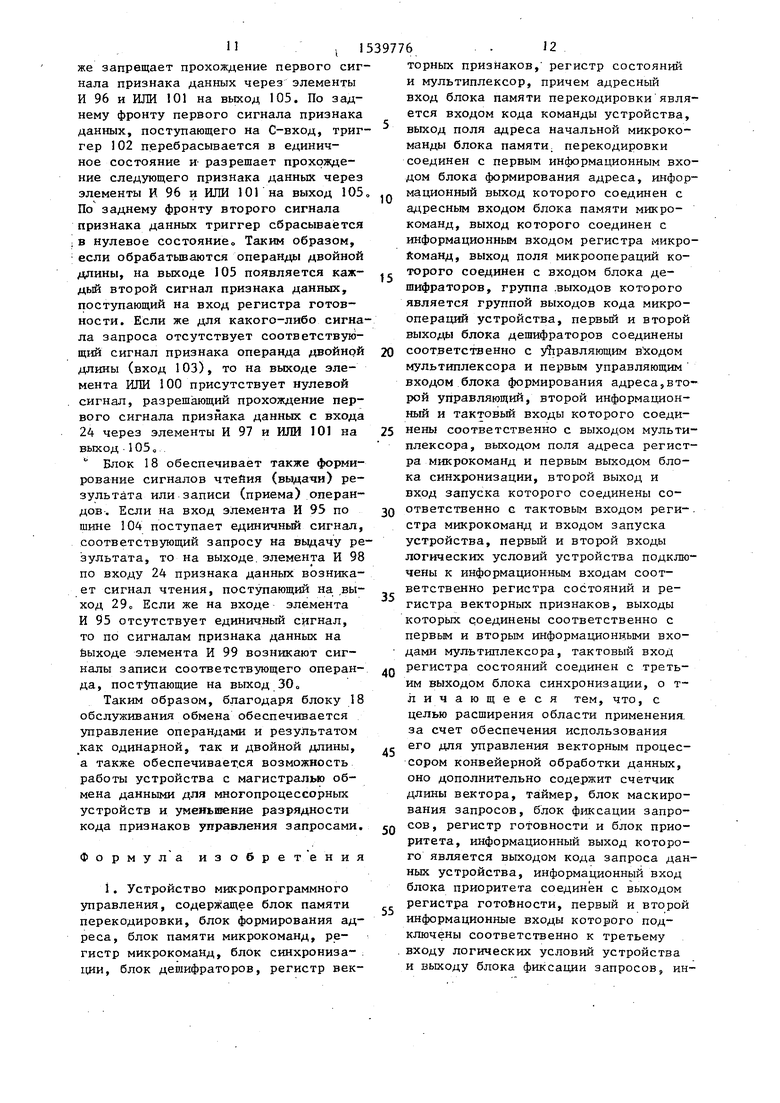

Таймер (фиг.2) содержит счетчик 31, два элемента И 32 и 33, информационный вход 34, группу управляющих входов 35, первый синхровход 36, второй синхровход 37 и выход 38.

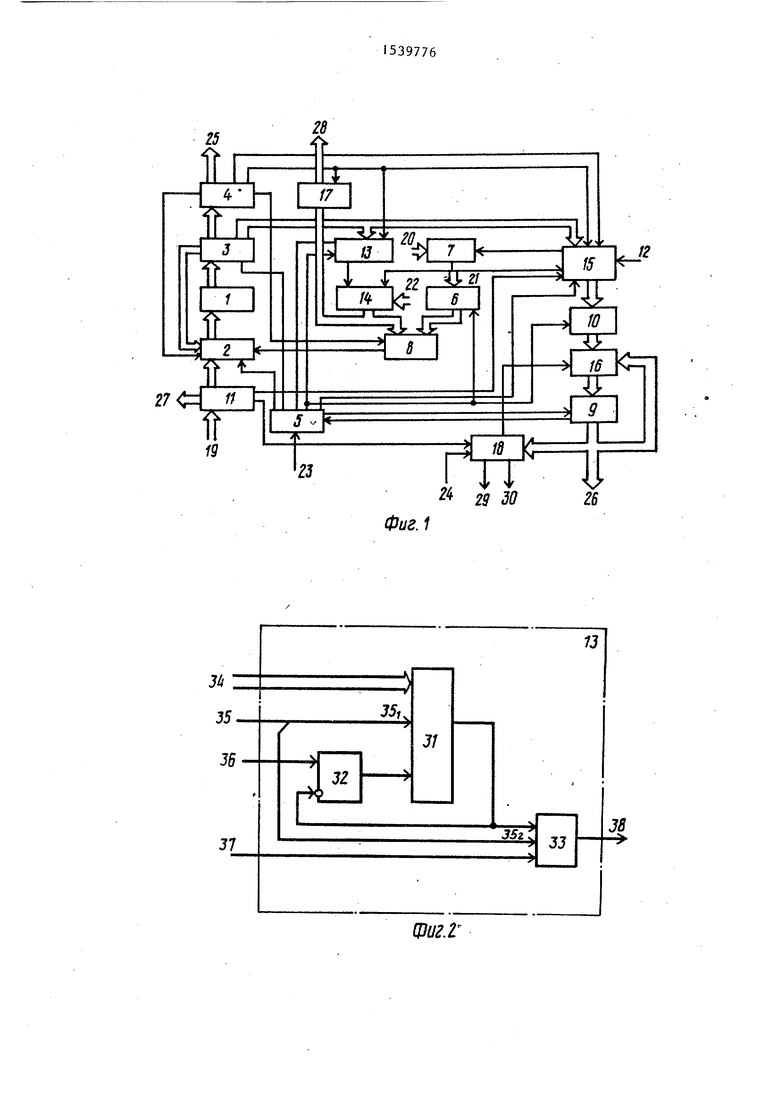

Блок 15 маскирования запросов (первый вариант) содержит (фиг.З) счетчик 39, одиннадцать элементов И 40-50, элемент ИЛИ 51, первый 52 и второй 53 триггеры, первый управляющий вход 54, три разряда 55,-55, входа настройки блока, тактовый вход

Микропрограмма предлагаемого устройства представляет собой микропрограмму конвейерной обработки данных, обеспечивающую выполнение арифметико-логической операции, заданной в команде (например, умножение двух чисел с плавающей точкой; поразрядное логическое умножение двух кодов). Микропрограмма конвейерной обработки данных - это микропрограмма, которая позволяет нести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда- массива для ударных команд), причем каждая из пар элементов находится в определенной фазе выполнения арифметико-логической операции Операция сложения двух чисел с плавающей точкой состоит из следующих фаз: анализ порядков; выравнивание порядков;

40

55, второй управляющий вход 56, вход

57 задания интервала времени, третий 35 СЛОжение; нормализация„ Микропрограм- управляющий вход 58, управляющий выход 59 и информационный выход 60.

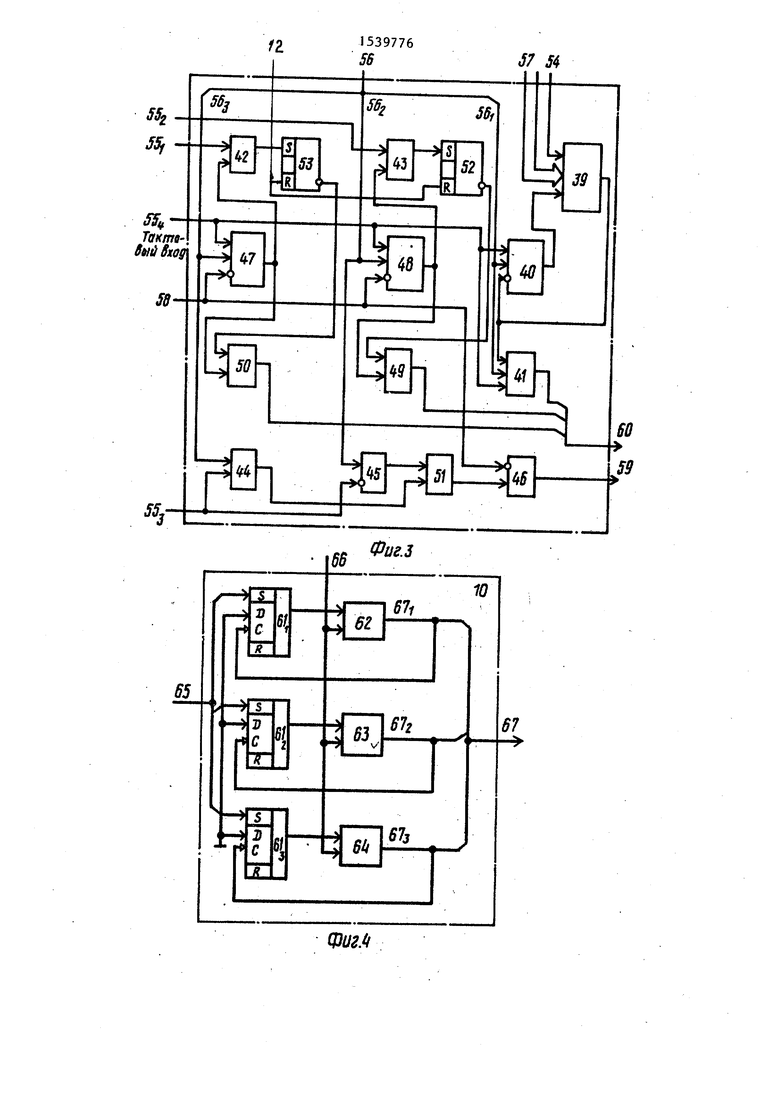

Блок 10 фиксации запросов (фиг.4) содержит регистр 61 и три элемента И 62-64, группу информационных входов 65, синхровход 66 и группу выходов 67.

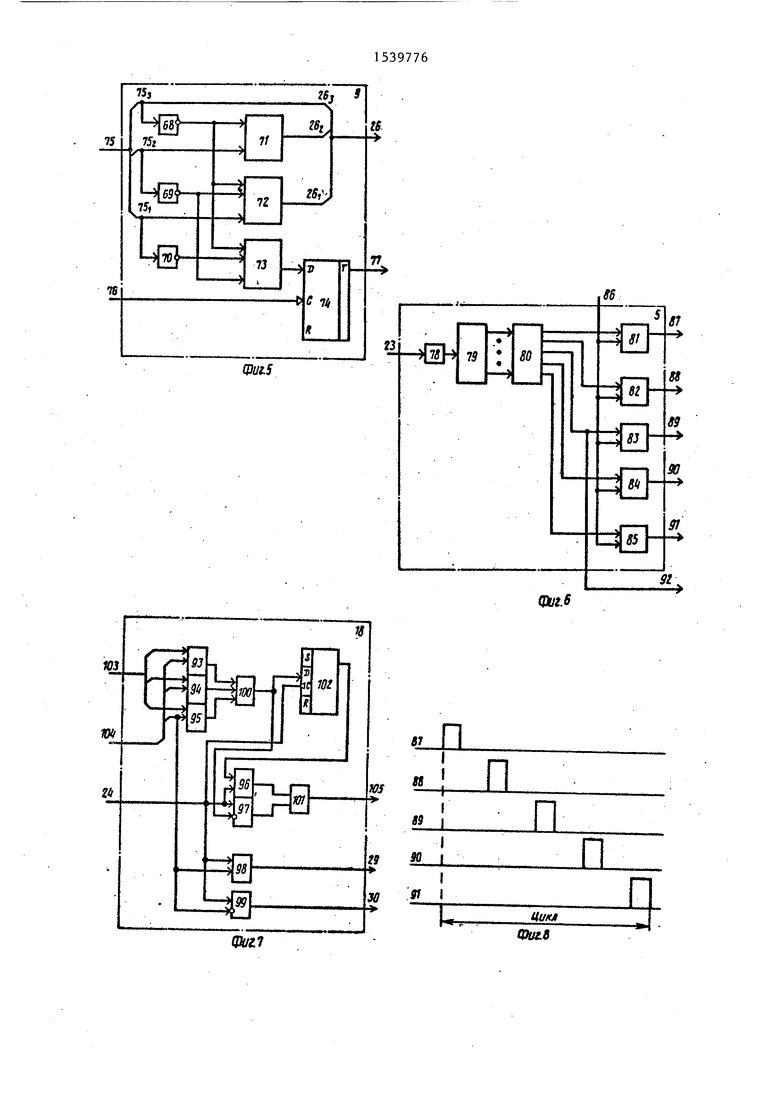

Блок 9 приоритета (фиг.5) содержит гри элемента ИЛИ 68-70, три элемента И 71-73, триггер 74, группу информационных входов 75, синхровход. 76, первый выход 77 и второй выход 26.

Блок 5 синхронизации (фиг.6) содержит вход 23 пуска устройства, так45

- 50

ма данной операции позволяет одновременно нормализовать сумму i-й пары чисел, суммировать i+1-ю пару чисел, выравнивать порядки у i+2-й пары чисел (например, i, i+1, i+2 - индексы трех расположенных подряд элементов векторов-операндов). Для организации конвейерного процесса обработки векторов-операндов в устройстве используются микрооперации запроса данных или запроса двойных данных,, Они предназначены для пересылки элемента массива операнда из ОЗУ либо для пересылки элемента массива результата выполнения векторной операции в ОЗУ.

-

товый генератор 78, счетчик 79, де шифратор 80, пять элементов И 81-85, управляющий вход 86, группу выходов 87-92.

Блок 18 обслуживания обмена (фиг.7) содержит семь элементов И 93 99, первый 100 и второй 101 элементы ИЛИ, триггер 102, управляющий вход 103, информационный вход 104, вход

10

15

539776д

24 признака данных, выход 105 модифицированного признака данных, первый 29 и второй 30 выходы синхронизации запросов о

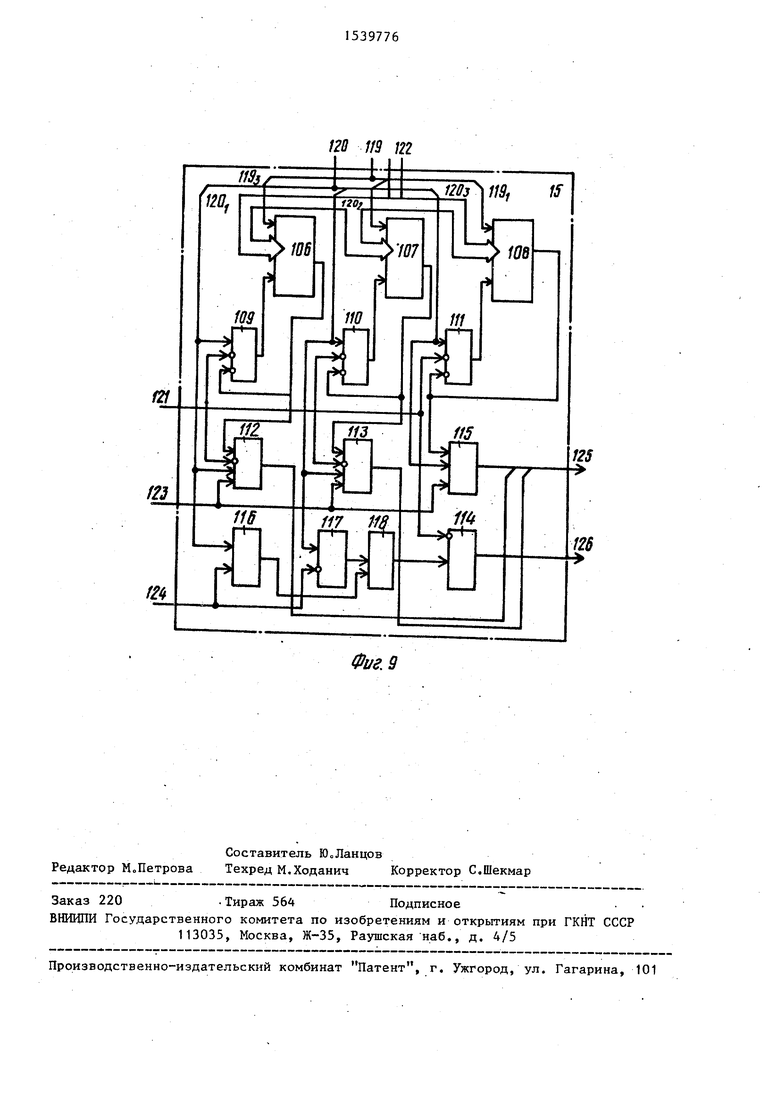

Блок 15 маскирования запросов (второй вариант) содержит (фиг„9) три счетчика 106 - 108, девять элементов И 109-117, элемент ИЛИ 118, с первого по третий управляющие входы 119- 121, вход 122 задания интервала времени, тактовый вход 123, вход 124 настройки блока, информационный выход 125 и управляющий выход 126„

Микропрограмма предлагаемого устройства представляет собой микропрограмму конвейерной обработки данных, обеспечивающую выполнение арифметико-логической операции, заданной в команде (например, умножение двух чисел с плавающей точкой; поразрядное логическое умножение двух кодов). Микропрограмма конвейерной обработки данных - это микропрограмма, которая позволяет нести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда- массива для ударных команд), причем каждая из пар элементов находится в определенной фазе выполнения арифметико-логической операции Операция сложения двух чисел с плавающей точкой состоит из следующих фаз: анализ порядков; выравнивание порядков;

20

25

30

35 СЛОжение; нормализация„ Микропрограм-

40

35 СЛОжение; нормализация„ Микропрограм-

45

50

55

ма данной операции позволяет одновременно нормализовать сумму i-й пары чисел, суммировать i+1-ю пару чисел, выравнивать порядки у i+2-й пары чисел (например, i, i+1, i+2 - индексы трех расположенных подряд элементов векторов-операндов). Для организации конвейерного процесса обработки векторов-операндов в устройстве используются микрооперации запроса данных или запроса двойных данных,, Они предназначены для пересылки элемента массива операнда из ОЗУ либо для пересылки элемента массива результата выполнения векторной операции в ОЗУ.

При выполнении определенного запроса соответствующий триггер регистра 16 готовности устанавливается в состояние Готов „ Запрос считается выполненным, если запрашиваемая пересылка выполнена (соответствующий триггер регистра готовности сбрасывается).

51

Благодаря использованию в устройстве механизмов блокировки и выдачи запросов, а также двойных запросов (блок 15), блокировки формирования векторных признаков (таймер 13) и блокировки всех запросов , кроме первого, с помощью кода настройки из блока 11 возможно блокирование выдачи ложных результатов и признаков результата с конвейера до того момента, пока на входы операционных блоков, входящих в. последнюю ступень конвейера для данной операции, не придут результаты обработки первой пары операндов массива данных на воех предшествующих ступенях конвейера,, С выдачей последней пары операндов массива данных запросы на новые операнды также бл окируются „ Возможна также аппаратная блокировка всех запросов, кроме первого, на выдачу одного из операндов при выполнении операций типа вектор-скаляр, например умножения компонент вектора на константу, что приводит к сокращению микропрограмм выполнения таких операций, а следовательно, к сокращению объема блока и всего оборудования в целом и повышению быстродействия устройства. Благодаря наличию в устройстве выхода 26 кода запроса данных и входа 24 признака данных возможно использование данного устройства микропрограммного управления в расширителе команд для векторных операций или для работы с магистралък обмена данными, что увеличивает его функциональные возможности.,

Устройство работает следующим образом.

По входу 23 происходит установка устройства в исходное состояние, подготовка схем к работе (цепи сброса регистров и счетчиков устройства в исходное состояние на схеме не показаны) о По входу 20 в счетчик длины вектора заносится длина вектора Код операции поступает на вход 19 устройства, в блок 11 памяти перекодировки, где происходит перекодирование кода операции в начальный адрес соответствующей микропрограммы, в код настройки операционной части, поступающей на выход 27 и позволяющий реализовать выполнение микропрограмм в конвейерном режиме для данного кода операций, аппаратно модифицировать операции, выполняемые отдельными ус397766

тройствами (например, изменить тип , данных и формат данных в операционных блоках)о

Блок 2 служит для формирования - адреса каждой последующей микрокоманды выполняемой микропрограммы в соответствии с временной диаграммой. По сформированному адресу, поступаю- .Q щему в блок 1 памяти микрокоманд,выбирается соответствующая микрокоманда, поступающая в регистр 3 микрокоманд для хранения в период выполнения микрокоманды

jc Блок 4 дешифраторов расшифровывает код микрокоманды и выдает на выход 25 и блоки устройств управляющие сигналы. Поскольку выполнение микропрограммы происходит в конвейерном ре- 20 жиме, возникает необходимость маскирования записи признаков в регистр 14 векторных признаков0 Для этого служит таймер 13„ Кроме векторных признаков, поступающих на вход 22 25 логических условий, в регистр 14 поступает признак последнего операнда со счетчика длины вектора.

На вход 21 логических условий, в регистр 6 состояния поступают приэ- 30 наки, возникающие при выполнении скалярных операций. Признаки скалярных и векторных операций поступают на мультиплексор 8, с которого под управлением блока дешифраторов 4 необ- ходимый признак поступает в блок 2„

Блок 15 маскирования запросов (первый вариант) используется для маскирования записи запросов в блок 10 фиксации запросов и формирования сиг- дд налов для подсчета длины вектора в счетчике 7

Блок 10 фиксации запросов функционально представляет собой очередь запросов глубиной 1 о Наличие этой оче- дс реди позволяет выставлять из микрокоманды очередной запрос в то время, когда идет обслуживание предыдущего.

Из блока 10 запросы поступают в регистр 16 готовности, сюда же по 5Q входу 24 признака данных поступает информация об условии готовности данных.

Из регистра 16 готовности запросы поступают в блок 9 приоритета, кото- сс рый предназначен для выработки определенного порядка выдачи запросов. С выхода 26 выдается код запроса.

Блок 5 синхронизации формирует временную последовательность синхро

сигналов, используемых для формирования временных соотношений при выполнении микропрограммы В исходное состояние блок синхронизации приводится по входу 23 Запуск

Блок 10 фиксации запросов предназначен для промежуточного хранения запросов, поступающих из блока 15 маскирования запросов, и последующей их передачи в регистр 16 готовности.

Запросы, поступающие на информационный вход 65, запоминаются в регистре 61„ После прихода сигнала на синхровход 66 каждый запрос через свой элемент И (62, 63 или 64) поступает на выход 67 и одновременно обнуляет соответствующий триггер, переводя его в состояние готовности принять очередной запрос

Блок 9 приоритета предназначен для выработки определенного порядка выдачи запросов, поступающих из регистра 16 готовности, а также формирования сигнала, характеризующего отсутствие запросов в этом регистре (состояние, когда все запросы обслужены) .

При отсутствии запросов на информационном входе 75 появляются единич- ные сигналы на выходах инверторов 68 - 70 и, соответственно, элемента И 73о Импульс, поступающий на синхровход 76 при наличии сигнала на выходе элемента И 73 взводит триггер 74 и на первом выходе 77 появится сигнал, говорящий о том, что все запросы в регистре 16 готовности обслужены о

Очередность выдачи запросов на

второй выход 26 реализуется следующим образом:

запрос, поступающий на вход 75j, немедленно проходит на выход 26, ;

запрос, поступающий на вход 75, проходит через элемент И 71 на выход 26г только при отсутствии запроса на входе 75,;

запрос, поступающий на вход 75(, проходит через элемент И 73 на выход 26, тогда и только тогда, когда отсутствуют запросы на входах 753 и 75г.

Блок 5 синхронизации предназначен для формирования определенной времен ной последовательности синхроимпульсов, необходимых для организации правильной работы устройства микропрог

5

0

0

,.

раммного управления векторного процесса .

При подаче сигнала на вход 23 запуска устройства тактовый генератор 78 начинает непрерывно вырабатывать импульсы, поступающие на счетный вход счетчика 79, выходы которого соединены с дешифратором 80 таким образом, что если имеется разрешающий сигнал на управляющем входе 86, то на выходах с 87 по 91 циклически формируются сигналы в соответствии с временной диаграммой (фиг.8).

Сигнал на выходе 92 формируется в моменты времени так же, как сигнал на выходе 89, но в отличие от него, не зависит от разрешающего сигнала на входе 86„

Блок 15 маскирования запросов (фиг.З) предназначен для разрешения или запрещения прохождения запросов в блок 10 фиксации запросов, а также формирования сигналов, необходимых для подсчета длины вектора в счетчике 7.Для маскирования запросов на выдачу результатов, поступающих с входа 56, , на определенное число шагов в счетчике 39 предварительно с входа 57 по входу 54 разрешения записи заносится некоторая константа„ При этом на выходе счетчика отсутствует сигнал разрешения прохождения запросов с входа 561 через элемент И 41 на выход 60. Одновременно разрешается прохождение этих же запросов через элемент И 40 при появлении тактового сигнала Запросы с выхода элемента 40 поступают на вычитающий вход счетчика 39 и уменьшают его содержимое до тех пор, пока он не об- нулится и не заблокирует дальнейшее прохождение запросов на свой вход. При этом на выходе счетчика появляется сигнал разрешения прохождения запросов через элемент И 41 на выход 60 по синхроимпульсам, поступающим на тактовый вход„ Такой способ маскирования запросов устраняет ложное считывание результата1 на число шагов, равное глубине конвейера. На входы 55а и 55 с блока 11 перекодировки поступают сигналы признаков операции вектор-скаляр и скаляр-вектор соответственно При наличии сигналов на входах 552 и 55п можно замаскировать запросы на очередные элементы операндов, поступающие с входов 56 и 563 причем замаскировать все запро10

15

сы, кроме первого Действительно,если отсутствует сигнал переполнения счетчика длины вектора на входе 58,- то по тактовому сигналу первые запросы с входов 56 2 и 56.J через элемент И 48, 43 и 47, 42 соответственно проходят на установочные входы триггеров 52 и 53. При этом на их инверсных выходах появляются сигналы, запрещающие прохождение последующих запросов через элементы И 48, 49 и 47, 50 соответственно на выход 60.

Таймер 13 служит для разрешения или запрещения записи признаков в регистр 14 векторных признаков Для маскирования сигнала разрешения записи (выход 38) на определенное число шагов в счетчик 31 с информационного -входа 34 (по сигналу разрешения 20 записи управляющего входа 35.,) заносится некоторая константа. При этом на выходе счетчика возникает сигнал, запрещающий прохождение сигнала с входа 354,стробируемого синхросигналом с входа 37, через элемент И 33 и одновременно разрешающий прохождение синхросигналов с входа 36 че+ рез элемент И 32 на вычитающий вход счетчикас При этом синхросигналом происходит уменьшение содержимого счетчика до тех пор, пока он не об- нулится и не заблокирует элемент И 32. После обнуления до записи новой константы на выходе счетчика стоит сигнал разрешения прохождения сигнала записи с входа 35 г через элемент И 33 на вход 38„

В случае использования блока 15

25

30

35

до тех пор, пока они не обнулятся и не заблокируют прохождение запросов на свои входы При этом на выходах счетчиков появятся сигналы раз решения прохождения запросов через элементы И 112, 113 и 115 на выход

125по синхроимпульсам, поступающим на вход 41 23 „ Если на входе 121 при- сутствует сигнал переполнения счетчика длины вектора, то запросы с вхо дов 120.,, 120 2 на выход 125 не приходят.

В блоке 15 маскирования (фиг.9) по -входу 124 осуществляется также выбор одного из запросов, по которому происходит счет в счетчике 7 длины вектора Если на входе 124 присутствует единичный сигнал и нет переполнения счетчика длины вектора- (отсутствует сигнал на входе 121), то запрос с входа 120 проходит на выход 125. В противном случае (на входе 124 нулевой сигнал) на выход

126через элементы И 117 и ИЛИ 118 проходит запрос с входа 120

В случае использования в схеме устройства дополнительно блока 17 элементов И признаки вектора результата могут выдаваться на выход 28 через блок 17 элементов И при наличии соответствующего разрешения в микропрограмме получения данного результата

В случае использования в схеме устройства дополнительного блока 18 обслуживания обмена возможна организация функционирования устройства с двойными или одинарными операндами,

маскирования запросов (второй ва риант) а также обслуживания запросов на получение очередных элементов операндов или выдачу результата

для маскирования запросов на определенное число шагов в счетчики 106 - 108 предварительно с входа 122 задания интервала времени (по соответствующим сигналам разрешения записи второго управляющего входа 119) заносятся некоторые константы При этом на выходах счетчиков отсутствуют сигналы разрешения прохождения запросов с входов 120 через блок 11. и элементы И 113 и 115 на выход 125„ Одновременно разрешается прохождение этих же запросов через элементы И 109 - 111 при отсутствии сигнала переполнения счетчика длины вектора на входе 121. Запросы с выходов элементов И 109 и 110 и блока 11 поступают на вычитающие входы счетчиков 106 - 108 и уменьшают их содержимое

0

5

0

5

0

5

до тех пор, пока они не обнулятся и не заблокируют прохождение запросов на свои входы При этом на выходах счетчиков появятся сигналы разрешения прохождения запросов через элементы И 112, 113 и 115 на выход

125по синхроимпульсам, поступающим на вход 41 23 „ Если на входе 121 при- сутствует сигнал переполнения счетчика длины вектора, то запросы с входов 120.,, 120 2 на выход 125 не приходят.

В блоке 15 маскирования (фиг.9) по -входу 124 осуществляется также выбор одного из запросов, по которому происходит счет в счетчике 7 длины вектора Если на входе 124 присутствует единичный сигнал и нет переполнения счетчика длины вектора- (отсутствует сигнал на входе 121), то запрос с входа 120 проходит на выход 125. В противном случае (на входе 124 нулевой сигнал) на выход

126через элементы И 117 и ИЛИ 118 проходит запрос с входа 120

В случае использования в схеме устройства дополнительно блока 17 элементов И признаки вектора результата могут выдаваться на выход 28 через блок 17 элементов И при наличии соответствующего разрешения в микропрограмме получения данного результата

В случае использования в схеме устройства дополнительного блока 18 обслуживания обмена возможна организация функционирования устройства с двойными или одинарными операндами,

а также обслуживания запросов на получение очередных элементов операндов или выдачу результата

. При поступлении на вход 103, единичных сигналов, говорящих о том, что будут обрабатываться операнды двойной длины, на выходе одного из элементов И 93, 94 или 95 в зависимости от того, какой из трех сигналов в данный момент поступил на вход 104, появится единичный сигнал, по- ступающий через элемент ИЛИ 100 на вход триггера 102. Одновременно этот ригнал поступает на инверсный вход элемента И 97 и запрещает прохождение признака данных с входа 24 признака данных через элемент И 97 и ИЛИ

101на выход 105. Поскольку триггер

102в начальный момент времени находится в- нулевом состоянии, то он так

и

же запрещает прохождение первого сиг нала признака данных через элементы И 96 и ИЛИ 101 на выход 105. По заднему фронту первого сигнала признака данных, поступающего на С-вход, триг гер 102 перебрасывается в единичное состояние и разрешает прохождение следующего признака данных через элементы И 96 и ИЛИ 101 на выход 105 По заднему фронту второго сигнала признака данных триггер сбрасывается в нулевое состояние Таким образом, если обрабатываются операнды двойной длины, на выходе 105 появляется каждый второй сигнал признака данных, поступающий на вход регистра готовности. Если же для какого-либо сигнала запроса отсутствует соответствующий сигнал признака операнда двойной длины (вход 103), то на выходе элемента ИЛИ 100 присутствует нулевой сигнал, разрешающий прохождение первого сигнала признака данных с входа 24 через элементы И 97 и ИЛИ 101 на выход 105«,

Блок 18 обеспечивает также формирование сигналов чтейия (выдачи) результата или записи (приема) операндов . Если на вход элемента И 95 по шине 104 поступает единичный сигнал, соответствующий запросу на выдачу результата, то на выходе элемента И 98 по входу 24 признака данных возникает сигнал чтения, поступающий на выход 29 о Если же на входе элемента И 95 отсутствует единичный сигнал, то по сигналам признака данных на быходе элемента И 99 возникают сигналы записи соответствующего операнда, поступающие на выход 30„

Таким образом, благодаря блоку 18 обслуживания обмена обеспечивается управление операндами и результатом как одинарной, так и двойной длины, а также обеспечивается возможность работы устройства с магистралью обмена данными для многопроцессорных устройств и уменьшение разрядности кода признаков управления запросами.

Формула изобрет ения

1. Устройство микропрограммного управления, содержащее блок памяти перекодировки, блок формирования адреса, блок памяти микрокоманд, регистр микрокоманд, блок синхронизации, блок дешифраторов, регистр век

9776 12

торных признаков, регистр состояний и мультиплексор, причем адресный вход блока памяти перекодировки является входом кода команды устройства,

выход поля адреса начальной микрокоманды блока памяти перекодировки соединен с первым информационным входом блока формирования адреса, инфор

мационный выход которого соединен с

адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля микроопераций которого соединен с входом блока дешифраторов, группа выходов которого является группой выходов кода микроопераций устройства, первый и второй выходы блока дешифраторов соединены

соответственно с Управляющим входом мультиплексора и первым управляющим входом блока формирования адреса,второй управляющий, второй информационный и тактовый входы которого соединены соответственно с выходом мультиплексора, выходом поля адреса регистра микрокоманд и первым выходом блока синхронизации, второй выход и вход запуска которого соединены соответственно с тактовым входом регистра микрокоманд и входом запуска устройства, первый и второй входы логических условий устройства подключены к информационным входам соответственно регистра состояний и регистра векторных признаков, выходы которых соединены соответственно с первым и вторым информационными входами мультиплексора, тактовый вход

регистра состоянии соединен с третьим выходом блока синхронизации, о т- личающееся тем, что, с целью расширения области применения за счет обеспечения использования

его для управления векторным процессором конвейерной обработки данных, оно дополнительно содержит счетчик длины вектора, таймер, блок маскирования запросов, блок фиксации запросов, регистр готовности и блок приоритета, информационный выход которого является выходом кода запроса данных устройства, информационный вход блока приоритета соединен с выходом регистра готовности, первый и второй информационные входы которого подключены соответственно к третьему входу логических условий устройства и выходу блока фиксации запросов, ин

формационный вход которого соединен с. информационным выходом блока маскирования запросов, вход задания интервала времени маскирования которого соединен с выходом поля задания интервала времени регистра микрокоманд и входом задания интервала времени таймера, вход признака режима работы которого соединен с третьим входом блока дешифраторов и первым управляющим входом блока маскирования запросов , второй управляющий вход и вход настройки которого соединен соответственно с четвертым выходом блока де шифраторов и с выходом поля настройки блока памяти перекодировки, трети управляющий вход блока маскирования запросов соединен с выходом переполнения счетчика длины вектора и дополнительным разрядом информационног входа регистра векторных признаков, вход записи которого соединен с выходом таймера, первый тактовый вход которого соединен с тактовым входом блока фиксации запросов и третьим входом блока синхронизации, четвертый, пятый и шестой выходы которого соединены соответственно с вторым тактовым входом таймера, тактовым входом блока маскирования запросов и тактовым входом блока приоритета, выход признака отсутствия запросов которого соединен с входом управления режимами блока синхронизации, управляющий выход блока маскирования запросов соединен со счетным входом счетчика длины вектора, установочный вход ко.торого является входом задания кода длины вектора устройства,

2. Устройство по п.1, отличающееся тем, что блок маскирования запросов содержит два триггера, одиннадцать элементов И, элемент ИЛИ и счетчик, выход переноса которого соединен с инверсным входом первого и первым входом второго элементов И, выход первого элемента И соединен со счетным входом счетчика, информационный вход которого является входом задания интервала времени блока, первые входы третьего и четвертого элементов И являются соответственно первым и вторым разрядами входа настройки блока, третий разряд входа настройки которого подключен к первому входу пятого и инверсному входу шестого элементов И, выходы ко

0

0

5

-

торых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с прямым входом седьмого элемента И, инверсный вход которого соединен с инверсными входами восьмого и девятого элементов И и является третьим управляющим входом блока, тактовый вход которого подключен к первым прямым входам первого, восьмого и девятого элементов И, второй прямой вход первого элемента И соединен с вторым входом второго элемента И и является первым раз-рядом второго управляющего входа блока, второй разряд второго управляющего входа которого подключен к прямому входу шестого элемента И и второму прямому входу девятого элемента И, выход которого соединен с вторым входом четвертого элемента И и первым входом десятого элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход установки в I которого соеди -

0

5

0

5

0

5

нен с выходом четвертого элемента И, третий разряд второго управляющего входа блока подключен к второму входу пятого элемента И и второму прямому входу восьмого элемента И, выход которого соединен с вторым входом третьего элемента И и первым входом одиннадцатого элемента И, второй вход которого соединен с инверсным выходом второго триггера, вход установки в 1 которого соединен с выходом третьего элемента И, вход задания режима записи-счета счетчика является первым управляющим входа блока, выходы второго, десятого и одиннадцатого элементов И образуют информационный выход блока, управляющий выход которого подключен к выходу седьмого элемента И, входы установки в О первого и второго триггеров соединены между собой и подключены к входу начальной установки устройства.

3. Устройство по п.1, о т л и - чающееся тем, что блок маскирования запросов содержит три счетчика, девять элементов И и элемент ИЛИ, причем информационные входы с первого по третий счетчиков образуют вход задания интервалов времени блока, счетные входы с первого по третий счетчиков соединены с выходами соответственно с первого по третий элементов И, первые инверсные входы которых соединены с инверсными входа15

ми с четвертого по шестой элементов И и подключены к третьему управляющему входу блока, первый управляющий вход которого образуют входы задания режима записи-счета с первого по третий счетчиков, выход переноса первого счетчика соединен с вторым инверсным входом первого и первым прямым входом четвертого элементов И, второй прямой вход четвертог, первый прямой пятого и первый вход седьмого элементов И соединены между собой и подключены к тактовому входу блока, вход настройки которого подключен к первому входу восьмого и инверсному входу девятого элементов И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с прямым входом шестого элемента И, выход которого является управляющим выходом блока, информационный выход которого образует выходы четвертого, пятого и седьмого элементов И, выход переноса второго счетчика соединен с вторым инверсным входом второго и вторым прямым входом пятого элементов И, выходы переноса третьего счетчика соединен с вторым инверсным входом третьего и вторым входом седьмого элементов И, первый разряд второго . управляющего блока подключен к прямому входу первого, третьему прямому входу четвертого и второму входу вось

15

Iмого элементов И, второй разряд второго управляющего входа блока подключен к прямому входу второго,третьему прямому входу пятого и прямому входу девятого элементов И, третий разряд второго управляющего входа блока подключен к прямому входу третьего и третьему входу седьмого элементов И.

4. Устройство ,отлича- ю щ е е с я тем, что дополнительно

-

10

15

20

«

539776 . 16

содержит блок элементов И, первый вход которого соединен с выходом регистра векторных признаков, второй вход и выход блока элементов И подключены соответственно к третьему выходу блока дешифраторов и к выходу векторных признаков устройства.

5. Устройство по п.1, о т л и - чающееся тем, что дополнительно содержит блок обслуживания обмена, содержащий семь элементов И, два элемента ИЛИ и триггер, причем дополнительные три разряда выхода поля настройки блока памяти перекодировки соединены с первыми входами соответственно первого, второго и третьего элементов И, выходы которых соединены соответственно с первым и третьим входами первого элемента ИЛИ, выход которого соединен с инверсным входом четвертого элемента И и информационным входом триггера, вход синхронизации которого соединен с прямыми входами третьего и четвертого элементов И, первыми входами пятого и шестого элементов И и подключены к входу признака данных устройства,выход триггера соединен с вторым входом пятого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и входом 35 синхронизации регистра готовности, второй информационный вход которого соединен с информационным выходом блока приоритета и с вторыми входами первого, второго, третьего и шестого элементов И и инверсным входом четвертого элемента И, выходы шестого и четвертого элементов И являются соответственно первым и вторым выходами синхронизации запросов устройства.

25

30

45

25

28

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для сопряжения процессора с общей магистралью | 1985 |

|

SU1291998A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управления векторного процессора или расширителя команд для векторных операций. Целью изобретения является расширение области применения за счет обеспечения возможности использования его для управления векторным процессором конвейерной обработки данных. Устройство содержит блок памяти микрокоманд, блок формирования адреса, регистр микрокоманд, блок дешифраторов, блок синхронизации, регистр состояния, счетчик длины вектора, мультиплексор, блок приоритета, блок фиксации запросов, блок памяти перекодировки,таймер, регистр векторных признаков, блок маскирования запросов, регистр готовности, блок элементов И, блок обслуживания обмена. Благодаря блоку обслуживания обмена обеспечивается управление операндами и результатами как одинарной, так и двойной длины, а также обеспечивается возможность работы устройства с магистралью обмена данными для многопроцессорных устройств и уменьшение разрядности кода признаков управления запросами. 4 з.п. ф-лы, 9 ил.

Фиг-t

55г JSf

ФигА

ФигЛ

Цикл Фиг.8

128 т т

Фиг. 9

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Проектирование цифровых систем на комплектах микропрограммируемых БИС/ Под ред | |||

| В.Г | |||

| Колесникова | |||

| M.i Радио и связь, 1984, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

Авторы

Даты

1990-01-30—Публикация

1987-02-19—Подача