Изобретение относится к вычислительной технике и может быть использовано для контроля и отладки вычислительных систем.

Цель изобретения - повьштение достоверности работы устройства.

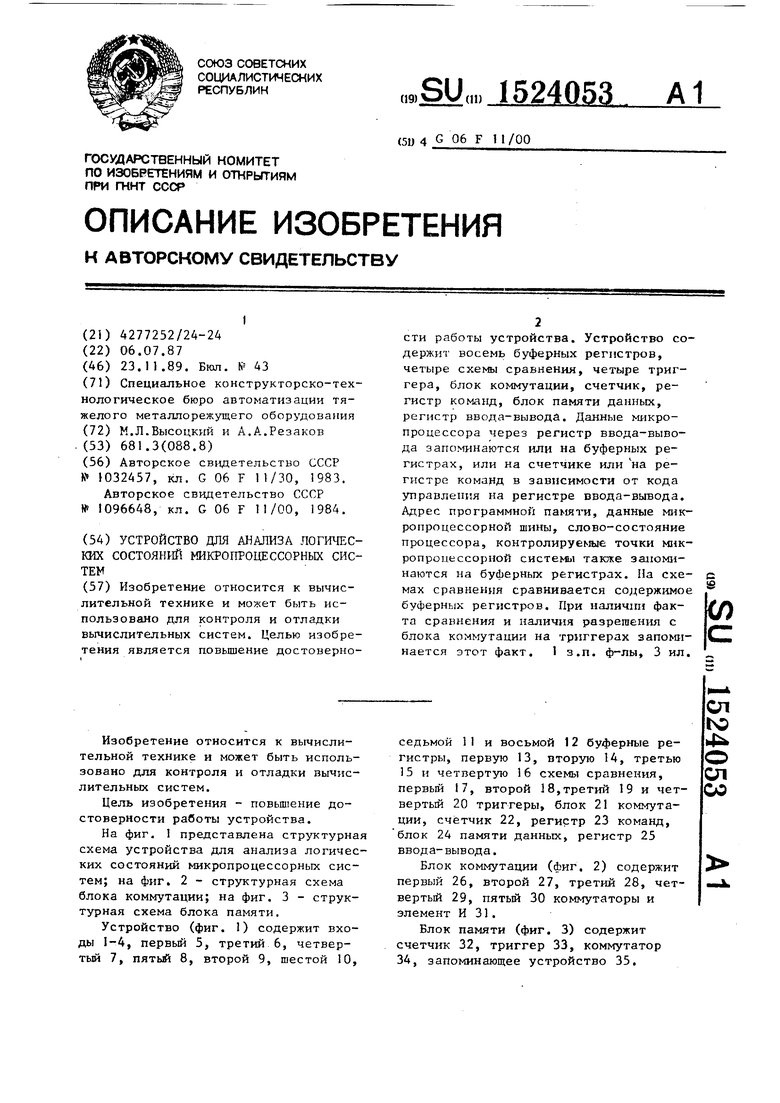

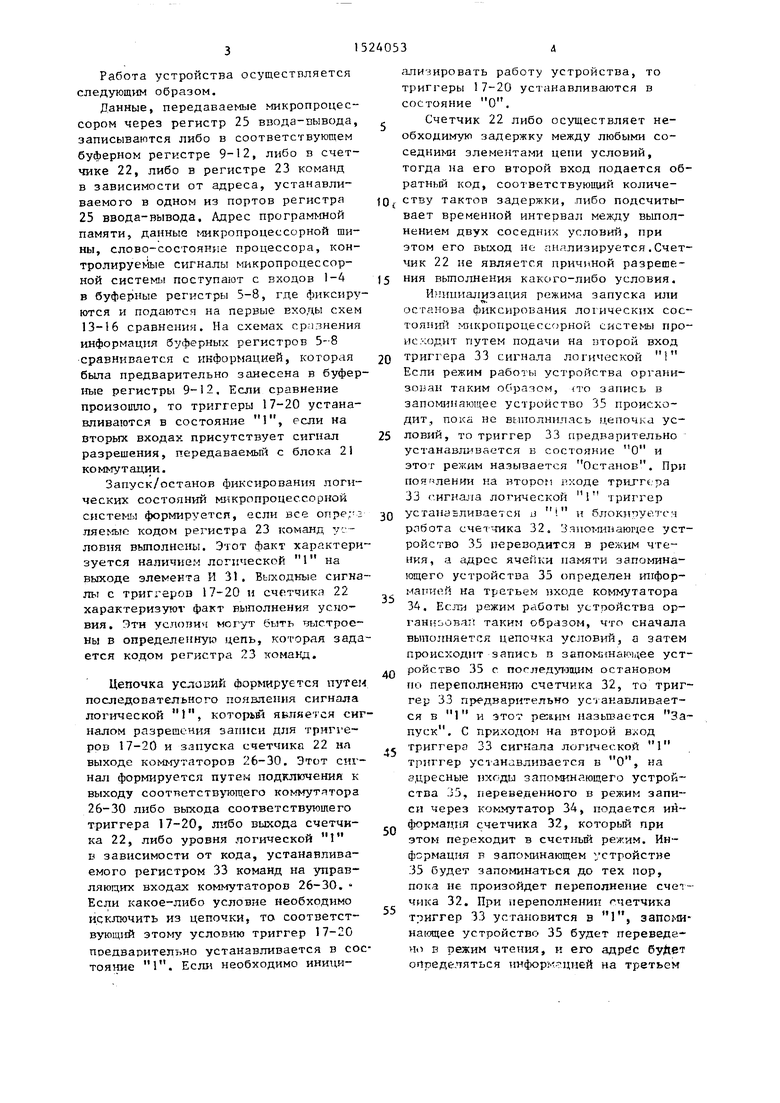

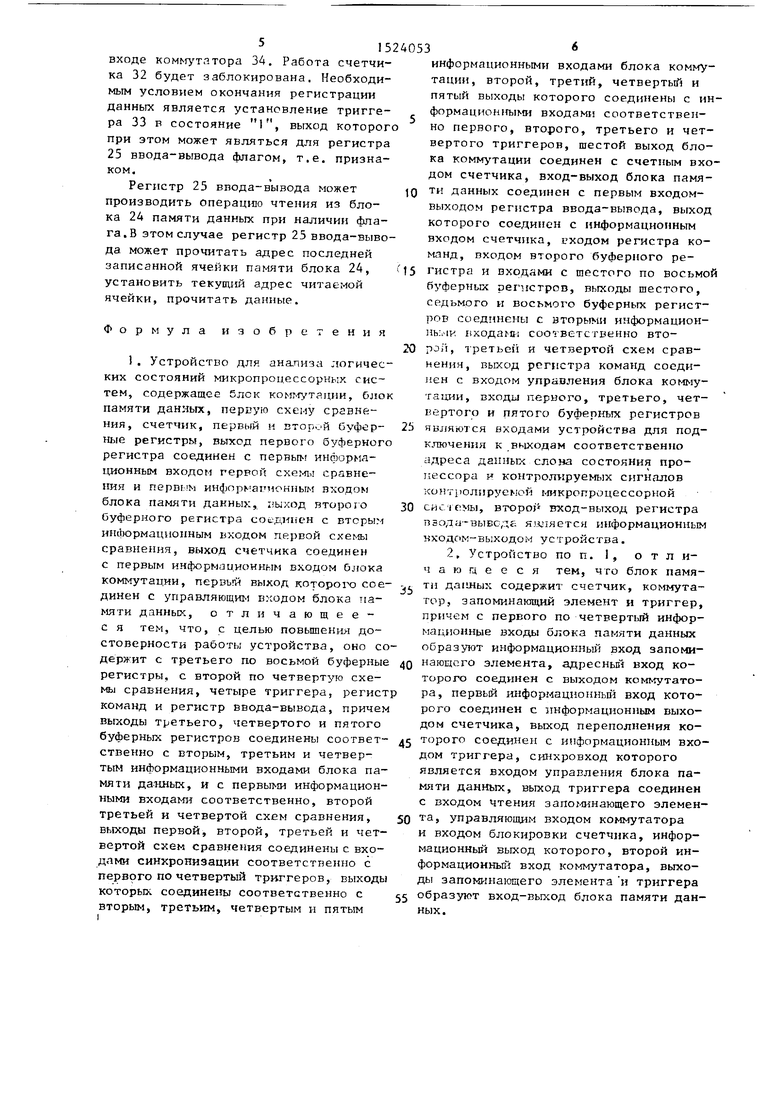

На фиг. 1 представлена структурная схема устройства для анализа логических состояний микропроцессорных систем; на фиг. 2 - структурная схема блока коммутации; на фиг. 3 - структурная схема блока памяти.

Устройство (фиг. 1) содержит входы 1-4, первый 5, третий 6, четвертый 7, пятый В, второй 9, шестой 10,

седьмой 11 и восьмой 12 буферные регистры, первую 13, вторую 14, третью 15 и четвертую 16 схемы сравнения, первый 17, второй 18,третий 19 и четвертый 20 триггеры, блок 21 коммутации, счетчик 22, регистр 23 команд, блок 24 памяти данных, регистр 25 ввода-вывода.

Блок коммутации (фиг. 2) содержит первый 26, второй 27, третий 28, чет- вертьй 29, пятый 30 коммутаторы и элемент И 31.

Блок памяти (фиг. 3) содержит счетчик 32, триггер 33, коммутатор 34, запоминающее устройство 35.

СП

to

4 О СП

со

Работа устройства осуществляется следующим образом.

Данные, передаваемые микропроцессором через регистр 25 ввода-вывода, записываются либо в соответствующем буферном регистре 9-12, либо в счетчике 22, либо в регистре 23 команд в зависимости от адреса, устанавливаемого в одном из портов регистра 25 ввода-вывода. Адрес пpoгpaм ffloй памяти, данные микропроцессорной шины, слово-состояние процессора, контролируемые сигналы м-1Кропроцессорной систем1л поступают с входов 1-4 в буферные регистры 5-8, где фиксируются и подаются на первые входы схем 13-16 сравнения. На схемах сравнения информация буферных регистров 5-8 сравнивается с информацией, которая была предварительно занесена в буферные регистры 9-12. Если сравнение произошло, то триггеры 17-20 устанавливаются в состояние 1, если на вторых входах присутствует сигнал разрешения, передаваемый с блока 21 коммутации.

Запуск/останов фиксирования логических состояний М11кропроцессорной системы формируется, если все опре;;; ляемыс кодом регистра 23 команд условия вьтолнсиы. Этот факт характеризуется наличием логической 1 на выходе элемента И 31. Выходные сигналы с триггеров 17-20 и счетчика 22 характеризуют факт выполнения усно- вия. Эти могут быть TJbicTpoe- ны в определенную цепь, которая зада ется кодом регистра 23 команд.

Цепочка условий формируется путем последовательного появления сигнала ло1Л1ческой 1, которьй является сигналом разрешения записи для триггеров 17-20 и запуска счетчика 22 на выходе коммутаторов 26-30. Этот сигнал формируется путем подключения к выходу соответствующего коммутатора 26-30 либо выхода соответствующего триггера 17-20, mi6o выхода счетчика 22, либо уровня логической 1 в зависимости от кода, устанавливаемого регистром 33 команд на управляющих входах ком тутаторов 26-30, Если какое-либо условие необходимо исключить из цепочки, то соответствующий этому условию триггер 17-20 предварительно устанавливается в состояние 1. Если необходимо иници

0

5

0

5

0

5

0

5

ализировать работу устройства, то триггеры 17-20 устанавливаются в состояние О.

Счетчик 22 либо осуществляет необходимую задержку между любыми соседними элементами цепи условий, тогда на его второй вход подается обратный код, соответствующий количеству тактов задержки, либо подсчитывает временной интервал между выполнением двух соседних условий, при этом его выход HG анализируется.Счетчик 22 не является причиной разрешения вьшолнения какого-либо условия.

Инициализация режима запуска или останова фиксирования логических сое- тоянш микропроцессорной системы происходит путем подачи на пторой вход триггера 33 сигнала логической 1 Если режим работы устройства организован таким оСфазом, ITO запись в запоминающее устройство 35 происходит, пока не вьитолнилась цепочка условий, то триггер 33 предварительно устанавлз- вается в состояние О и этот режим называется Останов. При поя гулении на втором лходе триггера 33 (лигиала логической 1 триггер устанавливается а i и блокируе.тсм работа счетчика 32. Зянот-шнающее устройство 35 переводится в режим чтения, а адрес ячейки памяти запоминающего устройства 35 определен информацией на третьем 5зходе коммутатора 34. EcjTH режим работы устройства ор- ганн:.ова: таким образом, что сначала выполняется цепочка условий, а затем происходит запись в запо№1наю1дее устройство 35 с поглед по1цим остановом по переполнен ш счетчика 32, то триггер 33 предварительно устанавливается в 1 и зтот ре:в;им называется Запуск . С приходом на второй вход триггера 33 сигнала логической 1 триггер устанавливается в О, на адресные нходи запоминающего устройства J5, переведенного в режим записи через коммутатор 34, подается ий- формапдш счетчика 32, которьп при этом переходит в счетньш режим. Информация в запоминающем устройстве 35 будет запоминаться до тех пор, пока не произойдет переполнение счетчика 32, При переполнении счетчика триггер 33 установится в 1, запоминающее устройство 35 будет переведе- VU1 в режим чтения, и его адрес буйет определяться информгцней на третьем

входе KOMNf TaTopa 34. Работа счетчика 32 будет заблокирована. Необходимым условием окончания регистрации данных является установление триггера 33 р состояние 1, выход которог при этом может являться для регистра 25 ввода-вывода флагом, т.е. признаком.

Регистр 25 ввода-вывода может производить операцию чтения из блока 24 памяти данных при наличии флага. В этом случае регистр 25 ввода-вывода может прочитать адрес последней записанной ячейки памяти блока 24, установить текущий адрес читаемой ячейки, прочитать данные.

Формула изобретения

1 . Устройство для ана.пиза логических состояний микропроцессорных систем, содержащее 5лок ком 7тации, бло памяти данных, первую схему сравнения, счетчик, первьй и второй буфер- ные регистры, выход первого буферног регистра соединен с первым информационным входом гервой cxei-fiii сравнения и первым инфоркшгмонным входом блока памяти данных, пыход второю буферного регистра соединен с вторым инйюрмациопным входом первой схемы сравнения, выход счетчика соединен с первым информационным входом блока

информационными входами блока коммутации, второй, третий, четвертый и пятый выходы которого соединены с ин формационныьт входами соответственно первого, второго, третьего и четвертого триггеров, шестой выход блока коммутации соединен с счетным входом счетчика, вход-выход блока памяти данных соединен с первым входом- выходом регистра ввода-вывода, выход которого соединен с информационным входом счетчика, входом регистра команд, входом второго буферного регистра и входами с шестого по восьмо буферных регистров, выходы шестого, седьмого и восьмого буферных регистров соединены с вторыми информацион- нь:.-1к nxoдaм J соответственно вто- poii, 1ретьей и четвертой схем сравнения, выход регистра команд соединен с входом управления блока коммутации, входы перыого, третьего, четвертого и пятого буфер1-гых регистров явJ/яютcя входами устройства для подключения к вь1ходам соответственно адреса данных слона состояния процессора и контролируемых сигналов контролируемой ьшкропроцессорной сисгемы, второй вход-выход регистра пзоды-вывсдс; яшшется информационным кходом-выходом устройства.

2, Устройство по п. 1, о т л и- ч а ю гд е е с я тем, что блок памя

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и отладки вычислительных систем. Цель изобретения - повышение достоверности работы устройства. Устройство содержит восемь буферных регистров, четыре схемы сравнения, четрые триггера, блок коммутации, счетчик, регистр команд, блок памяти данных, регистр ввода-вывода. Данные микропроцессора через регистр ввода-вывода запоминаются или на буферных регистрах, или на счетчике, или на регистре команд в зависимости от кода управления на регистре ввода-вывода. Адрес программной памяти, данные микропроцессорной шины, слово-состояние процессора, контролируемые точки микропроцессорной системы также запоминаются на буферных регистрах. На схемах сравнения сравнивается содержимое буферных регистров. При наличии факта сравнения и наличия разрешения с блока коммутации на триггерах запоминается этот факт. 1 з.п. ф-лы, 3 ил.

коммутации, первый выход которо1Х) сое- -. ти данных содержит счетчик, коммута- динен с управляющим входом блока па- тор, запоминаклдий элемент и триггер, мяти данных, отличающее- причем с первого по четверт1 1Й инфор- с я тем, что, с целью повьппения до- мационные входы блока памяти данных

образуют информационньш вход запоми40

стоверности работы устройства, оно содержит с третьего по восьмой буферные регистры, с второй по четвертую схемы сравнения, четыре триггера, регистр команд и регистр ввода-вывода, причем выходы третьего, четвертого и пятого буферных регистров соединены соответ- дд ственно с вторым, третьим и четвертым информационными входами блока памяти данных, и с первыми информационными входами соответственно, второй третьей и четвертой схем сравнения, выходы первой, второй, третьей и четвертой схем сравне1 ия соединены с входами сингсронизации соответственно с первого по четвертый триггеров, вькоды которых соединены соответственно с вторым, третьим, четвертым и пятым

наюцсго элемента, адресньй вход которого соединен с выходом коммутатора, первый информационньп вход которого соединен с информационньм выходом счетчика, выход переполнения которого соединен с информационным входом триггера, синхровход которого является входом управления блока памяти данных, выход триггера соединен с входом чтения запогданающего элемента, управляющим входом коммутатора и входом блокировки счетчика, информационный выход которого, второй информационньш вход коммутатора, выходы запоминающего элемента и триггера 55 образуют вход-выход блока памяти данных.

50

наюцсго элемента, адресньй вход которого соединен с выходом коммутатора, первый информационньп вход которого соединен с информационньм выходом счетчика, выход переполнения которого соединен с информационным входом триггера, синхровход которого является входом управления блока памяти данных, выход триггера соединен с входом чтения запогданающего элемента, управляющим входом коммутатора и входом блокировки счетчика, информационный выход которого, второй информационньш вход коммутатора, выходы запоминающего элемента и триггера образуют вход-выход блока памяти данных.

J

Фие. 3

Составитель М.Высоцкий Редактор Л.Зайцева Техред Л.ОлийныкКорректор Т.Палий

Заказ 7044/50 Тираж 668Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

524053

35

| Развертка с винтовым гидравлическим двигателем | 1931 |

|

SU32457A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1987-07-06—Подача