Изобретение относится к импульсной технике, предназначено для управления импульсным ускорителем, лазерными системами, генераторами 11мпульсов произ- вольной формы и может быть использовано в синхронизаторах, управляющих и вычислительных системах.

Цель изобретения - повышение точности задания временного положения импульсов в серии и расширение функциональных возможностей.

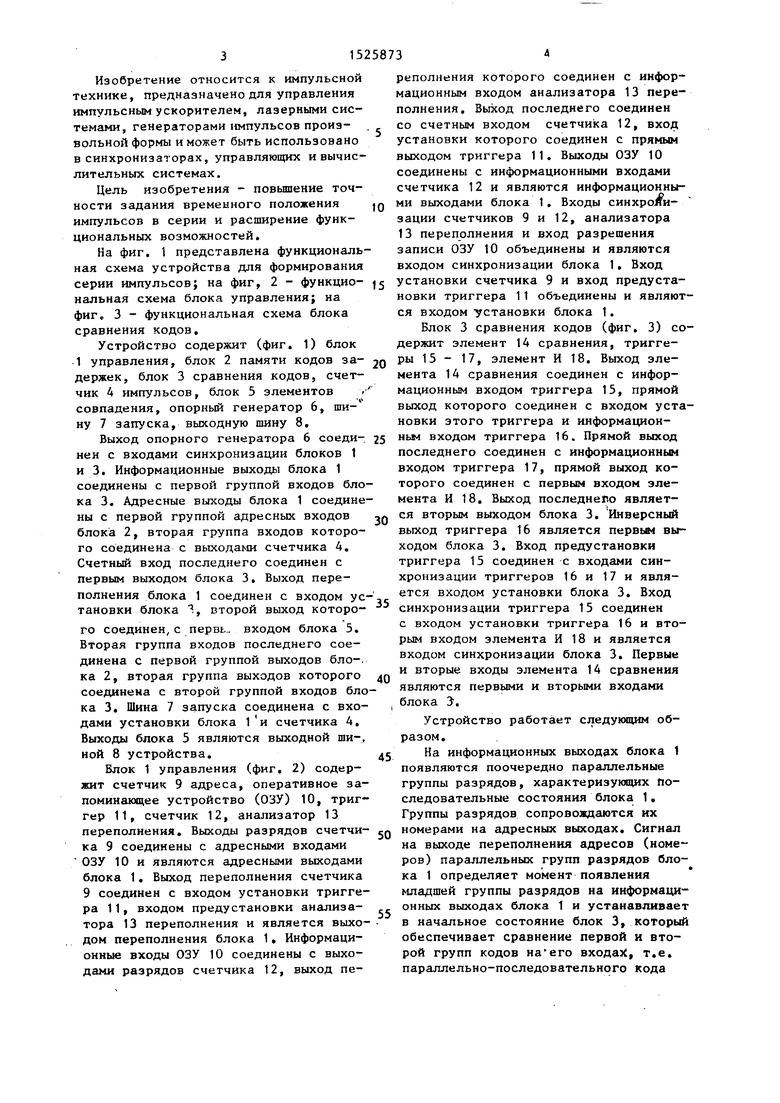

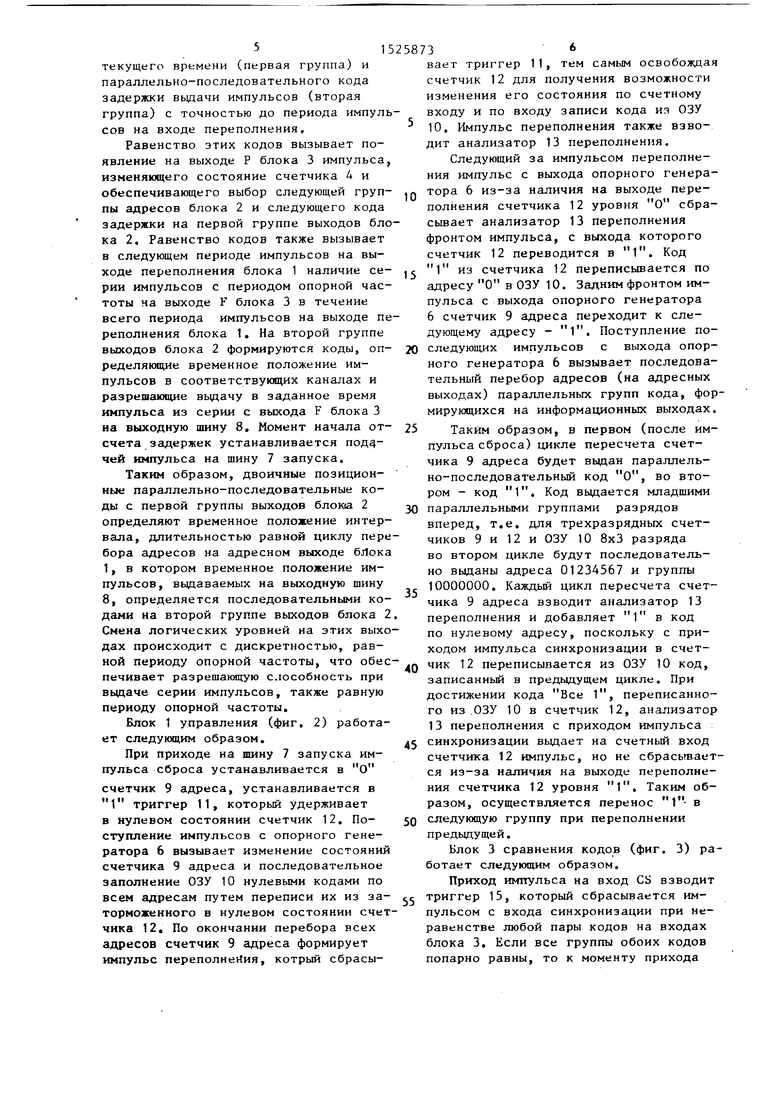

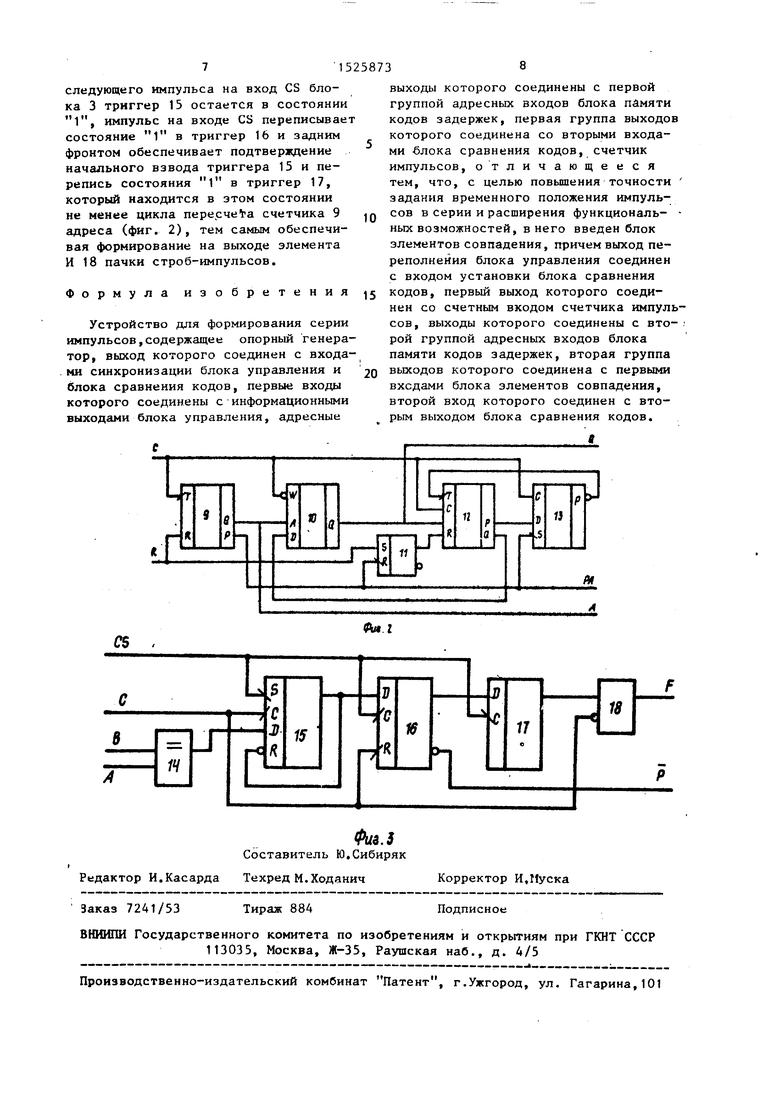

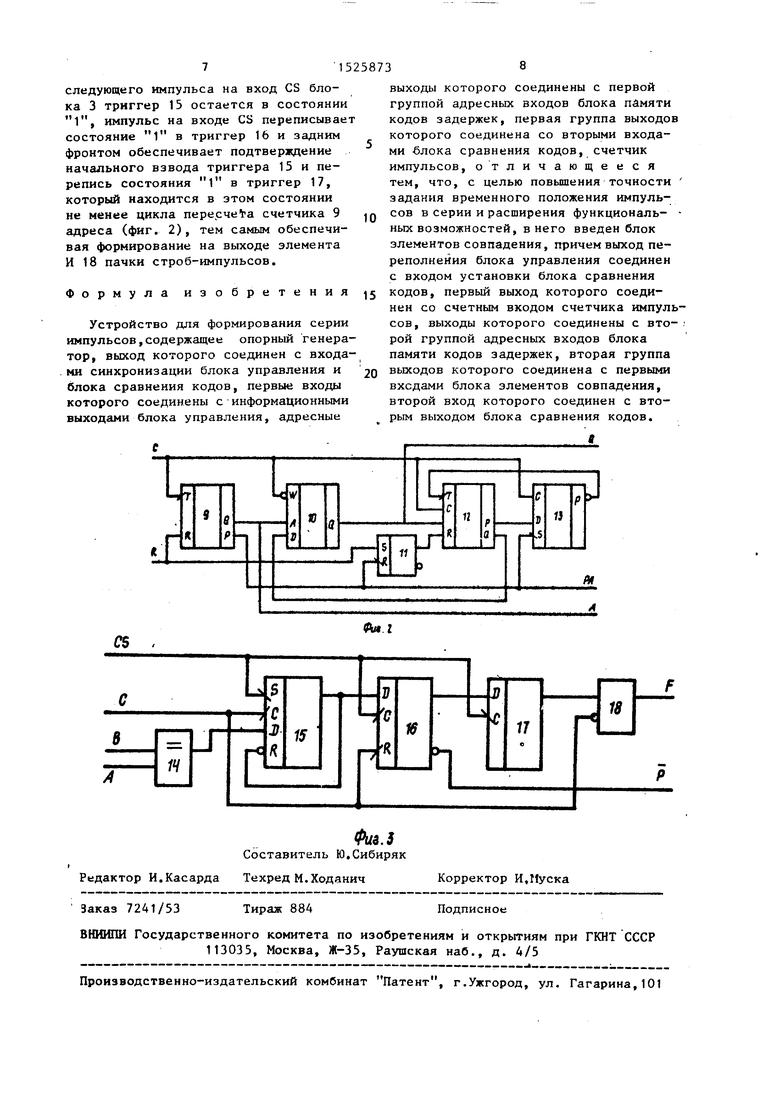

На фиг. 1 представлена функциональная схема устройства для формирования серии импульсов; на фиг, 2 - функцио- нальная схема блока управления; на фиг, 3 - функциональная схема блока сравнения кодов.

Устройство содержит (фиг. 1) блок .1 управления, блок 2 памяти кодов за- держек, блок 3 сравнения кодов, счетчик А импульсов, блок 5 элементов совпадения, опорный генератор 6, шину 7 запуска, выходную шину 8.

Выход опорного генератора 6 соеди- ней с входами синхронизации блоков 1 и 3. Информационные выходы блока 1 соединены с первой группой входов блока 3. Адресные выходы блока 1 соединены с первой группой адресных входов блока 2, вторая группа входов которого соединена с выходами счетчика 4. Счетный вход последнего соединен с первым выходом блока 3. Выход переполнения блока 1 соединен с входом установки блока j второй выход которо

го соединен, с первь-. входом блока 5. Вторая группа входов последнего соединена с первой группой выходов бло-. ка 2, вторая группа выходов которого соединена с второй группой входов блока 3. Шина 7 запуска соединена с вхо- дами установки блока 1 и счетчика 4. Выходы блока 5 являются выходной ши-, ной В устройства.

Блок 1 управления (фиг. 2) содержит счетчик 9 адреса, оперативное запоминающее устройство (ОЗУ) 10, триггер 11, счетчик 12, анализатор 13 переполнения. Выходы разрядов счетчи- ка 9 соединены с адресными входами ОЗУ 10 и являются адресными выходами блока 1. Выход переполнения счетчика 9 соединен с входом установки триггера 11, входом предустановки анализа- тора 13 переполнения и является выхо- дом переполнения блока 1. Информационные входы ОЗУ 10 соединены с выходами разрядов счетчика 12, выход пе;

. jg

2о

25 ,Q дд д5

Q. 35

реполнения которого соединен с информационным входом анализатора 13 переполнения. последнего соединен со счетным входом счетчика 12, вход установки которого соединен с прямым выходом триггера 11. Выходы ОЗУ 10 соединены с информационными входами счетчика 12 и являются информационными выходами блока 1. Входы синхрояи- зации счетчиков 9 и 12, анализатора 13 переполнения и вход разрешения записи ОЗУ 10 объединены и являются входом синхронизации блока 1. Вход установки счетчика 9 и вход предустановки триггера 11 объединены и являются входом установки блока 1.

Блок 3 сравнения кодов (фиг. 3) содержит элемент 14 сравнения, триггеры 15 - 17, элемент И 18. Выход элемента 14 сравнения соединен с информационным входом триггера 15, прямой выход которого соединен с входом установки этого триггера и информационные входом триггера 16. Прямой выход последнего соединен с информационным входом триггера 17, прямой выход которого соединен с первым входом элемента И 18. Выход последнего является вторым выходом блока 3. Инверсный выход триггера 16 является первьм выходом блока 3. Вход предустановки триггера 15 соединен с входами синхронизации триггеров 16 и 17 и является входом установки блока 3. Вход синхронизации триггера 15 соединен с входом установки триггера 16 и вторым входом элемента И 18 и является входом синхронизации блока 3. Первые и вторые входы элемента 14 сравнения являются первыми и вторыми входами блока Э.

Устройство работает следуюпщм образом.

На информационных выходах блока 1 появляются поочередно параллельные группы разрядов, характеризующих Последовательные состояния блока 1. Группы разрядов сопровождаются их номерами на адресных выходах. Сигнал на выходе переполнения адресов (номеров) параллельных групп разрядов блока 1 определяет момент появления младшей группы разрядов на информационных выходах блока 1 и устанавливает в начальное состояние блок 3, который обеспечивает сравнение первой и второй групп кодов входах, т.е. параллельно-последовательного кода

текущего времени (первая группа) и параллельно-последовательного кода задержки выдачи импульсов (вторая группа) с точностью до периода импульсов на входе переполнения,

Равенство этих кодов вызывает появление на выходе Р блока 3 импульса изменяющего состояние счетчика 4 и обеспечивающего выбор следующей группы адресов блока 2 и следующего кода задержки на первой группе выходов блока 2. Равенство кодов также вызывает в следующем периоде импульсов на выходе переполнения блока 1 наличие серии импульсов с периодом опорной частоты на выходе F блока 3 в течение всего периода импульсов на выходе переполнения блока 1. На второй группе выходов блока 2 формируются коды, определяющие временное положение импульсов в соответствующих каналах и разрешаюпще выдачу в заданное время импульса из серии с выхода F блока 3 на выходную шину 8, Момент начала отсчета задержек устанавливается чей импульса на шину 7 запуска.

Таким образом, двоичные позицион- ные параллельно-последовательные коды с первой группы выходов блока 2 определяют временное положение интервала, длительностью равной циклу перебора адресов на адресном выходе бЛока 1, в котором временное положение импульсов, выдаваемых на выходную шину 8, определяется последовательными кодами на второй группе выходов блока 2 Смена логических уровней на этих выходах происходит с дискретностью, равной периоду опорной частоты, что обеспечивает разрешающую слособность при выдаче серии импульсов, также равную периоду опорной частоты.

Блок 1 управления (фиг. 2) работает следующим образом.

При приходе на шину 7 запуска импульса сброса устанавливается в О

счетчик 9 адреса, устанавливается в 1 триггер 11, который удерживает в нулевом состоянии счетчик 12. Поступление импульсов с опорного генератора 6 вызывает изменение состояний счетчика 9 адреса и последовательное заполнение ОЗУ 10 нулевыми кодами по всем адресам путем переписи их из заторможенного в нулевом состоянии счетчика 12, По окончании перебора всех адресов счетчик 9 адреса формирует импульс переполнения, котрый сбрасы . 10

15

20

25

5258736

вает триггер 11, тем самым освобождая счетчик 12 для получения возможности изменения его состояния по счетному входу и по входу записи кода из ОЗУ 10. Импульс переполнения также взводит анализатор 13 переполнения.

Следующий за импульсом переполнения импульс с выхода опорного генератора 6 из-за наличия на выходе переполнения счетчика 12 уровня О сбрасывает анализатор 13 переполнения фронтом импульса, с выхода которого счетчик 12 переводится в 1. Код 1 из счетчика 12 переписывается по адресу О в ОЗУ 10. Задним фронтом импульса с выхода опорного генератора 6 счетчик 9 адреса переходит к следующему адресу - 1. Поступление последующих импульсов с выхода опорного генератора 6 вызывает последовательный перебор адресов (на адресных выходах) параллельных групп кода, формирующихся на информационных выходах.

Таким образом, в первом (после импульса сброса) цикле пересчета счетчика 9 адреса будет выдан параллельно-последовательный код О, во втором - код 1. Код выдается младшими параллельными группами разрядов вперед, т.е. для трехразрядных счетчиков 9 и 12 и ОЗУ 10 8x3 разряда во втором цикле будут последовательно выданы адреса 01234567 и группы 10000000. Каждый цикл пересчета счетчика 9 адреса взводит анализатор 13 переполнения и добавляет 1 в код по нулевому адресу, поскольку с приходом импульса синхронизации в счетчик 12 переписывается из ОЗУ 10 код, записанный в предыдущем цикле. При достижении кода Все 1, переписанного из .ОЗУ 10 в счетчик 12, анализатор 13 переполнения с приходом импульса синхронизации выдает на счетный вход счетчика 12 импульс, но не сбрасывается из-за наличия на выходе переполнения счетчика 12 уровня 1. Таким образом, осуществляется перенос в следующую группу при переполнении предыдущей.

Блок 3 сравнения кодов (фиг. 3) работает следующим образом.

Приход импульса на вход CS взводит 5 триггер 15, который сбрасывается импульсом с входа синхронизации при неравенстве любой пары кодов на входах блока 3. Если все группы обоих кодов попарно равны, то к моменту прихода

30

35

40

45

50

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сетки частот | 1988 |

|

SU1656674A1 |

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

| Многоканальный генератор серии задержанных импульсов | 1987 |

|

SU1800595A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

Изобретение может быть использовано в синхронизаторах, управляющих и вычислительных системах. Цель изобретения - повышение точности задания временного положения импульсов в серии и расширение функциональных возможностей, которая достигается за счет введения блока 5 элементов совпадений и получения на выходе блока 3 сравнения кодов серий импульсов, синхронизированных с импульсами на выходе опорного генератора 6. В блоке 2 памяти кодов задержек хранятся коды, которые определяют временное положение серий импульсов и номера каналов, на выходе которых пройдут эти серии. Устройство также содержит блок 1 управления, счетчик 4, шину 7 запуска, выходную шину 8. 3 ил.

CS

Фаа.З

Составитель Ю,Сибиряк Редактор И.Касарда Техред М.Ходанич

Заказ 7241/53

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

fia.l

Корректор И,Пуска

Подписное

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-30—Публикация

1987-11-10—Подача