(21)4415274/24-21

(22)25.02.88

(46) 30.11.89. Бюл. № 44

(71)Московский инженерно-физический институт

(72)Ю.И. Бочаров, А.А. Лебедев, Н.А. Самотаев и В.П. Солдатов

(53)621.374.33(088.8)

(56)Кондалев А.И. Системные преобразователи формы информации. К.: Науко- ва думка, 1974, с. 249.

(54)КОМПАРАТОР НАПРЯЖЕНИЙ

(57)Изобретение относится к импульсной технике и может быть использовано в радиоизмерительной аппаратуре, в аналого-цифровых преобразователях. Целью изобретения является повьшение быстродействия. Цель изобретения - достигается тем, что в компараторе, содержащем последовательно соединенные ограничитель 1 входного разностного сигнала, первый и второй дифференциальные каскады 2, 4, блок 4 сдвига уровня и триггера-защелки 5, в ограничитель 1 входного разностного сигнала введены пятый, шестой, седьмой, восьмой и девятый транзисторы 14-17, третий источник 19 тока и конденсатор 20, что позволило значительно увеличить режимные токи во время формирования фронта сигнала при малых статических значениях этих токов и тем самым уменьшить время восстановления, обеспечивающее повышение быстродействия. того, ограничитель 1 входного сигнала содержит первый, второй, третий и четвертый транзисторы 6-9, два источника 10, 11 тока и две шины 21, 22. 2 ил.

i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для хранения и выборки информации | 1981 |

|

SU982096A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Стереодекодер для системы стереофонического радиовещания с полярной модуляцией | 1991 |

|

SU1748269A1 |

| Операционный усилитель | 1983 |

|

SU1160530A1 |

| Дифференциальный усилитель | 1987 |

|

SU1501256A1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Балансный модулятор | 1980 |

|

SU904197A1 |

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Усилитель | 1980 |

|

SU987795A1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ПАРАЛЛЕЛЬНЫЙ ТРОИЧНЫЙ КОМПАРАТОР | 2020 |

|

RU2723672C1 |

Изобретение относится к импульсной технике и может быть использовано в радиоизмерительной аппаратуре, в аналого-цифровых преобразователях. Целью изобретения является повышение быстродействия. Цель изобретения достигается тем, что в компараторе, содержащем последовательно соединенные ограничитель 1 входного разностного сигнала, первый и второй дифференциальные каскады 2,4, блок 3 сдвига уровня и триггера-защелки 5, в ограничитель 1 входного разностного сигнала введены пятый, шестой, седьмой, восьмой и девятый транзисторы 14 - 17, третий источник 19 тока и конденсатор 20, что позволило значительно увеличить режимные токи во время формирования фронта сигнала при малых статических значениях этих токов и тем самым уменьшить время восстановления, обеспечивающее повышение быстродействия. Кроме того, ограничитель 1 входного сигнала содержит первый, второй, третий и четвертый транзисторы 6 - 9, два источника 10,11 тока и две шины 21, 22. 2 ил.

ел го

СП

оЬ со

I 1 I I /

Изобретение относится к импульсной технике и может быть использовано в радиоизмерительной аппаратуре, в микросхемах аналого-цифровых преобразователей с низковольтным питанием .

Цель изобретения - повышение быстродействия компаратора за счет уменьшения времени восстановления.

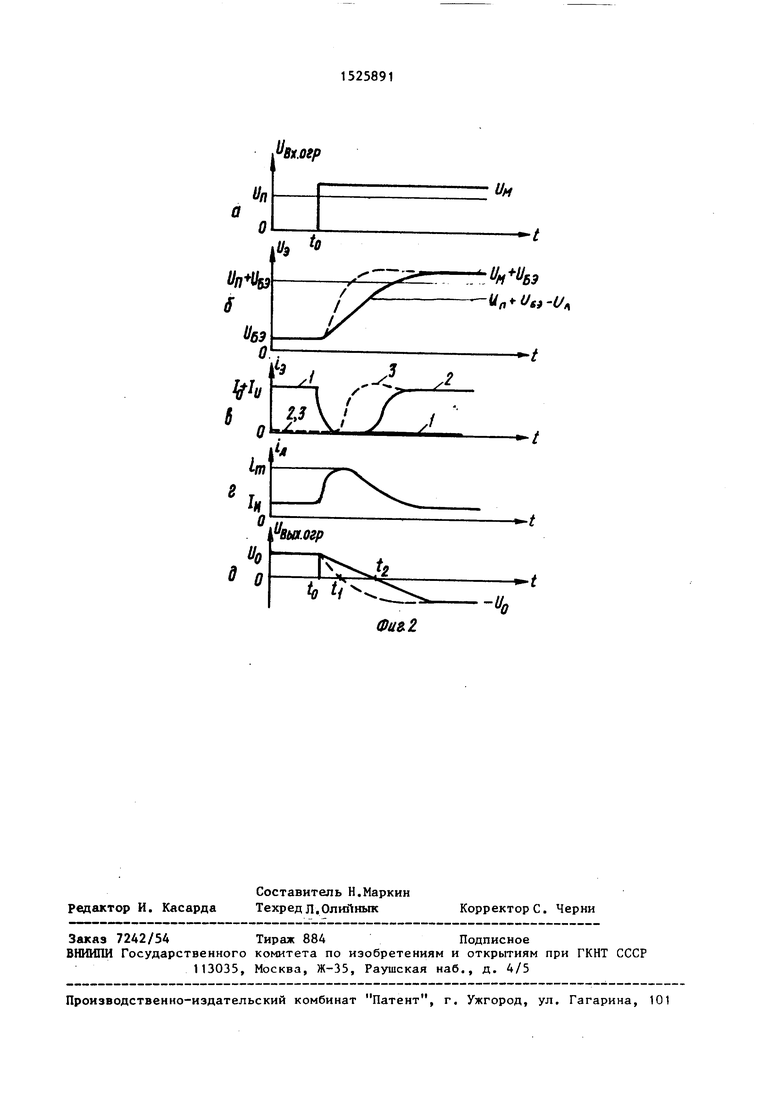

На фиг. 1 представлена структурно принщшиальная схема компаратора напряжений; на фиг. 2 - временные раммы, поясняюпше работу компаратора

Компаратор напряжений содержит последоватепьно включенные ограничитель 1 входного разностного сигнала, первый усилительный дифференциальный каскад 2, блок 3 сдвига уровня, второй усилительный дифференциальный каскад 4 и триггер-защелку 5. Ограничитель 1 входного сигнала содержит первый, второй, третий и четвертый биполярные транзисторы 6-9 одного типа проводимости и два источника 10 и 11 равных токов. Причем геометрические размеры первого и четвертого, второго и третьего транзисторов 6-9 попарно равны, а площади эмиттеров первого и четвертого транзисторов 6 и 9 отличаются от площадей эмиттеров второго и третьего транзисторов 7 и 8. Эмиттеры первого и второго, третьего и четвертого транзисторов 6-9 попарно объединены и подключены симметрично к источникам 10 и 11 тока, а базы первого и третьего, второго и четвертого транзисторов 6-9 попарно объединены и являются входами 12 и 13 компаратора.. При этом в ограничитель 1 входного разностного сигнала.дополнительно введены пятый, шестой, седьмой, восьмой.и девятьш транзисторы 14-18, третий источник 19 тока и конденсатор 20, так что типы проводимости пятого и шестого транзисторов 14 и 15 противоположны, а седьмого, восьмого и девятого транзисторов 16-18 соответствуют типам проводимости первых четырех транзисторов. При этом эмиттеры пятого и шестйго транзисторов 14 и 15 объединены и подключены к третьему источнику 19 тока и одной из обкладок ковденсатора 20, другая обкладка которого соединена с первой папюй 21 питания. Коллекторы пятого и шестого транзисторов 14 и 15 объединены и подключены к базам

0

5

0

5

0

5

0

5

0

5

седьмого, восьмого и девятого транзисторов 16-18, эмиттеры которых соединены с второй шиной 22 питания противоположной полярности. Причем коллектор седьмого транзистора 16 подключен к базе пятого 14 и эмиттерам первого и второго транзисторов 6 и 7. Коллектор восьмого транзистора 17 подключен к базе шестого 15 и эмиттерам третьего 8 и четвертого 9 транзисторов, а коллектор девятого транзистора 18 соединен с его базой.

Устройство работает следующим образом.

При быстрых изменениях входного сигнала, когда быстродействие известного компаратора ограничивается из- за малой величины токов I, (которыми перезаряжаются паразитные емкости в схеме), в предлагаемом устройстве дополнительно введенные элементы позволяют добиться значительного увеличения режимных токов во время формирования фронтов сигнала при сохранении малых статических значений этих токов, равных

1о + 1„, где 1 ток третьего источника.

Действительно, пусть на вход 12 компаратора подано постоянное U напряжение перегрузки (фиго 2 а), а на вход 13 компаратора в момент времени t - перепад напряжения амплитудой и. Одновременно с переходом транзисторов 6 и 8 в режим отсечки перепад входного напряжения передается на базы транзисторов 14 и 15, находящихся в активном режиме. Благодаря наличию конденсатора 20, который для быстрых (высокочастотных) составляющих входного сигнала имеет малое сопротивление, суммарный коллекторный ток i транзисторов 14 и 15 во время формирования фронта может в несколько раз превысить статическое значение

1„(Р) - 1,(1 ).

где р - оператор Лапласа-Карсона; С - величина емкости конденсатора; температурный потенциал.

При этом перезаряд паразитных емкостей в процессе перехода транзисторов 7 и 9 в активный режим осуществляется токами источников 10

и 11 и коллекторными токами транзисторов 16 и 17. Следовательно, значение задержки ограничителя в предлагаемом устройстве составляет СП(УП-УА)

Н Г,

где и - диапазон линейной работы дифференциального каскада.

и л ±2 гСравнение величин задержек прототипа и предлагаемого устройства при условии i IQ (это обеспечивается соответствующим выбором параметров схемы) позволяет сделать вывод, что в предлагаемом устройстве возможно достичь большего быстродействия, чем в прототипе благодаря уменьшению времени восстановления.

На фиг. 2б показаны временные диараммы формирования фронта сигналов на эмиттерах транзисторов в схеме прототипа (сплошная линия) и в предлагаемом устройстве - пунктирная линия. На фиг. 2 в показаны временные диаграммы изменения эмиттерных токов транзисторов 6 и 8 (кривая 1) и 7 и 9 (кривая 2 и 3) для прототипа и предлагаемой схемы. На фиг. 2 г показана временная диаграмма изменения коллекторных токов транзисторов 16 и 17. На фиг. 2 д показаны временные диаграммы разностного сигнала выхода схемы ограничителя, используемой в прототипе, и в предлагаемом устройстве (соответственно сплошная и пунктирная линии).

Формула изобретения

Компаратор напряжений, содержащий последовательно включенные ограничитель входного разностного сигнала, первый усилительный дифференциальный каскад, блок сдвига уровня, второй усилительный дифференциальный каскад и триггер- защелку, а ограничитель входного разностного сигнала

0

содержит первый, второй, третий и четвертый биполярные транзисторы одного типа проводимости и два источника равных токов, причем геометрические размеры первого и четвертого, второго и третьего транзисторов попарно равны, а площади эмиттеров первого и четвертого транзисторов отличаются от площадей эмиттеров второго и третьего транзисторов, коллекторы всех транзисторов соединены с шиной питания, эмиттеры первого и второго, третьего и четвертого 5 транзисторов попарно объединены и подключены симметрично к источникам тока, а базы первого и третьего, второго и четвертого транзисторов попарно объединены и являются входами компаратора, отличающий с тем, что, с целью повьш1ен ш быстродействия, в ограничитель входного разностного сигнала дополнительно введены пятый, щестой, седьмой, восьмой и девятьй транзисторы, третий источник тока и ковденсатор, при этом типы проводимости пятого и шестого транзисторов противоположны, а седьмого, восьмого и девятого транзисторов соответствуют типам проводимости первых четырех транзисторов, эмиттеры пятого и шестого транзисторов объединены и подключены к третьему источнику тока и одной из обкладок конденсатора, другая обкладка кото0

5

0

5

0

5

я

рого соединена с первой шиной, а коллекторы пятого и шестого транзисторов объединены и подключены к базам седьмого, восьмого и девятого транзисторов, эмиттеры которых соединены с второй Iшiнoй питания противоположной полярности, причем коллектор седьмого транзистора подключен к базе пятого и эмиттерам первого и второго транзисторов, коллектор восьмого транзистора подключен к базе шестого и эмиттерам третьего и четвертого транзисторов, а коллектор девятого транзистора соединен с его базой.

(

Авторы

Даты

1989-11-30—Публикация

1988-02-25—Подача