(21)А369879/2А-21

(22)17.12.87

(46) 15.12.89. Бюл. 46 (72) Ю.А.Глухов

(53)621.317.77(088.8)

(56)Авторское свидетельство СССР 788023, кл. G 01 R 25/00, 1978.

(54)УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТЕКУЩЕЙ ФАЗЫ

(57)Изобретение относится к устрой- ствам выделения текущей фазы случайных детерминированных процессов и может быть использовано для исследования закономерностей изменения во времени текущей фазы прямых и рассеянных сигналов пассивной и активной радиолокации и гидролокации. Целью изобретения является распшрение

диапазона рабочих частот. Текущая фаза с дискретностью S /2 регистрируется в многоразрядном реверсивном счетчике 13, изменение кода которого пропорционально изменению текущей фазы во времени. Изменение текущей фазы на угол 5Г/2 определяется индикаторами 9 и 10, Устройство дополиительно содержит генератор 1 синусоидального напряжения, фазовращатель 2, перемножители 3 и 4, фильтры 5 и.6 низкой частоты, компараторы 7 и 8, логические элементы ИЛИ П и 12. Устройство легко сопрягается со стандартными вычислительными средствами и охватывает широкий диапазон рабочих частот, включая СВЧ-диапазон, 2 з.п. ф-лы, 4 ил.

г

Изобретение относится к устройствам выделения текущей фазы случайных детермшшрованных процессов и может быть использовано для исследования закономерностей изменения во времени текущей фазы прямых и рассеянных сигналов пассивной и активной радиолокации и гидролокации.

Цель изобретения - расширение диа пазона рабочих частот.

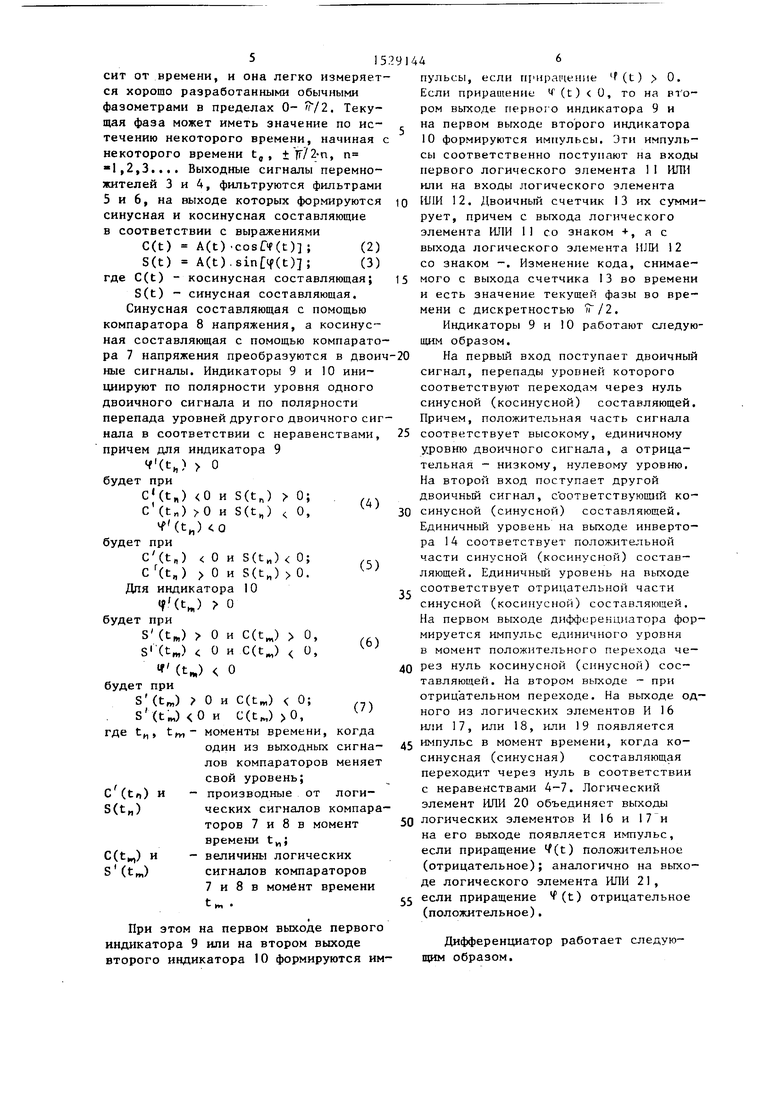

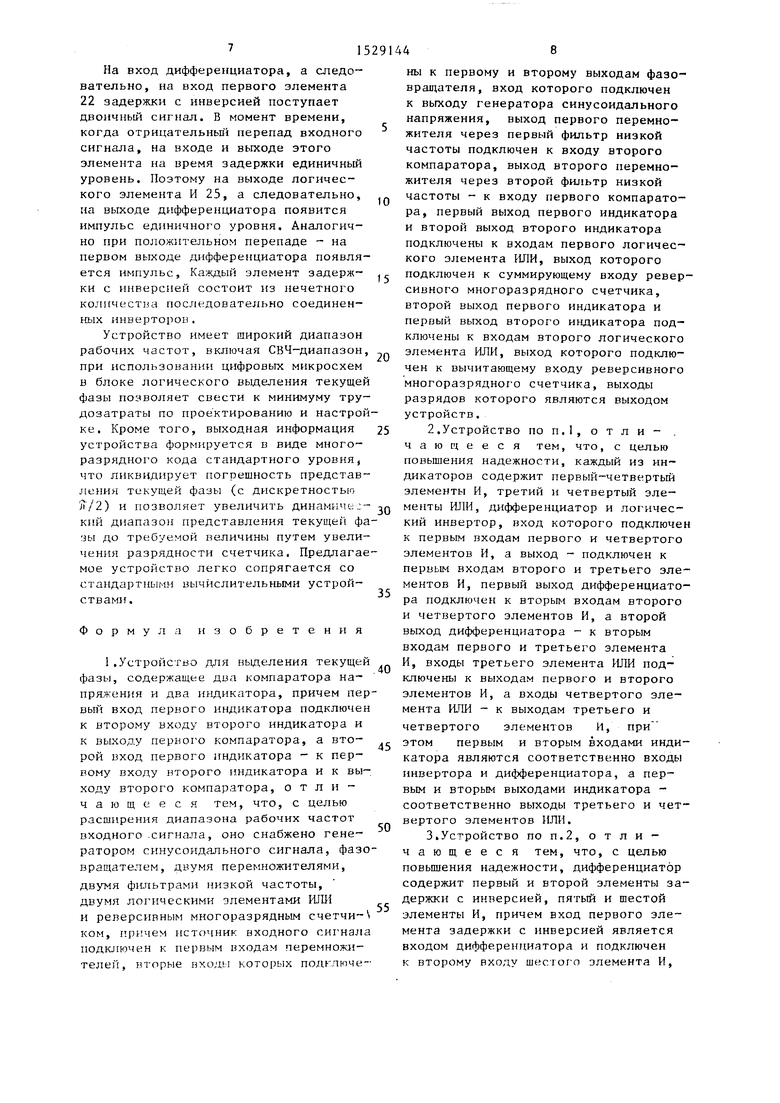

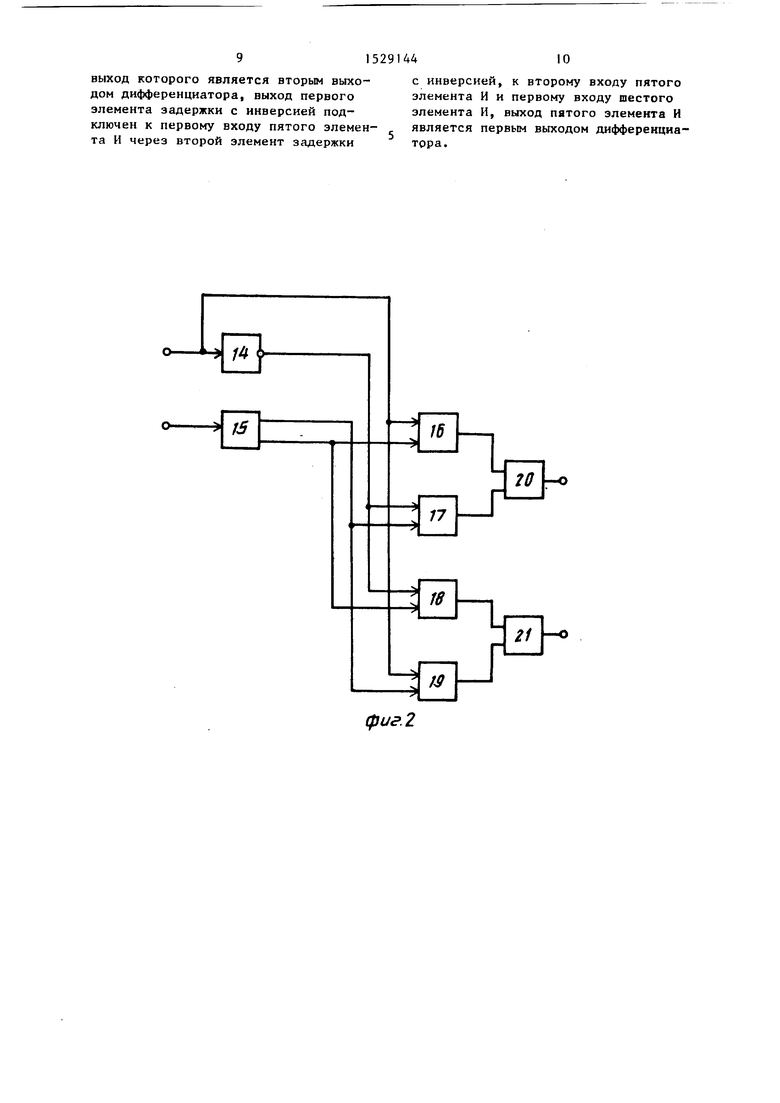

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - схема индикатора; на фнг.З - схема дифференциатора; на фиг,4 - эпюры напряжений, поясняющие работу дифференциатора.

Устройство содержит генератор 1 синусоидального напряжения, фазовращатель 2, первый 3 и второй 4 пере- множителп, первый и второй фильтры 5 и 6 низкой частоты, первый 7 и второй 8 компараторы напряжения, первый 9 и второй 10 индикаторы, первый 11 и BTopoii 12 логические элементы ИЛИ, многоразрядный реверсивный счетчик 13, Каждый нз индикаторов содержит логический инвертор 14, дифференциатор 15, первый 16 и второй 17, третий 18 и четвертый 19 логические элементы И, третий 20 и четвертый 21 логические элементы ИЛИ, Дифференциатор содержит первый 22 и второй 23 элементы задержки с инверсией, пятый 24 и тестой 25 логические эле- менты И,

Входной сигнал устройства подключен к nepBbLM входам перемножителей 3 и 4, вторые входы которых подключены к первому и второму выходам фазовращателя 2, вход которого подключен к выходу генератора 1, Выход перемножителя 3 через последовательно подключенные фильтр 5 и компаратор 8 подключен к второму входу индикатора 9 и к первому входу индикатора 10, Выход перемножителя 4 через последовательно подключенные фильтр 6 и компаратор 7 подключен к первому входу индикатора 9 и к вто- рому входу индикатора 10, Первый выход индикатора 9 и второй выход индикатора 10 подключены к входам логического элемента ИЛИ 11, выход которого подключен к суммирующему вхду счетчика 13, Второй выход индикатора 9 и первый выход индикатора 10 подключены к входам логического элемента ИЛИ 12, выход которого подключен к вычитающему входу счетчика .13, Выход счетчика 13 является выходом устройства.

Первый вход каждого индикатора 9 и 10 подключен к входу логического инвертора 14 и к первым входам логических элементов И 16 и 19, Второй вход каждого индикатора 9 и 10 подклчен к входу дифференциатора 15, первый выход которого подключен к вторым входам логических элементов И 17 и 19, а второй выход - к вторым входам логических элементов И 16 и 18. Выход логического инвертора 14 подклчен к первым входам логических элеметов И 17 и 18, Выходы логических элементов И 16 и 17 подключены к входам логического элемента ИЛИ 20, выходы логических элементов И 18 и 19 подключены к входам логического элемента ИЛИ 21, Выход логического элемента Ш1И 20 является первым выходом, а выход логического элемента ИЛИ 21 - вторым выходом каждого инвертора 9 и 10, Вход дифференциатора 15 подключен ко входу элемента 22 задержки и к второму входу логического элемента И 25.,Выход элемента 22 задержки подключен через элемент 23 задержки к первому входу логического элемента И 24, ко второму входу этог же элемента и к первому входу логичекого элемента И 25, Выход логического элемента И 24 является первым выходом, а выход логического элемента И 25 - вторым выходом дифферен- циатора 15,

Устройство работает следующим образом.

На вход фазовращателя 2 от генератора 1 поступает синусоидальный сигнал с частотой , На первом и втором выходах фазовращателя 2 формируются два синусоидальных сигнала с частотой UJ , сдвинутые относительно друг друга по фазе л/2, и эти сигналы поступают соответственно на вторые входы первого 3 и второго 4 перемножителей. На первые входы пе ремножителей 3 и 4 поступает входной сигнал с средней частотой GJo

U(t) A(t) sin :u;ot-t-(/ (t) , где A(t) - огибающая сигнала;

средняя частота; (t) - текущая фаза; tfg - начальная фаза.

Начальная фаза в дальнейшем не рассматривается, так как она не зави

сит от времени, и она легко измеряется хорошо разработанными обычными фазометрами в пределах О- /2. Текущая фаза может иметь значение по истечению некоторого времени, начиная некоторого времени t, , ± f/2;n, п 1,2,3.... Выходные сигналы перемножителей 3 и 4, фильтруются фильтрами 5 и 6, на выходе которых формируются синусная и косинусная составляющие в соответствии с выражениями

C(t) A(t).cosC f(t); (2)

S(t) A(t).sin/:cf(t); (3) где C(t) - косинусная составляющая;

S(t) - синусная составляющая. Синусная составляющая с помощью компаратора 8 напряжения, а косинусная составляющая с помощью компаратора 7 напряжения преобразуются в двои ные сигналы. Индикаторы 9 и 10 инициируют по полярности уровня одного двоичного сигнала и по полярности перепада уровней другого двоичного сигнала в соответствии с неравенствами, причем для индикатора 9

(t,) О будет при

C (tJ 0 и S(tJ 0;

С (tn) 0 и S(t,) О,

(tj о будет при

C (t,) О и S(tJ 0;

С (1„) О и S(tJ 0. Для индикатора 10

f (t) О будет при

S (t) О и C(tJ О,

s Xt) о и c(tJ о, (t J о

будет при

S (tm) О и C(t„) 0; S (tJ 0 и C(tJ 0, где t, t - моменты времени, когда один из выходных сигналов компараторов меняет свой уровень;

-производные от логических сигналов компараторов 7 и 8 в момент времени

-величины логических сигналов компараторов

7 и 8 в момент времени t .

(4)

(5)

(6)

(7)

C Ctr.) и

s(tj

C(t,) и

s4tj

При зтом на первом выходе первого индикатора 9 или на втором выходе второго индикатора 10 формируются им10

15

-2025

пульсы, если приращение f(t) 0. Если приращение Ч (t) О, то на вТо- ром выходе первого индикатора 9 и на первом выходе второго индикатора 10 формируются импульсы. Эти импульсы соответственно поступают на входы первого логического злемента 1I ИЛИ или на входы логического элемента ШШ 12. Двоичный счетчик 13 их суммирует, причем с выхода логического элемента ИЛИ И со знаком -, а с выхода логического элемента Шй 12 со знаком -. Изменение кода, снимаемого с выхода счетчика I3 во времени и есть значение текущей фазы во времени с дискретностью ,

Индикаторы 9 и 10 работают следующим образом.

На первый вход поступает двоичный сигнал, перепады уровней которого соответствуют переходам через нуль синусной (косинусной) составляющей. Причем, положительная часть сигнала соответствует высокому, единичному уровню двоичного сигнала, а отрицательная - низкому, нулевому уровню. На второй вход поступает другой двоичный сигнал, сЪответствующий ко30 синусной (синусной) составляющей. Единичный уровень на выходе инвертора 14 соответствует положительной части синусной (косинусной) составляющей. Единичный уровень на выходе соответствует отрицательной части синусной (косинусной) составляющей. На первом выходе дифференциатора формируется импульс единичного уровня в момент положительного перехода че-

40 рез нуль косинусной (синусной) составляющей. На втором выходе - при отрицательном переходе. На выходе одного из логических элементов И 16 или 17, или 18, или 19 появляется

д5 импульс в момент времени, когда косинусная (синусная) составляющая переходит через нуль в соответствии с неравенствами 4-7. Логический элемент ИЛИ 20 объединяет выходы

50 логических элементов И 16 и 17 и на его выходе появляется импульс, если приращение /(t) положительное (отрицательное); аналогично на выходе логического элемента ИЛИ 21,

55 если приращение (t) отрицательное (положительное).

Дифференциатор работает следующим образом.

35

715

На вход дифференциатора, а следовательно, на вход первого элемента 22 задержки с инверсией поступает двоичный сигнал. В момент времени, когда отрицательньш перепад входного сигнала, на входе и выходе этого элемента на время задержки единичный уровень. Поэтому на выходе логического элемента И 25, а следовательно, на выходе дифференциатора появится импульс единичного уровня. Аналогично при положительном перепаде - на первом выходе дифференциатора появляется импульс. Каждый элемент задерж- кн с инверсией состоит из нечетного количеств последовательно соединенных инверторов.

Устройство имеет широкий диапазон рабочих частот, включая СВЧ-диапазон, при использовании цифровых микросхем в блоке логического выделения текущей фазы позволяет свести к минимуму трудозатраты по проектированию и настройке. Кроме того, выходная информация устройства формируется в виде многоразрядного кода стандартного уровня, что ликвидирует погрешность представления текущей фазы (с дискретностью iT/2) и позволяет увеличить динамкче:- кий диапазон представления текуп1ей фазы до требуемой величины путем увеличения разрядности счетчика, Предлагаемое устройство легко сопрягается со стапдаргными вычислительными устройствами.

Формула изобретения

1.Устройство для выделения текущей

фазы, содержащее два компаратора напряжения и два индикатора, причем первый вход первого индикатора подключен к второму входу второго индикатора и к выходу первого компаратора, а вто- рой вход первого индикатора - к первому входу второго индикатора и к выходу второго компаратора, отличающееся тем, что, с целью расширения диапазона рабочих частот входного .сигнала, оно снабжено генератором синусоидального сигнала, фазовращателем, двумя перемножителями, двумя фильтрами низкой частоты, двумя логическими элементами ИШ и реверсивным многоразрядным счетчи- ком, причем источник входного сигнала подключен к первым входам перемножителей, вторые входы которых подключе

8

0

5 Q

0

5

0

0

ны к первому и второму выходам фазовращателя, вход которого подключен к выходу генератора синусоидального напряжения, выход первого перемно- жителя через первый фильтр низкой частоты подключен к входу второго компаратора, выход второго перемножителя через второй фильтр низкой частоты - к входу первого компаратора, первый выход первого индикатора и второй выход второго индикатора подключены к входам первого логического элемента ИЛИ, выход которого подключен к суммирующему входу реверсивного многоразрядного счетчика, второй выход первого индикатора и первый выход второго индикатора подключены к входам второго логического элемента ИЛИ, выход которого подключен к вычитающему входу реверсивного многоразрядного счетчика, выходы разрядов которого являются выходом устройств.

2.Устройство по п,1, о т л и - чающееся тем, что, с целью повьшения надежности, каждый из индикаторов содержит первый-четвертый элементы И, третий и четвертый элементы ИЛИ, дифференциатор и логический инвертор, вход которого подключен к первым входам первого и четвертого элементов И, а выход - подключен к первым входам второго и третьего элементов И, первый выход дифференциатора подключен к вторым входам второго и четвертого элементов И, а второй выход дифференциатора - к вторым входам первого и третьего элемента И, входы третьего элемента ИЛИ подключены к выходам первого и второго элементов И, а входы четвертого элемента ИЛИ - к выходам третьего и четвертого элементов И, при этом первым и вторым входами индикатора являются соответственно входы инвертора и дифференциатора, а первым и вторым выходами индикатора - соответственно выходы третьего и четвертого элементов ИЛИ.

3,Устройство по п.2, отличающееся тем, что, с целью повьщ1ения надежности, дифференциатор содержит первый и второй элементы задержки с инверсией, пятый и шестой элементы И, причем вход первого элемента задержки с инверсией является входом дифференциатора и подключен к второму входу шестого элемента И,

выход которого является вторым выходом дифференциатора, выход первого элемента задержки с инверсией подключен к первому входу пятого элемента И через второй элемент задержки

1529U410

с инверсией, к второму входу пятого элемента И и первому входу шестого элемента И, выход пятого элемента И является первым выходом дифференциатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С ДВУХКРАТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 1991 |

|

RU2007886C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| ДАТЧИК ЧАСТОТЫ ВРАЩЕНИЯ РОТОРА МАШИНЫ ПЕРЕМЕННОГО ТОКА | 1994 |

|

RU2085953C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| ГЛОБАЛЬНО ЛИНЕАРИЗОВАННАЯ СИСТЕМА СИНХРОНИЗАЦИИ | 2014 |

|

RU2554535C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

Изобретение относится к устройствам выделения текущей фазы случайных детерминированных процессов и может быть использовано для исследования закономерностей изменения во времени текущей фазы прямых и рассеяных сигналов пассивной и активной радиолокации и гидролокации. Целью изобретения является расширение диапазона рабочих частот. Текущая фаза с дискретностью φ/2 регистрируется в многоразрядном реверсивном счетчике 13, изменение кода которого пропорционально изменению текущей фазы во времени. Изменение текущей фазы на угол φ/2 определяется индикаторами 9 и 10. Устройство дополнительно содержит генератор 1 синусоидального напряжения, фазовращатель 2, перемножители 3 и 4, фильтры 5 и 6 низкой частоты, компараторы 7 и 8, логические элементы ИЛИ 11 и 12. Устройство легко сопрягается со стандартными вычислительными средствами и охватывает широкий диапазон рабочих частот, включая СВЧ-диапазон. 2 з.п. ф-лы, 4 ил.

фиг. 2

/

-o

(ffLfe.3

-(/г4

Авторы

Даты

1989-12-15—Публикация

1987-12-17—Подача