f

изобретение относится к вычислительной технике и может быть использовано при отладке программ вычислительной системы в реальном масштабе времени.

Целью изобретения является повышение быстродействия при отладке программ.

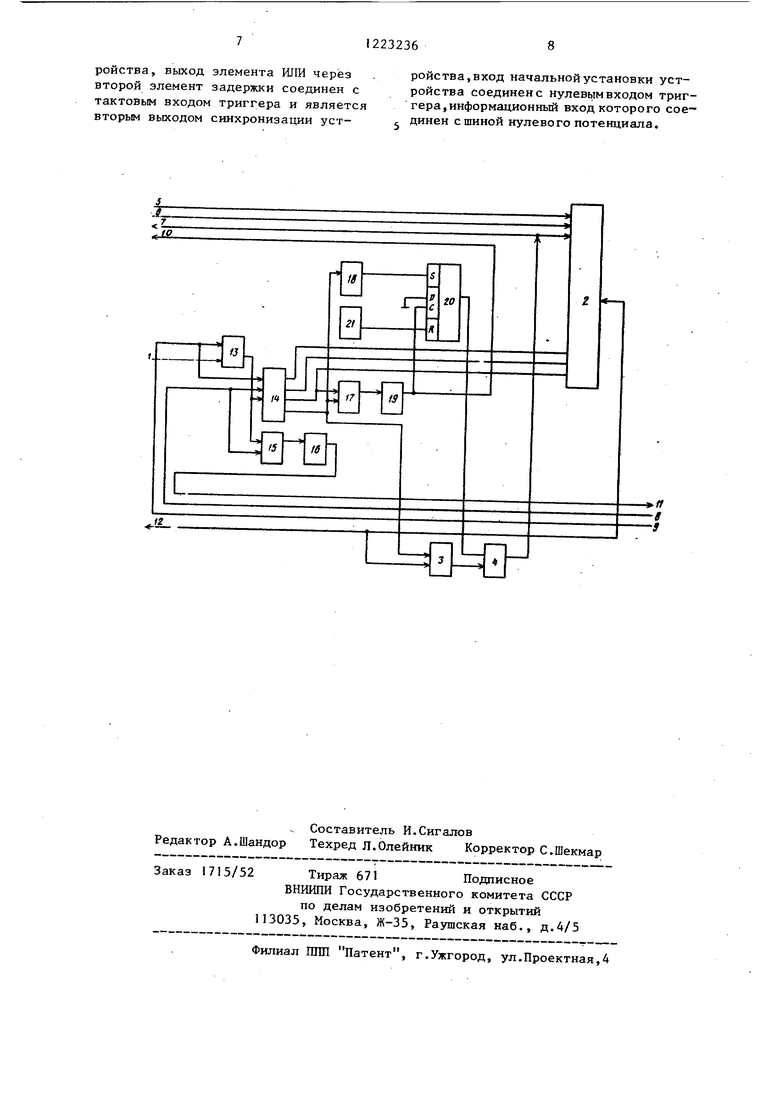

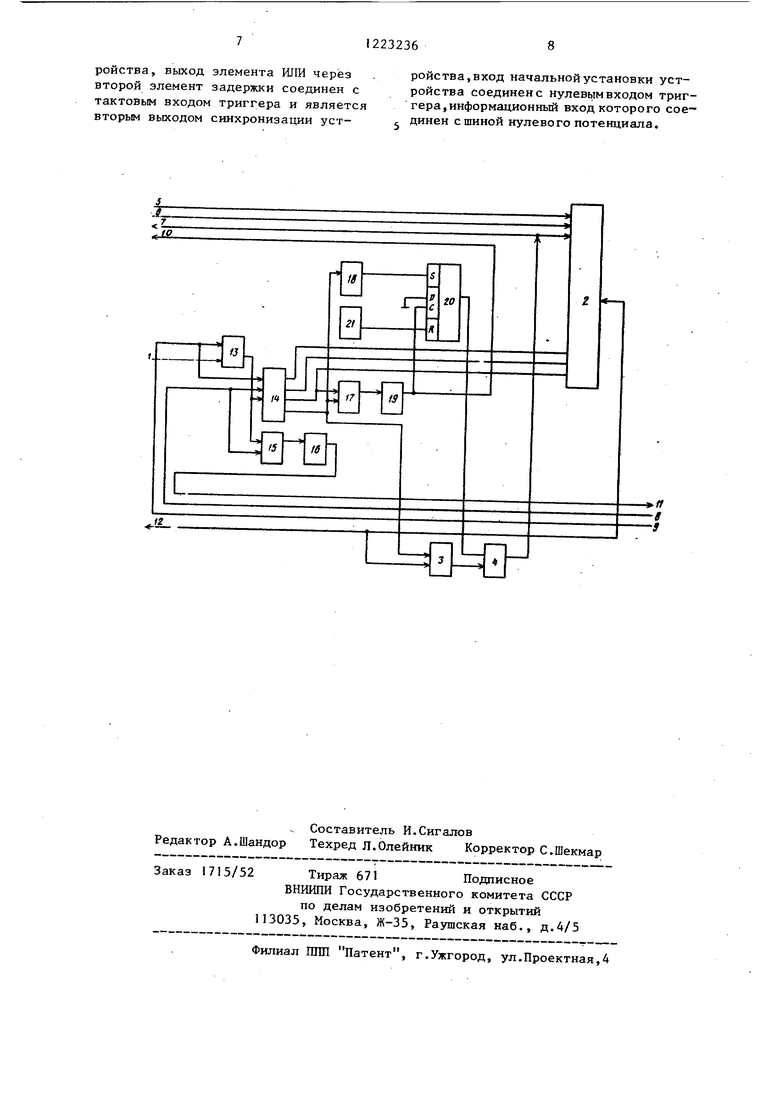

На чертеже представлена структурная схема устройства для отладки программ,.

Устройство содержит вход 1 установки начального адреса, мультиплексор- 2, регистр 3, группу 4 элементов И, первую и вторую группы информационных входов 5 и 6 соответственно, первый информационньй выход 7 устройства, первый тактовьй вход 8 устройства, адресный вход 9 устройства, выходы 10 и 11 синхронизации устройства, второй информационный выход 12 устройства, схему 13 сравнения, дешифратор 14, элемент И 15, первый элемент 16 задержки, второй элемент ИЛИ. 17, формировател 18 КОРОТКОГО импульса (ФКИ), второй элемент 19 задержки, триггер 20, вход 21 начальной установки.

Сигналом Начальная установка, который поступает по входу 21 при включении питания, одиночньй импуль с выхода схемы Начальная установка поступает на R-вход триггера 20 и устанавливает его в нулевое состоя- .ние.

На группу входов схемы 13 сравнения записьшается определенный код, соответствующий номеру, присвоенном устройству отладки программ. По первому входу устройства на другую группу входов схемы 13 сравнения поступают старшие разряды адреса, которые сравниваются с кодом, присвоенным устройству отладки програм При сравнении с вьгкода схемы 13 сравнения поступает сигнал, разрешающий работу дешифратора 14 (на третий вход дешифратора 14) и элемента И 15.

По первому входу устройства на вход дешифратора 14 поступают младшие разряды адреса, по выходу 11 устройства на вход дешифратора 14 поступают разрядь шины управления. При поступлении на дешифратор 14 совокупности сигналов: младших разрядов адреса, разрядов управления и сигнала со схемы 13 сравнения, в

232362

зависимости от кода, поступившего на вход дешифратора 14, возбуждается один из выходов дешифратора 14.

Поступающий код может быть четы5 рех типов. В соответствии с описанной ниже работой устройства отладки программ обозначим каждый из кодов символами: а , Б , иг. При поступлении на вход дешифратора 14

10 кода а возбуждается первый выход дешифратора. При поступлении кода возбуждается второй выход дешифратора 14. Код 6 возбуждает третий выход дешифратора 14, который подклю15 чен к первому входу элемента ИЛИ 17. Код ъ возбуждает четвертый выход дешифратора 14, который подключен к второму входу элемента ИЛИ 17 и к входу формирователя 18 короткого

20 импульса. Выход последнего подключен к установочному входу S-тригге- ра 20. Выход элемента ИЛИ I7 подключен к входу элемента 19 задержки,, выход которого подк/1ючен к синхро25 визирующему входу С-триггера 20. На информационный вход Г -триггера 20 подается логический О. Наличие сигналов на установочном S и синхронизирующем С входах триггера 20

30 перебрасьшает триггер 20 в единичное состояние. Выход элемента 19 задерж- - ки является вьгходом 10 блока сравнения .

По входу 8 устройства на элемент И 15 подается тактовьй сигнал. Работу элемента И 15 разрешает сигнал со схемы 13 сравнения. С выхода эле- мента И 15 сигнал поступает на вход элемента 16 задержки.

4Q Мультиплексор 2 обеспечивает коммутацию информации, поступающей с первой, второй групп информационных входов (5 и 6) и с первого информационного выхода 7 устройства, на

45 второй информационньй выход 12 устройства под управлением сигналов, поступающих с дешифратора 14.

Регистр 3 предназначен для сохранения информации на время ее

передачи через группу 4 элементов И на первьй информационный выход 7. Группа 4 элементрв И необходима для согласования информационных выходов регистра 3 с первым информационным

выходом 7 устройства.

Для отладки программ к устрой- cjTsy подсоединяются мини-ЭВМ (мик35

3

ро-ЭВМ) и отлаживаемый вычислитель следующим образом.

Адресная шина мини-ЭВМ подсоединяется к группе адресных входов 9 устройства, управляющие сигналы - к входу 8 и выходу 11 устройства, шина данных - к второму информационному выходу 12 устройства.

Шины адреса и управления (сигналы чтение/запись, СИЛ - синхроим- пульс активного устройства) отлаживаемого вычислителя подсоединяются к первой и второй группам информационных входов 5 и 6 устройства соответственно, шина данньк подсоединяется к первому информационному выходу 7 устройства, линия сигнала СИП (синхроимпульс пассивного устройства) - к выходу 10 устройства.

Устройство работает следующим образом.

Отлаживаемый вычислитель в соответствии с организацией своего интерфейса, т.е. шина адреса,шина управления (сигналы чтение/запись, СИА) и шина данных подсоединяются к первой и второй группам информационных входов 5 и 6 и выходу 7 устройства соответственно. Шина 7 уст- ройства - двунаправленная. Выход

10устройства являе гся линией сигнала СИП для отлаживаемого вьмислите- ля.

Мини-ЭВМ (микро-ЭВМ), применяемая для отлаживания вычислителя, в соответствии с организацией своего интерфейса подсоединяется своей адресной шиной к группе адресных входов устройства для отладки программ, шиной управления к группе управляющих входов 8 и первому управляющему выходу

11(сигнал СХИ - синхроимпульс исполнителя) устройства, шиной данных к двунаправленной информационной шине 12 устройства.

Работа устройства для отладки программ начинается с того, что мини-ЭВМ (микро-ЭВМ) выставляет по своей адресной шине, т.е. на вход 9 устройства, код и сигнал синхронизации на вход 8 устройства СХЗ (синхроимпульс задатчика). При анализе этих сигналов дешифратор 14 вы- рабатьшает управляющие сигналы, определяемые кодом, поступившим от мини-ЭВМ (микро-ЭВМ).

Мини-ЭВМ (микро-ЭВМ) в начале читает шину управления отлаживаемого

23236

вычислителя. Для этого мини-ЭВМ (микро-ЭВМ) подает на входы один и два блока сравнения соответствующий : код. По этому коду вырабатьшается

5 сигнал с третьего выхода дешифратора 14, поступающий на второй управляющий вход мультиплексора 2, в результате чего происходит коммутация шины управления отлаживаемого вычислителя

10 (второй группы информационных входов 6 устройства) на шину данных мини- ЭВМ (вторую двунаправленную информационную шину I2 устройства), После окончания переходных процессов в

15 мультиплексоре 2 дешифратором 14 по первому выходу на выход 11 устройства выдается сигнал синхронизации СХИ. Мини-ЭВМ при получении сигнала СХИ считывает информацию, поступаю-

20 Щую на ее шину данных, снимает сигнал СХЗ с шины 8, а затем выставленный код с шины адреса, .т.е. с шины 9. Мини-ЭВМ анализирует полученную информацию. Если отлаживаемый вы25 числитель выставил на шину управления сигнал чтение/запись, то необходимо проанализировать адрес, по которому производится эта операция. Происходит следующее. Мини-ЭВМ

30 выставляет по шинам 8 и 9 сигнал СХЗ и соответствующий код на вход дешифратора 14. С второго выхода дешифратора 14 по этому коду выраба- , тьюается сигнал, поступаюиа1й iia первый вход- мультиплексора 2, в результате происходит коммутация шины адреса отлаживаемого вычислителя (первой группы информационных входов 5 устройства) на шину данных мини-ЭВМ вторую двунаправленную . информационную шину 12 устройства). После окончания переходных процессов в мультиплексоре 2.дешифратором 14 выдается сигнал синхронизации СХИ. Мини-ЭВМ при получении сигнала СХИ считьшает информацию, поступающую на ее шину 12 данных; снимает сигнал СХЗ по шине 8, снимает вы-; ставленный код с шины 9 адреса. Мини-ЭВМ анализирует полученный ад35

40

45

50

рес.

Если требуется произвести операцию записи по полученному адресу, то: мини-ЭВМ выставляет по шинам 8 и 9 сигнал СХЗ и соответствующий код на вход дешифратора 14. С четвертого выхода дешифратора 14 вырабатьшается сигнал, поступающий

на третий вход мультиплексора 2, в результате чего происходит коммутация (через мультиплексор 2) пшны данных отлаживаемого вычислителя (первой двунаправленной шины 7 устройства) на шину данных мини-ЭВМ (вторую двунаправленную информационную пшну 12 устройства). После окончания переходных процессов в мультиплексоре 2 элемент ИЛИ 17 через второй элемент задержки выдает сигнал синхронизации СХИ. Мин.и ЗВМ при получении сигнала СХИ считывает информацию, поступающую на ее шину данных, снимает выставленный код с шины 9 адреса. Дешифратор 14 вырабатьшает сигнал СИП для отлаживаемого вычислителя, поступающий на выход 10 устройства.

Если после получения адреса необходимо произвести операцию чтения, то мини-ЭВМ выставляет по шинам 8 и 9 сигнал СХЗ и соответствующий код дешифратору 14. С выхода дешифратора 14 вьфабатьюается сигнал, поступающий на управляющий вход регистра 3, в результате чего в регистре 3 происходит запись информации, поступающей на его информационные входы с шины данных мини-ЭВМ (вторая двунаправленная шина 12 устройства). После прекращения переходных процессов в регистре 3 дешифратор 14 сравнения вырабатьшает сигнал, поступающий с его седьмого выхода на первую группу входов группы 4 элементов И, в результате чего информация с :группы выходов регистра 3, поступая на вторую группу входов группы 4 элементов И, коммутщ)уется послед ним на шине отлаживаемого вычислителя (на первую двунаправленную информационную шину 7 устройства). После окончания переходных процессов в группе 4 элементов И вырабатывается сигнал СИП для отлаживаемого вычислителя на выходе 10 устройства. С выхода элемента 16 задержки /на выход П устройства выдается сиг нал СХИ. Мини-ЭВМ при получении сиг нала СХИ снимает сигнал СХЗ (шина 8 устройства), код с шины адреса (шина 9 устройства) и информацию с шины данных (шина 12 устройства).

Таким образом, предлагаемое устройство обеспечивает значительное

уменьшение времени отладки программ, так как позволяет автоматизировать этот процесс.

Формула изобре,тения

Устройство для отладки программ, содержащее .схему сравнения, элемент

И, регистр и мультиплексор, причем выход схемы сравнения соединен с первым входом элемента И, адресный вход устройства соединен с первым входом схемы сравнения, второй вход

которой соединен с входом задания начального адреса устройства, первый информационный вход устройства соединен с первым информационным входом мультиплексора, о т л и ч а ю щ е е с я тем, что, с целью по- вьш1ения быстродействия при отладке программ, в устройство введены формирователь короткого импульса, триггер, группа элементов И, дешифратор, элемент ИПИ, первый и второй элементы задержки, причем адресный вход устройства соединен с первым входом дешифратора, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выход схемы сравнения соединен с вторым входом деЩифратора, третий выход которого соединен с третьим управляющим входом мультиплексора и первым входом элемента ИЛИ, тактовьй вход устройства соединен с третьим входом дешифратора и вторым входом элемента И, выход которого через

первый элемент задержки соединен с первым вькодом синхронизации устройства, четвертьй выход дешифратора соединен с входом записи регистра, с вторым входом элемента ИЛИ и через

формирователь короткого импульса с единичным входом триггера, прямой выход которого соединен с первыми входами элементов И группы, информационные выходы регистра соединены с

вторыми входами соответствующих элементов И группы, выхода которых соединены с второй группой информационных входов мультиплексора и являются первой группой информационных выходов устройства, выход

мультиплексора соединен с информа- ционным входом регистра и является вторым информационньм выходом устройства, выход элемента ИЛИ через второй элемент задержки соединен с тактовым входом триггера и является вторым выходом синхронизации уст Составитель И.Сигалов Редактор А.Шандор Техред Л.Олейник Корректор С.Шекмар

1715/52

Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ШШ Патент, г.Ужгород, ул.Проектная,4

ройства, вход начальной установки устройства соединен с нулевым входом триггера, информационный вход которого соединен с шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1317444A2 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для формирования сигнала идентификации начала команды ЭВМ | 1985 |

|

SU1352493A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программ вычислительной системы в реальном масштабе временя. Положительный эффект изобретения заключается в том, что оно повышает производительность при отладке программ за счет того, что позволяет контролировать очередной адрес операндов в текущей команде, предыдущие адреса и операнды, контролировать и изменять внутренние регистры процессора отлаживаемой вычислительной системы, запускать программы с любого адреса, задавать несколько адресов и условий останова. В устройство, содержащее блок сравнения, элемент и регистр и мультиплексор, введены группа элементов И, формирователь короткого импульса, триггер, дешифратор, элемент ИЛИ, первый и второй элементы задержки. ил. i (/)

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1979 |

|

SU960821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-26—Подача