Изобретение относится к вычислительной технике и может быть использовано в устройствах сопряжения в процессе обмена данными с возможностью перестройки форматов слов.

Целью изобретения является расширение функциональных возможностей. устройства за счет перестройки разрядности, числа слов и начальной фазы преобразования..

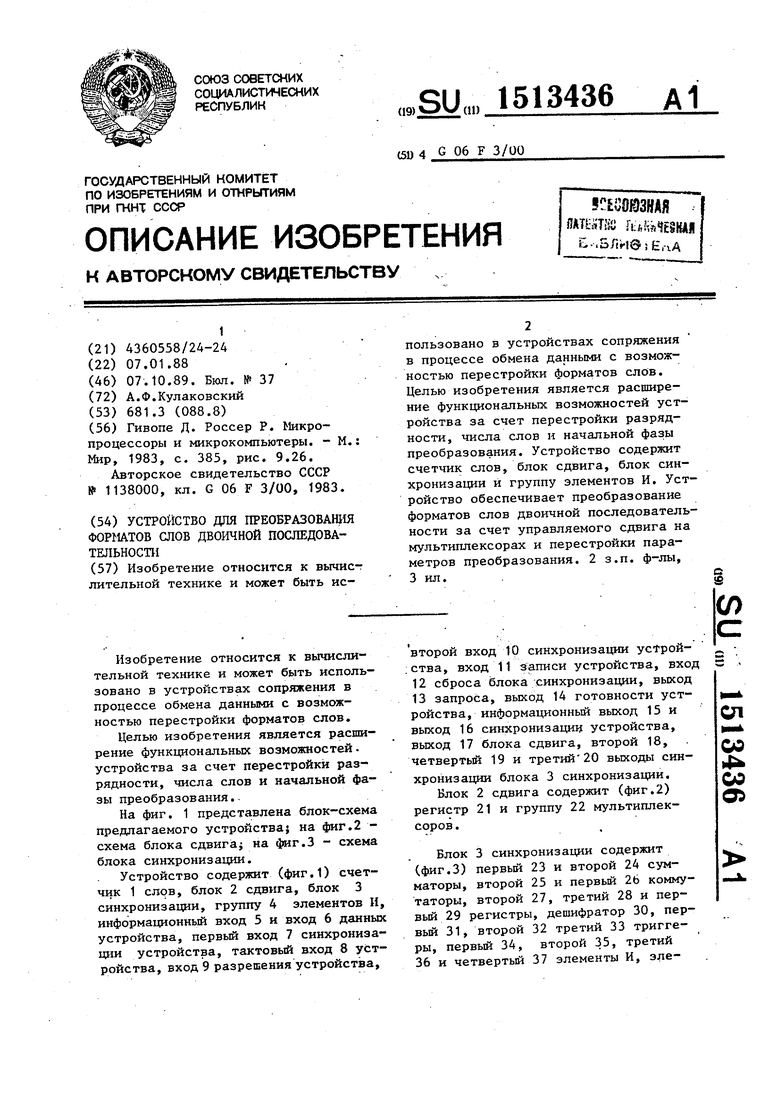

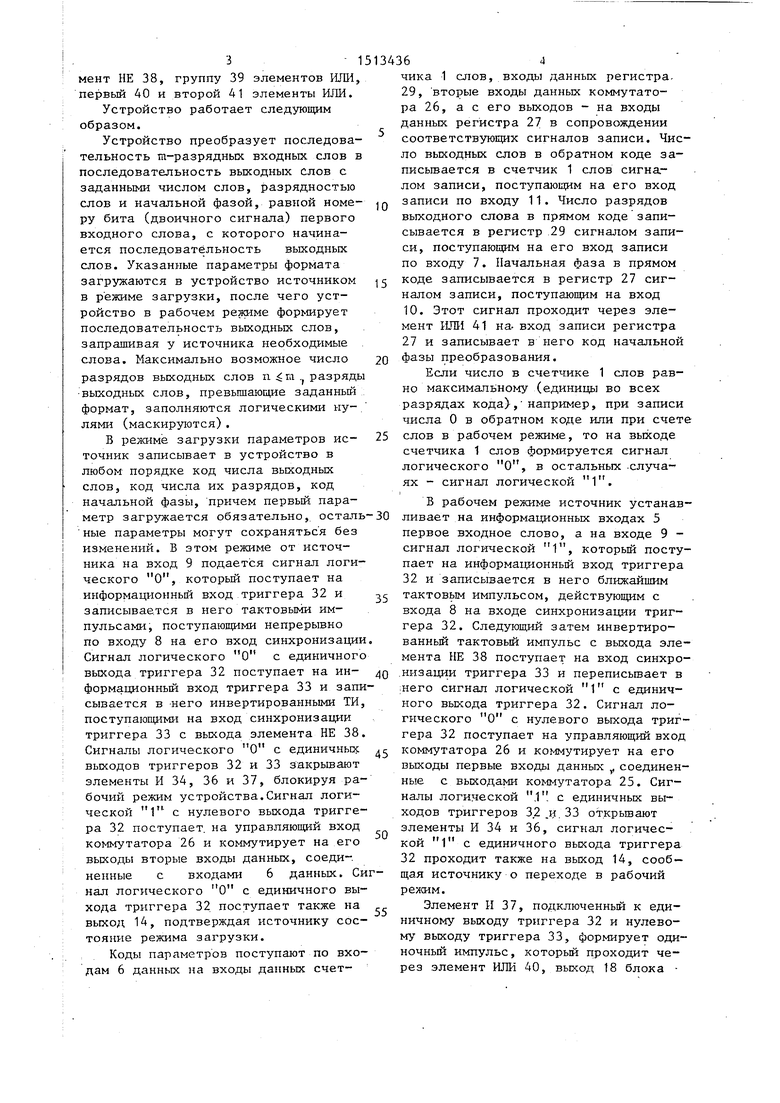

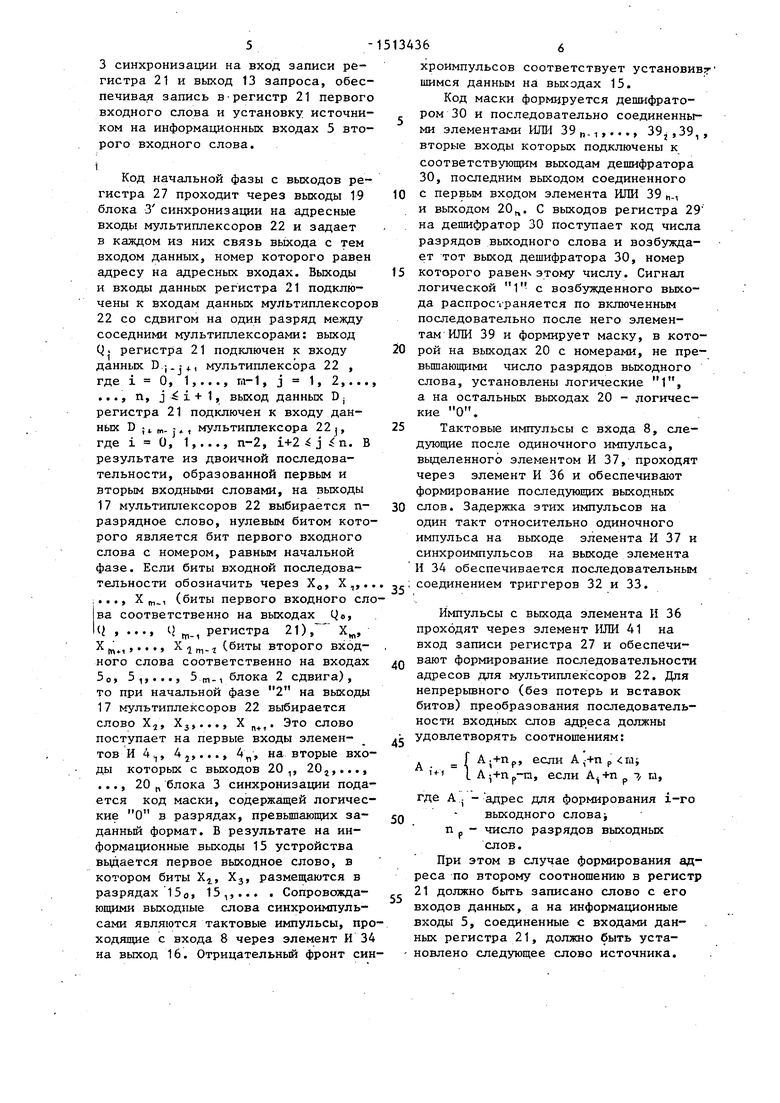

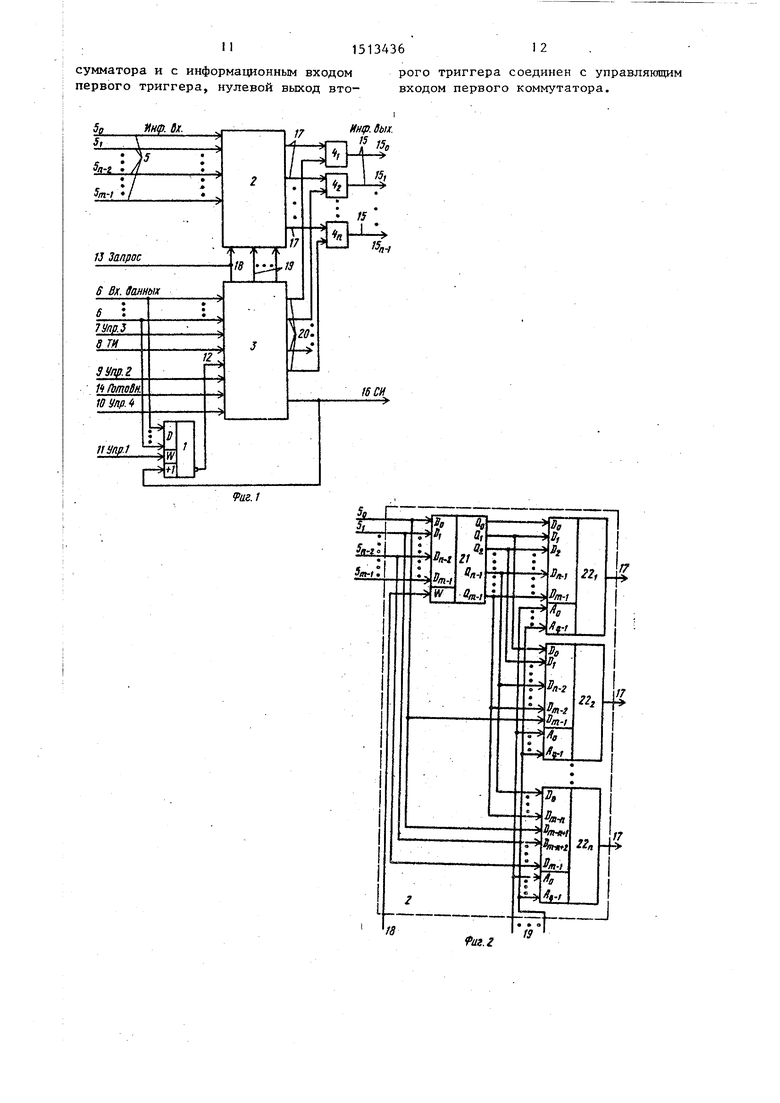

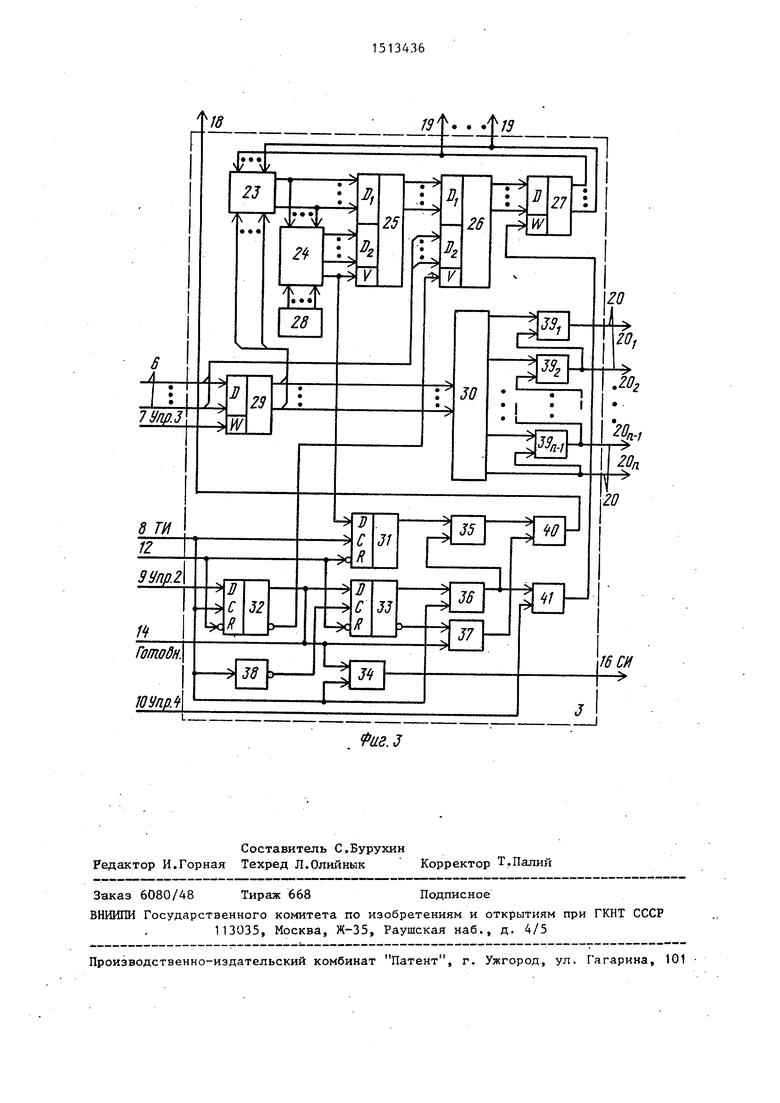

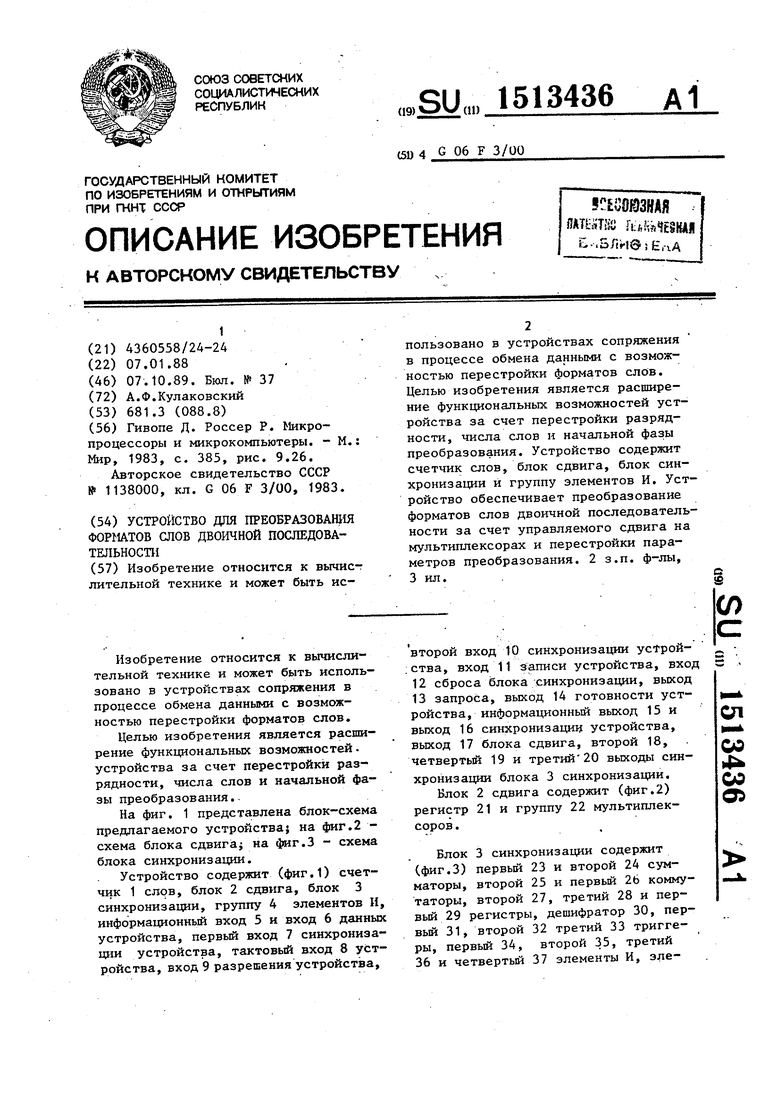

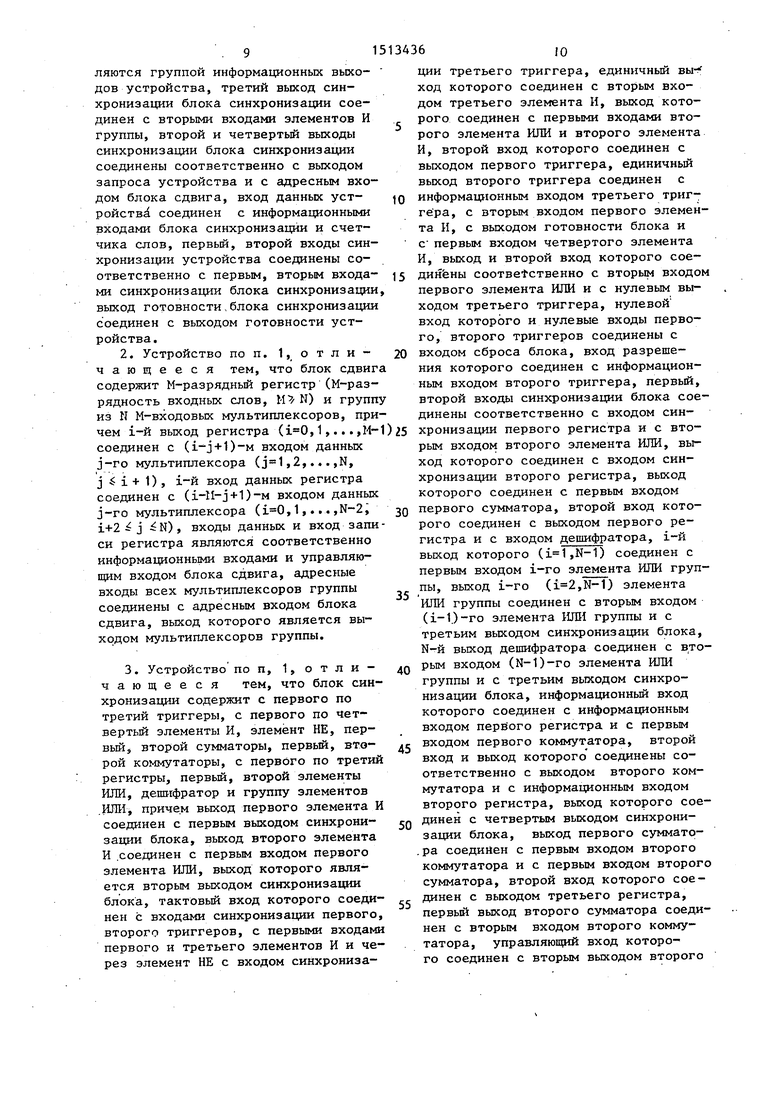

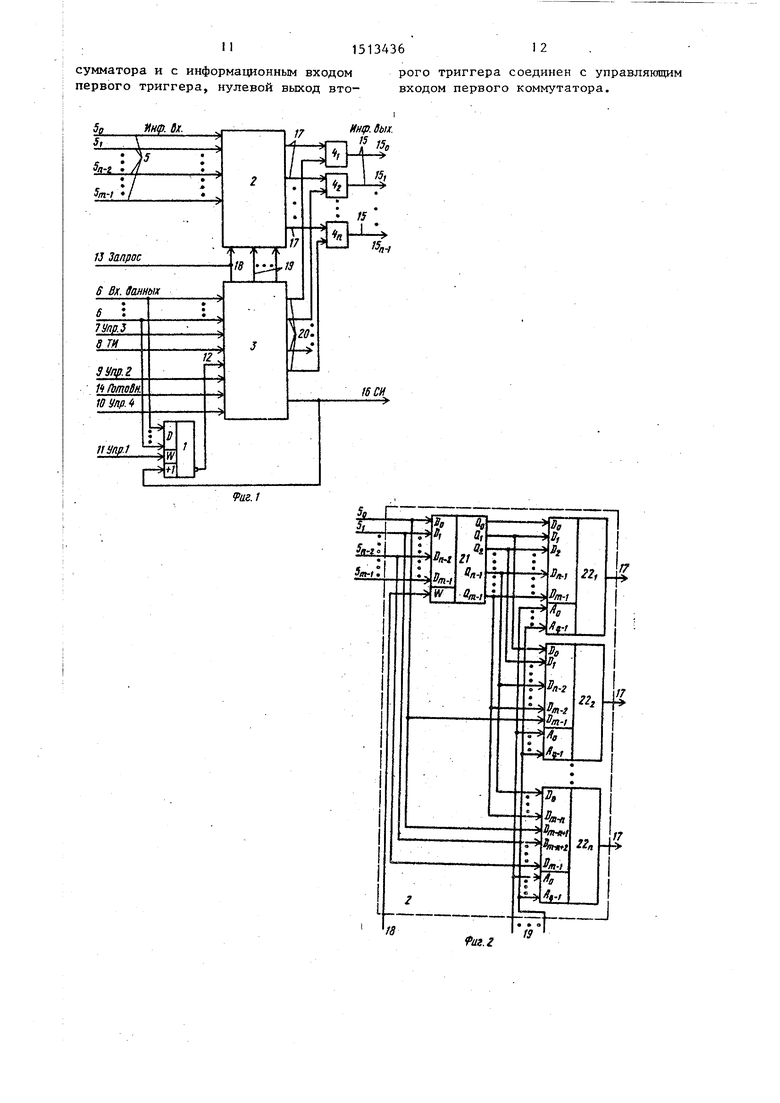

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - схема блока сдвига на фиг.З - схема блока синхронизации.

Устройство содержит (фиг.1) счетчик 1 слов, блок 2 сдвига, блок 3 синхронизации, группу 4 элементов И, информационный вход 5 и вход 6 данных устройства, первый вход 7 синхронизации устройства, тактовый вход 8 устройства, вход 9 разрешения устройства.

второй вход 10 синхронизации усТрой- :ства, вход 11 записи устройства, вход

12сброса блока синхронизации, выход

13запроса, выход 14 готовности устройства, информационный выход 15 и выход 16 синхронизации устройства, выход 17 блока сдвига, второй 18, четвертьй 19 и третий 20 выходы синхронизации блока 3 синхронизации.

Блок 2 сдвига содержит (фиг.2) регистр 21 и группу 22 мультиплексоров .

Блок 3 синхронизации содержит (фиг.З) первый 23 и второй 24 сумматоры, второй 25 и первый 26 коммутаторы, второй 27, третий 28 и первый 29 регистры, дешифратор 30, первый 31, второй 32 третий 33 триггеры, первый 34, второй 35, третий 36 и четвертьй 37 элементы И, элеСП

до «i

00 Од

мент НЕ 38, группу 39 элементов ИГШ первый 40 и второй 41 элементы ИЛИ.

Устройство работает следующим образом.

Устройство преобразует последовательность т-разрядных входных слов в последовательность выходных слов с заданными числом слов, разрядностью слов и начальной фазой, равной номе- ру бита (двоичного сигнала) первого входного слова, с которого начинается последовательность выходных слов. Указанные параметры формата загружаются в устройство источником в режиме загрузки, после чего устройство в рабочем режиме формирует последовательность выходных слов, запрашивая у источника необходимые слова. Максимально возможное число разрядов выходных слов п :$m . разряды выходных слов, превьгшаюсще заданный формат, заполняются логическими ну- лями (маскируются).

В режиме загрузки параметров ис- точник записывает в устройство в любом порядке код числа выходных слов, код числа их разрядов, код начальной фазы, причем первый параметр загружается обязательно, остал ные параметры могут сохраняться без изменений. В этом режиме от источника на вход 9 подается сигнал логического О, который поступает на

информационный вход триггера 32 и записывается в него тактовыми импульсами, поступающими непрерывно по входу 8 на его вход синхронизации Сигнал логического О с единичного выхода триггера 32 поступает на ин- формационньш вход триггера 33 и записывается в -него инвертированными ТИ, поступающими на вход синхронизации триггера 33 с выхода элемента НЕ 38. Сигналы логического О с единичных выходов триггеров 32 и 33 закрьшают элементы И 34, 36 и 37, блокируя рабочий режим устройства.Сигнал логической 1 с нулевого выхода триггера 32 поступает, на управляющий вход коммутатора 26 и коммутирует на его выходы вторые входы данных, соеди-. ненные с входами 6 данных. Синал логического О с единичного выхода триггера 32 поступает также на выход 14, подтверждая источнику состояние режима загрузки.

Коды параметров поступают по входам 6 данных на входы данных счетQ5 0

5 0

5

Q 5 -

чика 1 слов, входы данных регистра, 29, вторые входы данных коммутатора 26, ас его выходов - на входы данных регистра 11 в сопровождении соответствующих сигналов записи. Число выходных слов в обратном коде за- письгоается в счетчик 1 слов сигналом записи, поступающим на его вход записи по входу 11. Число разрядов выходного слова в прямом коде записывается в регистр 29 сигналом записи, поступающим на его вход записи по входу 7. Начальная фаза в прямом коде записывается в регистр 27 сигналом записи, поступающим на вход 10. Этот сигнал проходит через элемент ИЛИ 41 на- вход записи регистра 27 и записывает в него код начальной фазы преобразования.

Если число в счетчике 1 слов равно максимальному (единицы во всех разрядах кода), например, при записи числа О в обратном коде или при счете слов в рабочем режиме, то на выходе счетчика 1 слов формируется сигнал логического О, в остальных -случаях - сигнал логической 1.

В рабочем режиме источник устанавливает на информационных входах 5 первое входное слово, а на входе 9 - сигнал лопгческой 1, который поступает на информационный вход триггера 32 и записывается в него ближайшим тактовь1м импульсом, действующим с входа 8 на входе синхронизации триггера 32. Следующий затем инвертиро- ванньй тактовый импульс с выхода элемента НЕ 38 поступает на вход синхро- .низации триггера 33 и переписьшает в ;него сигнал логической 1 с единичного выхода триггера 32. Сигнал логического О с нулевого выхода триггера 32 поступает на управляющий вход коммутатора 26 и коммутирует на его выходы первые входы данных соединенные с выходами коммутатора 25. Сигналы логической ,1 с единичных выходов триггеров 32 .и.33 открьшают элементы И 34 и 36, сигнал логической 1 с единичного выхода триггера 32 проходит также на выход 14, сообщая источнику о переходе в рабочий режим.

Элемент И 37, подключенньй к единичному выходу триггера 32 и нулевому выходу триггера 33, формирует одиночный импульс, которьй проходит через элемент ИЛИ 40, выход 18 блока

3 синхронизации на вход записи регистра 21 и выход 13 запроса, обеспечивая запись в-регистр 21 первого входного слова и установку источником на информационных входах 5 второго входного слова.

i

Код начальной фазы с выходов регистра 27 проходит через выходы 19 блока 3 синхронизации на адресные входы мультиплексоров 22 и задает в каждом из них связь выхода с тем входом данных, номер которого равен адресу на адресных входах. Выходы и входы данных регистра 21 подключены к входам данных мультиплексоро 22 со сдвигом на один разряд между соседними мультиплексорами: вькод Q регистра 21 подютючен к входу данных D.J.J4., мультиплексора 22 , где i О, 1,..., гл-1, j 1, 2,... ..., п, j j i + 1, выход данньк D регистра 21 подключен к входу данных D jt „ -, мультиплексора 22j, где 1 0, 1,..., п-2, i+2 j п. В результате из двоичной последовательности, образованной первым и вторым входными словами, на выходы 17 мультиплексоров 22 выбирается п- разрядное слово, нулевым битом которого является бит первого входного слова с номером, равным начальной фазе. Если биты входной последовательности обозначить через Хо

1

X

(биты первого входного сл - т-1

ва соответственно на выходах Qo, (... Ч rti-1 регистра 21), Х, X ,,..., X . (биты второго входного слова соответственно на входах 5о, 5,,..., 5т., блока 2 сдвига), то при начальной фазе 2 на выходы 17 мультиплексоров 22 выбирается

слово X

1

i

Это слово

поступает на первые входы элементов

И 4

1

г

4, на вторые вхо- 20,. 20.

п ДЫ которых с выходов iu ,, iUj,...,

..., 20 „ блока 3 синхронизации подается код маски, содержащей логические О в разрядах, превышаюпщх за- данньй формат. В результате на информационные выходы 15 устройства выдается первое выходное слово, в

размещаются в

. Сопровождающими выходные слова синхроимпульсами являются тактовые импульсы, проходящие с входа 8 через элемент И 34 на выход 16. Отрицательный фронт синкотором биты Х, Хз, разрядах 15о 15

1

в , 10

15

20

25

30

о

35

40

45

50

55

хроимпульсов соответствует установив шимся данным на выходах 15.

Код маски формируется дешифратором 30 и последовательно соединенными элементами ИЛИ 39„.i,..., 39j,39,, вторые входы которых подключены к соответствующим выходам дешифратора 30, последним выходом соединенного с первым входом элемента ИЛИ 39 п- и вькодом 20. С выходов регистра 29 на дешифратор 30 поступает код числа разрядов выходного слова и возбуждает тот выход дешифратора 30, номер которого равенчэтому числу. Сигнал логической 1 с возбужденного выхода распрос раняется по включенным последовательно после него элементам ИЛИ 39 и формирует маску, в которой на выходах 20 с номерами, не пре- вьш1ающими число разрядов выходного слова, установлены логические 1, а на остальных выходах 20 - логические О.

Тактовые импульсы с входа 8, следующие после одиночного импульса, вьщеленного элементом И 37, проходят через элемент И 36 и обеспечивают формирование последующих выходных слов. Задержка этих импульсов на один такт относительно одиночного импульса на выходе элемента И 37 и синхроимпульсов на выходе элемента И 34 обеспечивается последовательным соединением триггеров 32 и 33.

Импульсы с выхода элемента И 36 проходят через элемент ИЛИ 41 на вход записи регистра 27 и обеспечивают формирование последовательности адресов для мультиплексоров 22, Для непрерьшного (без потерь и вставок битов) преобразования последовательности входных слов адреса должны удовлетворять соотношениям:

Г А;+Пр, если А,, 1 Л +Пр-п, если р гл,

где AJ - адрес для формирования i-ro

выходного словаi п р - число разрядов выходных

слов.

При этом в случае формирования адреса по второму соотношению в регистр 21 должно быть записано слово с его входов данных, а на информационные входы 5, соединенные с входами данных регистра 21, должно быть установлено следующее слово источника.

Текущий адрес А. с выходов регистра 27 поступает на первые входы сумматора 23, на вторые входы которого с выходов регистра 29 поступает код числа разрядов выходных слов. Код суммы с выходов сумматора 23 поступает на первые входы коммутатора 25 и вторые входы сумматора 24, на первые входы которого с выходов ре- Q гистра 28 подается обратный код чиса т-1, т.е. код числа 2 -та, где q - число разрядов кода числа т-1. Выходы и выход переноса сумматора 24.подключены соответственно к вторым входам и 5 правляющему входу комм татора 25. В сумматоре 24 образуется число ;+п +2 -1п. Если А., то возникают перенос (сигнал логической 1) на выходе переноса сумматора 20 24 и код числа А,+Пр-т на выходах сумматора 24, в противном случае перенос отсутствует. В коммутаторе 25 на его выходы коммутируются первые или вторые входы при наличии на уп- 25 равляющем входе коммутатора 25 соответственно сигнала логического О или логической 1. Поэтому на выходы коммутатора 25- проходят сигналы с вькодов сумматора 23 при отсутст- о ВИИ переноса в сумматоре 24 или сигналы с выходов сумматора 24 при наличии в нем переноса, т.е. адрес для формирования следующего выходного слова. Этот адрес проходит через коммутатор 26 на информационный вход регистра 27 и записывается в него при поступлении на вход синхронизации регистра 27 очередного импульса с выхода элемента ИЛИ 41. Адрес с вькодов регистра 27 проходит через выходы 19 блока 3 синхронизации на адресные входы мультиплексоров 22 и выбирает очередное выходное слово.

35

40

45

Сигналы с выхода переноса сумматора 24 поступают также на информационный вход триггера 31 и запоминаются тактовыми импульсами, действующими на его тактовом входе с входа 8. Сигнал переноса с единичного выхода триггера 31 открывает элемент И 35, очередной импульс с выхода элемента И 36 проходит через элементы И 35, ИЛИ 40, выход 18 блока 3 синхронизации на вход записи регистра 21, выход 13 запроса и запоминает в регистре 21 слово с его

5 0 5 о

5

0

5

0

5

входов данных, считывает новое слово источника на информационные входы 5. Синхроимпульсы с выходов 16 по- 1 ступают также на суммирующий вход счетчика 1 слов, наращивая каждый раз его содержимое на единицу. По окончании синхроимпульса, завершившего заполнение единицами всех разрядов счетчика 1 слов, на его выходе возникает сигнал логического О, поступающий на установочные входы триггеров 31-33 и устанавливающий их в О. Сигналы логического О с прямых выходов триггеров 31-33 закрывают элементы И 34-37, блокируя рабочий режим устройства. Сигнал логического с единичного выхода триггера 32 проходит также на выход 14 готовности, сообщая источнику об окончании преобразования форматов и готовности устройства к загрузке параметров. Источник снимает сигнал логической 1 с входа 9 и может приступать к загрузке параметров форматов следующего цикла преобразования.

Формула изобретения

1. Устройство для преобразования форматов слов двоичной последовательности, содержащее счетчик слов, блок синхронизации и блок сдвига, причем выход счетчика слов соединен с входом сброса блока синхронизации, первый выход синхронизации которого соединен с суммирующим входом счетчика слов и с выходом синхронизации устройства, второй выход синхронизации блока синхронизации соединен с управляющим входом блока сдвига, ин- формационньй вход которого соединен с информационным входом устройства,, вход разрешения, вход записи и тактовый вход устройства соединены соответственно с входом разрешения блока синхронизации с входом записи счетчика слов и с тактовым входом блока синхронизации , о т л и ч а ю- щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет перестройки разрядности, числа слов и начальной фазы преобразования, в устройство введена группа из N элементов И, при-, чем информационньй выход блока сдвига соединен с первыми входами элементов И группы, выходы которых яв9

ляются группой информационных выхо- дев устройства, третий выход синхронизации блока синхронизации соединен с вторыми входами элементов И группы, второй и четвертьй выходы синхронизации блока синхронизации соединены соответственно с выходом запроса устройства и с адресным входом блока сдвига, вход данных уст- ройств4 соединен с информационными входами блока синхронизации и счетчика слов, первый, второй входы синхронизации устройства соединены соответственно с первым, вторым входами синхронизации блока синхронизаци выход готовности,блока синхронизаци соединен с выходом готовности устройства.

2. Устройство по п. 1, отли

чающееся тем, что блок сдвига содержит М-разрядный регистр (М-раз- рядность входных слов, М N) и группу из N М-входовых мультиплексоров, приИ, выход и второй вход которого сое- 15 динёны cooTBetCTBeHHO с вторым входом первого элемента ИЛИ и с нулевым выходом третьего триггера, нулевой вход которого и нулевые входы первого, второго триггеров соединены с входом сброса блока, вход разрешения которого соединен с информационным входом второго триггера, первьй, второй входы синхронизации блока соединены соответственно с входом син30

чем i-й выход регистра (,1,...,М-1)25 хронизации первого регистра и с вто- соединен с ()-M входом данных j-ro мультиплексора (,2,...,N, j i 1) , i-й вход данных регистра соединен с (i-n-j+1)-M входом данных j-ro мультиплексора (,1,...,N-2, N), входы данных и вход записи регистра являются соответственно информационными входами и управляющим входом блока сдвига, адресные входы всех мультиплексоров группы соединены с адресным входом блока сдвига, выход которого является выходом мультиплексоров группы.

35

рым входом второго элемента ИЛИ, выход которого соединен с входом синхронизации второго регистра, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом первого регистра и с входом дешифратора, 1-й выход которого (,N-1) соединен с первым входом 1-го элемента ИЛИ группы, выход 1-го (,N-1) элемента ИЛИ группы соединен с вторым входом (1-1.)-го элемента ИЛИ группы и с третьим выходом синхронизации блока, N-й выход дешифратора соединен с вторым входом (N-1)-ro элемента ИЛИ группы и с третьим выходом синхронизации блока, информационный вход которого соединен с информационным входом пербого регистра и с первым входом первого коммутатора, второй вход и выход которого соединены соответственно с выходом второго коммутатора и с информационным входом второго регистра, выход которого сое- гп динен с четвертым выходом синхронизации блока, выход первого суммато- .ра соединен с первым входом второго коммутатора и с первым входом второго сумматора, второй вход которого соединен с выходом третьего регистра, первый выход второго сумматора соединен с вторым входом второго коммутатора, управляющий вход которого соединен с вторым выходом второго

3. Устройство по п, 1, отличающееся тем, что блок синхронизации содержит с первого по третий триггеры, с первого по четвертый элементы И, элемент НЕ, первый, второй сумматоры, первый, это- рой коммутаторы, с первого по третий регистры, первый, второй элементы ИЛИ, дешифратор и группу элементов .ИЛИ, причем выход первого элемента И соединен с первым выходом синхронизации блока, выход второго элемента И .соединен с первым входом первого элемента ИЛИ, выход которого является вторым выходом синхронизации блока, тактовый вход которого соеди- нен с входами синхронизации первого, второго триггеров, с первыми входами первого и третьего элементов И и через элемент НЕ с входом синхрониза

10

0

ции третьего триггера, единичньш вы- ход которого соединен с вторым входом третьего элемента И, выход которого соединен с первыми входами второго элемента ИЛИ и второго элемента И, второй вход которого соединен с выходом первого триггера, единичный выход второго триггера соединен с информационным входом третьего триггера, с вторым входом первого элемента И, с выходом готовности блока и С первым входом четвертого элемента

И, выход и второй вход которого сое- 5 динёны cooTBetCTBeHHO с вторым входом первого элемента ИЛИ и с нулевым выходом третьего триггера, нулевой вход которого и нулевые входы первого, второго триггеров соединены с входом сброса блока, вход разрешения которого соединен с информационным входом второго триггера, первьй, второй входы синхронизации блока соединены соответственно с входом син0

0

5 хронизации первого регистра и с вто-

5

0

j ,

рым входом второго элемента ИЛИ, выход которого соединен с входом синхронизации второго регистра, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом первого регистра и с входом дешифратора, 1-й выход которого (,N-1) соединен с первым входом 1-го элемента ИЛИ группы, выход 1-го (,N-1) элемента ИЛИ группы соединен с вторым входом (1-1.)-го элемента ИЛИ группы и с третьим выходом синхронизации блока, N-й выход дешифратора соединен с вторым входом (N-1)-ro элемента ИЛИ группы и с третьим выходом синхронизации блока, информационный вход которого соединен с информационным входом пербого регистра и с первым входом первого коммутатора, второй вход и выход которого соединены соответственно с выходом второго коммутатора и с информационным входом второго регистра, выход которого сое- п динен с четвертым выходом синхронизации блока, выход первого суммато- .ра соединен с первым входом второго коммутатора и с первым входом второго сумматора, второй вход которого соединен с выходом третьего регистра, первый выход второго сумматора соединен с вторым входом второго коммутатора, управляющий вход которого соединен с вторым выходом второго

сумматора и с информационным входом первого триггера, нулевой выход второго триггера соединен с управляющим входом первого коммутатора.

Фи.8.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для ввода информации | 1986 |

|

SU1383330A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах сопряжения в процессе обмена данными с возможностью перестройки форматов слов. Целью изобретения является расширение функциональных возможностей устройства за счет перестройки разрядности, числа слов и начальной фазы преобразования. Устройство содержит счетчик слов, блок сдвига, блок синхронизации и группу элементов И. Устройство обеспечивает преобразование форматов слов двоичной последовательности за счет управляемого сдвига на мультиплексорах и перестройки параметров преобразования. 2 з.п.ф-лы, 3 ил.

| Гивопе Д | |||

| Россер Р | |||

| Микропроцессоры и микрокомпьютеры | |||

| - М | |||

| Мир, 1983, с | |||

| Саморазгружающаяся платформа | 1922 |

|

SU385A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Авторское свидетельство СССР № 1138000, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1988-01-07—Подача