Изобретение относится к вычислительной технике и может быть исполь- зозано для построения быстродействующих многооперандных арифметических Устройств.

Целью изобретения является повышение 6ticTpo действия.

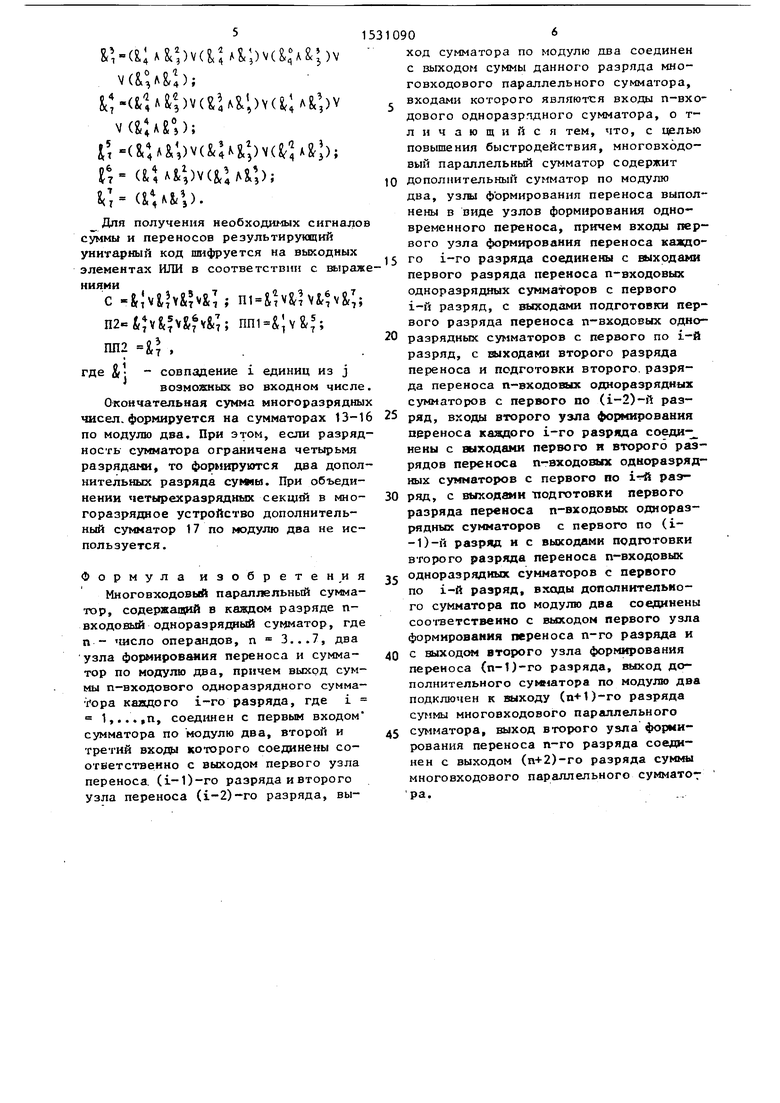

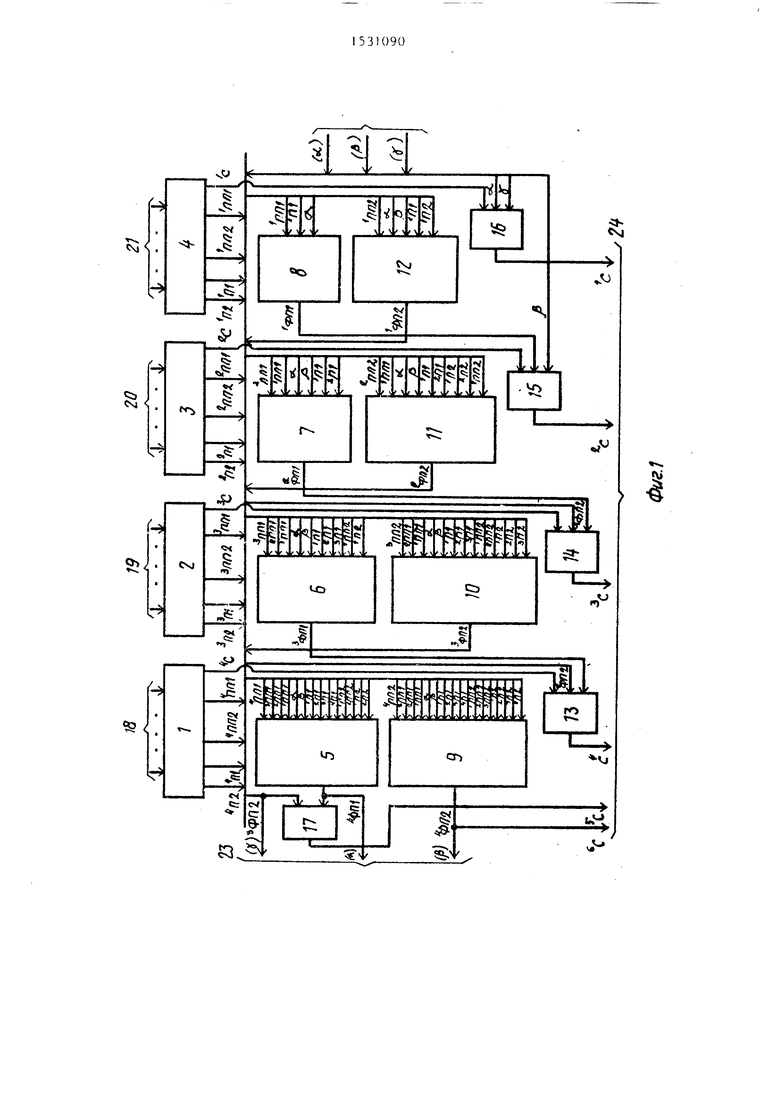

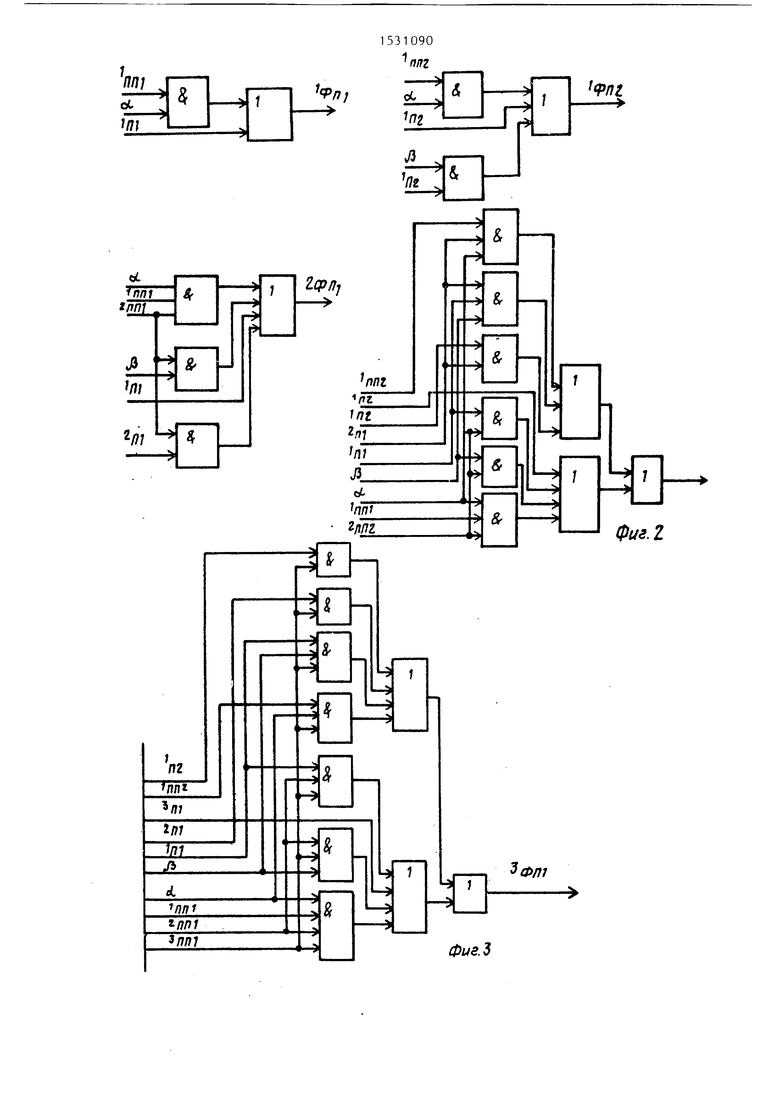

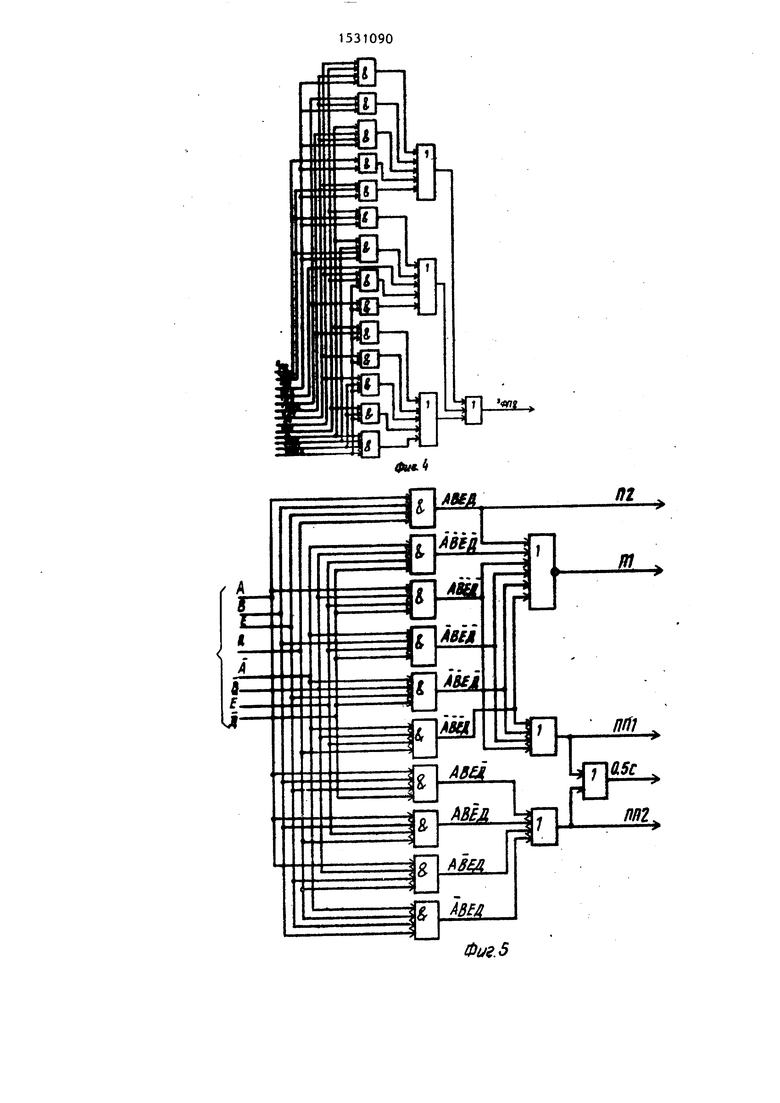

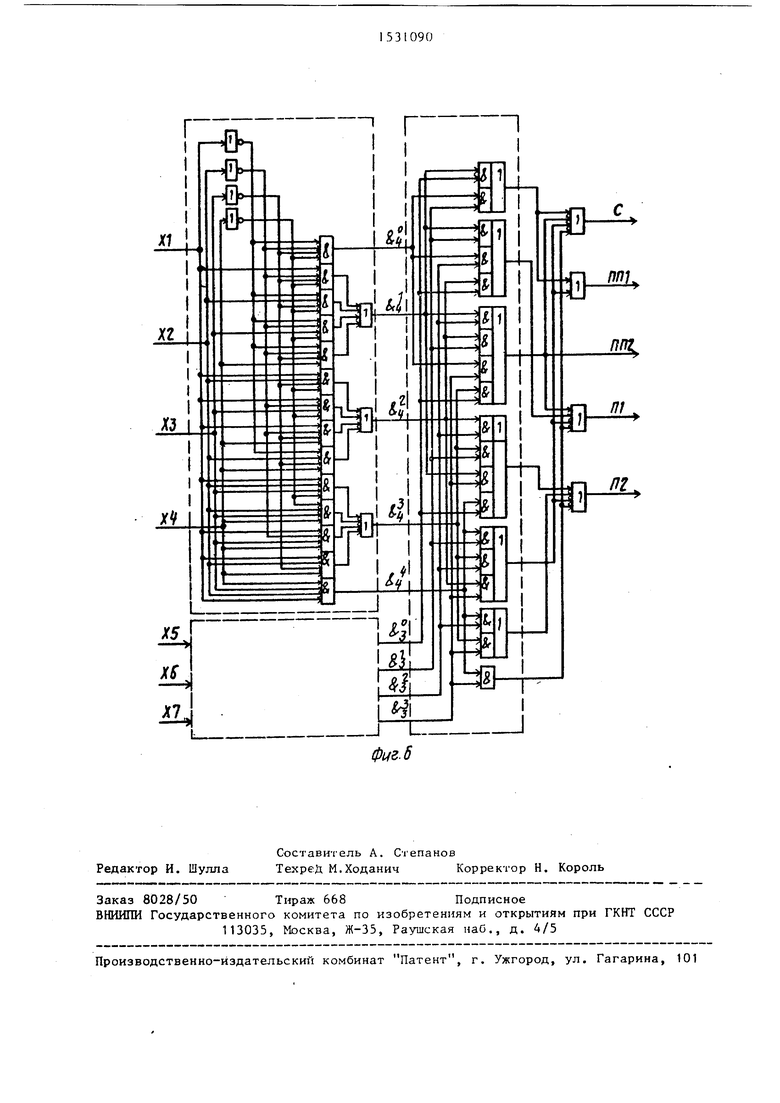

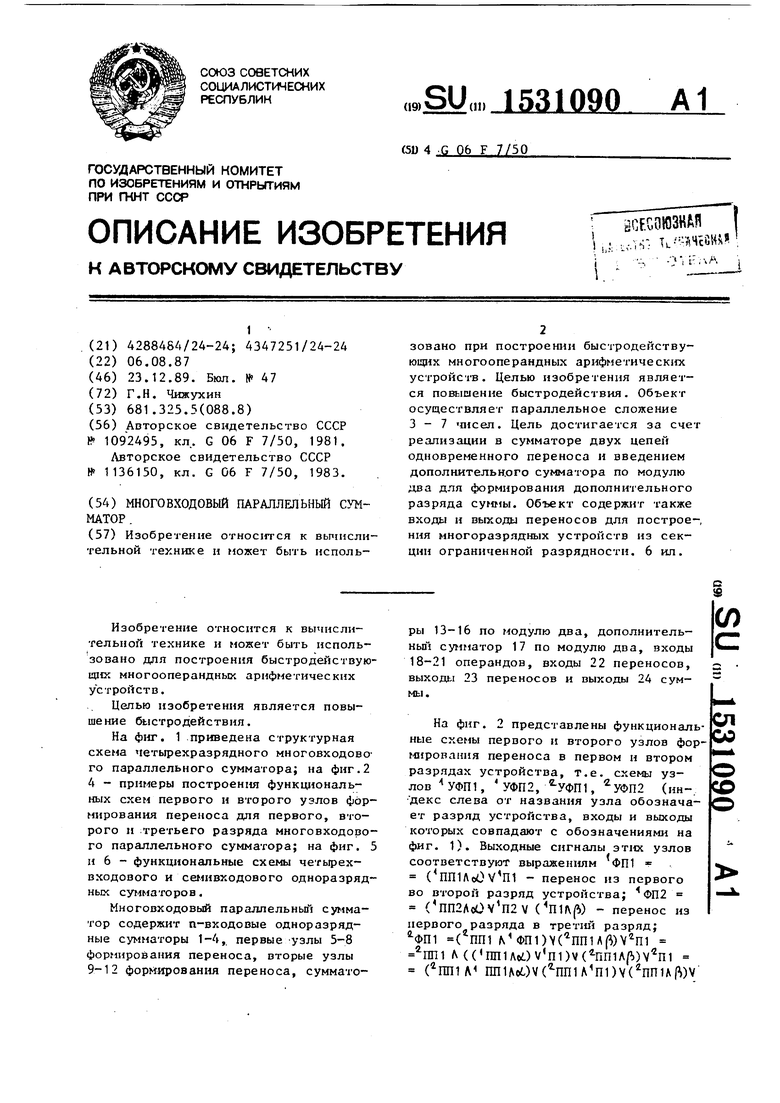

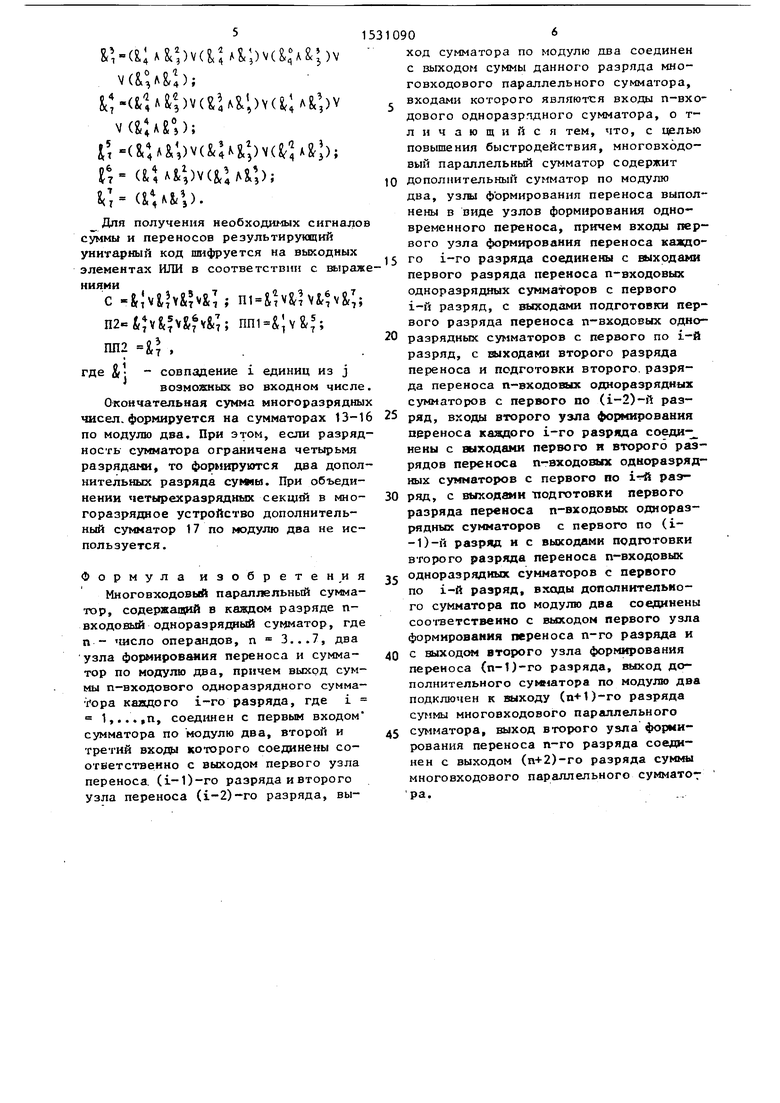

На фиг. 1 приведена структурная схема teтьфexpaзpяднoгo многовходово- го параллельного сумматора; на фиг.2 4 - примеры построения функциональных схем первого и второго узлов формирования переноса для первого, второго и л ретьего разряда многовходово- го параллельного сумматора; на фиг. 5 и 6 - функциональные схемы четырех- входового и семивходового одноразрядных сумматоров.

Многовходовый параллельньй тор содержит п-входовые одноразрядные су 1маторы 1-4, первые узлы 5-8 формирования переноса, вторые узлы 9-12 формирования переноса, сумматоры 13-16 по модулю два, дополнитель- ньй сумматор 17 по модулю два, входы 18-21 операндов, входы 22 переносов, выходы 23 переносов и выходы 24 суммы.

На фиг. 2 представлены функциональные схемы первого и второго узлов формирования переноса в первом и втором разрядах устройства, т.е. схемы узлов УФП1, УФП2, УФт , УФП2 (ин-. деке слева от названия узла обозначает разряд устройства, входы и выходы которых совпадают с обозначениями на фиг. 1). Выходные сигналы 3Titx узлов соответствуют выражениям ФП1 (nniAoOV m - перенос из первого во второй разряд устройства; ФП2 ( пП2ЛоОУ П2 V (%1Л(Ь) - перенос из первого разряда в третий разряд; ( ПП1 )(ПП1А() 1Ш1 Л (( mUci)v ni)V(ViniA(b) (ПП1А nnUo6)V()V()V

сл

tn

оо

(;о

3 15310904

- перенос из второго в третий ,рования переноса uL всего устройст-

разряд; ФП2 - (ПП2А ФП1 )V (Iin2A()V|ва;

V(ni Л ФП2) ((.) ФП2()V(ПП2Л on2)

Л ПО V ()) V (П1 ((ПП2Л 5V() ( -ПП2л гШ1Л ПП1л ГШ1Л«)

i.)v п2v ( П1 А())) (пп2Л raiiAet)VV()v(

J()V() ( -nU rin2Aot)Аи) V()V ( ПП2л 1Ш1Л ПП2Л

V(m A n2)V((i) - перенос изЛо1;)/( Л n2)V ( A niA/i)V

второго в четвертый разряд. V (1Ш2л П1 )V ( ПП2А ПП2А nnUQt)V ( -ПП2Л

Выходные сигналы первого и второго toЛ )V ( ПП2А ПП2Ар)) V ( nri2A n2)V

узлов формирования переноса для тре-Ч( ПП2 А ШЛ ПП2ЛоС.)У ( А -П1 )У

тьего разряда устройства описываютсяVCnn2A -ni А П1 Afi) (П1 Л 1Ш2Л ПП1Л,ОУ

вырахсепиями ФП1 (ГШ1 А ФПОУV ( А TiOV )У

V(nniA on2) ( nnU nniA nniAo6)VV ( )V С П1Л Vin2 А пП2Ао4.)

V()v( nniA nniAp)v 15( л n2)v(nu nri2A nuf)v t:

V(nni )V( nniA nn2A t)V( nnuVi2)VV(ni ) V( niA nu nn2A ПП1 AcC ) V

V(nniA niA()ni - перенос из третье-VC Ol А П1 л 1Ш2А П1 )V А -Пи П2)

го разряда в четвериъй разряд ус х рой-V(ni А П1 П1Л f) - перенос из четства; ФП2 ( п112 ) V( nn2A on2)Vвертого разряда, используемьй для форV П2 () ( ПП2Л ПП1 А 1П1АЮ V 20 «фования переноса всего устройства.

V(im2A IiniA ni)Y( Afb)V(lin2AЕсли необходимо организовать многоA nDVC Vin2N nn2AoOV( nn2A n2)V(nn2Aвходовые многоразрядные параллельные

A niAp))V niV ( ni nn2A linU5(.)V ( и1 Лсумматоры, можно использовать выходЛ 1Ш2Л П1)V(nlN nn2Aft)V ( П1 )Vные переносы четырехразрядного многоV(niA nU nn2AoOV( )V( ri1A 25входового параллельного сумматора, коА П1А П1лП) - перенос из треч ьего раз-торые на выходах 23 определяются выряда, используемый для формированияраженипми

переноса oi всего устройства. 4mni. а 1-и

Для четвертого разряда выражения

следующие: 30Тогда в указанных выражениях под

( ПП1А ФП1)У()У П1 переносом об подразумевается ((x.Vg).

( nniA r nU nniA nniA()V(imiA nni Четырехвходовый и семивходовый одA tiniA ViDVC nniA nnU nniAf) Аноразрядный сумматоры формируют на

)V( nniA nniA nn2Act)V( Асвоих выходах сигналы суммы (С), перA nniA n2)Vrnnu nni A nUft)V(niI1 Авого и второго разряда переноса (П1

Л П1)У(ПП1А ПП2А ПП1А«1-)У( Г1П1А ПП2 А и П2) и сигналы подготовки этих разA nDV (rai1A nn2Ap.)V(nrilA n2)V (ПП1Арядов переноса (ПП1 и ПП2).

А ПП2АО(.) П2) V С ПГПЛЭти сигналы для четырех в ходов о го

N П1A niAft) - перенос из четвер-одноразрядного сумматора описываются

того разряда, используемый для форми- .выражениями

С АВЁДУАВЁДУЛВЕДУАВЁДУАВЕДУЛВ1ДУАВЕДУЛВЕД;

( 4n2; ,

4mni. а 1-и

( 4n2; ,

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| МНОГОУРОВНЕВАЯ M-МЕРНАЯ МАТРИЧНАЯ СУММИРУЮЩАЯ СТРУКТУРА ВЕРТИКАЛЬНОЙ АРИФМЕТИКИ В.М. ТАРАНУХИ | 2003 |

|

RU2246128C2 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| ПРИЕМНАЯ АППАРАТУРА БАЗОВОЙ СТАНЦИИ СИСТЕМЫ РАДИОСВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1996 |

|

RU2113766C1 |

| МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР | 1992 |

|

RU2047216C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих многооперандных арифметических устройств. Целью изобретения является повышение быстродействия. Объект осуществляет параллельное сложение 3-7 чисел. Цель достигается за счет реализации в сумматоре двух цепей одновременного переноса и введением дополнительного сумматора по модулю два для формирования дополнительного разряда суммы. Объект содержит также входы и выходы переносов для построения многоразрядных устройств из секции ограниченной разрядности. 6 ил.

П1 ЛBEДVABEДVЛBEДVABEДVABEДvABEД ;чисел в пятиразрядньш унитарный код

П2 АВЕД; и трех чисел в четырехразрядньш унитарный код, а также сумматора этих

Гт1 АВЕДУАВЕДУАВЕД«АВЕД; „ „ ;, дешифраторов формиПП2 ABEДvАВЕДVAБEДvАВЕД,руютсп разряды унитарного кода .,.

... & .. и & .. Д ,, отражаю1дие число

где А,В.Е,Д - входные операнды.mtч/ --i

«50 единиц в поступающих 4- и 3-разрядОдноразрядные сумматоры с большим,,

ных входных комбинациях. После сложечислом входов могут быть построены,

ния двух унитарных кодов получаем

например, с использованием преобра f грезультирующий унитарный код, разряди

зования группы входных одноразрядных

„ -.г - которого описываются выражениям

чисел в унитарный код количества еди---, ,

55 рО-С.. ниц с последующим суммированием этих 7

кодов на сумматоре унитарных коде.о1 , (,(С) д5, )

СемивходовьвЧ одноразрядньш .сумматорJ о о i о

состоит из двух дешифраторов четырехXT ( &) () (& 4 «) ;

&()v()(4)v (Цл8.Ъ;

Xc -(b ni5)v(&us.i)v(x,;A8ci)v

V(&;A&°); rT ()v()v();

Гт (,)v(&:Ail); ().

Для получения необходимых сигналов суммы и переносов результирующий унитарный код шифруется на выходных элементах ИЛИ в соответствии с кияии

с -&;vib& v&;; ni & ivttv8,;;

(fv&fY&;; , ПП2 & ,

где & - совпадение i единиц из j

возмояных во входном числе. Окончательная сумма многоразрядных чисел, формируется на сумматорах 13-16 по модулю два. При этом, если разрядность сумматора ограничена четырьмя разрядами, то формируются два допол- нительюсс разряда cyvHta. При объединении четырехразрядных секций в многоразрядное устройства дополнительный сумматор 17 по модулю два не используется.

Формула изобретен и я Многовходовый параллельный сумматор, содержа1ций в каждом разряде п- входовый одноразрядный сумматор, где п - число операндов, п 3,..7, два узла формирования переноса и сумматор по модулю два, причем выход суммы п-входового одноразрядного сумма- Гора кандого i-ro разряда, где i 1,...,п, соединен с первым входом сумматора по модулю два, второй и третий входы которого соединены соответственно с выходом первого узла переноса, (i-l)-ro разряда и второго узла переноса (i-2)-ro разряда, вы1

-

5310906

ход сумматора по модулю два соединен с выходом суммы данного разряда мно- говходового параллельного сумматора, , входами которого являются входы п-вхо- дового одноразрядного сумматора, о т- л и ч а ю щ и и с я тем, что, с целью повышения быстродействия, многовходо- вый параллельный сумматор содержит

0 дополнительный сумматор по модулю

два, узлы формирования переноса выполнены в виде узлов формирования одновременного переноса, примем входы первого узла формирования переноса кааздо15 го 1-го разряда соединены с выходами первого разряда переноса п-входовьпс одноразрядных сумматоров с первого i-й разряд, с выходами подготовки первого разряда переноса п-входовых одно20 разрядных сумматоров с первого по i-и разряд, с выходами второго разряда переноса и подготовки второго, разряда переноса п-входовых одноразрядных сумматоров с первого по (1-2)-й раз25 ряд, входы второго узла фор1 шровання переноса каждого i-ro разряда соеди- нены с выходами первого и второго разрядов переноса п-входовых одноразрядных сумматоров с первого по i- раэ30 ряд, с выходами подготовки первого разряда переноса п-входовых одноразрядных сумматоров с первого по (i- -1)-й разряд и с вьосодами подготовки второго разряда переноса п-входовык одноразрядных сумматоров с первого по i-й разряд, входы допапнительио- го сумматора по модулю два соединены соответственио с выходом первого узла формирования переноса п-го разряда и с выходом второго узла формирования переноса (n-l)-ro разряда, выход дополнительного сумматора по модутво два подключен к выходу ()-гo разряда суммы многовходового параллельного

45 сумматора, выход второго узла формирования переноса п-го разряда соединен с выходом (п+2)-го разряда суммы многовходового параллельного суммато7 ра.

35

40

b«4

Фиг. 5

Фиг. 6

| Двоичный сумматор | 1981 |

|

SU1092495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-23—Публикация

1987-08-06—Подача