(Л

;о

00

.

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики сложных цифровых устройств.

Цель изобретения является расширение диагностических возможностей за счет определения числа участков контролируемой последовательности, содержащих ошибочные биты, и опреде- ление номера искаженного участка при его единственности.

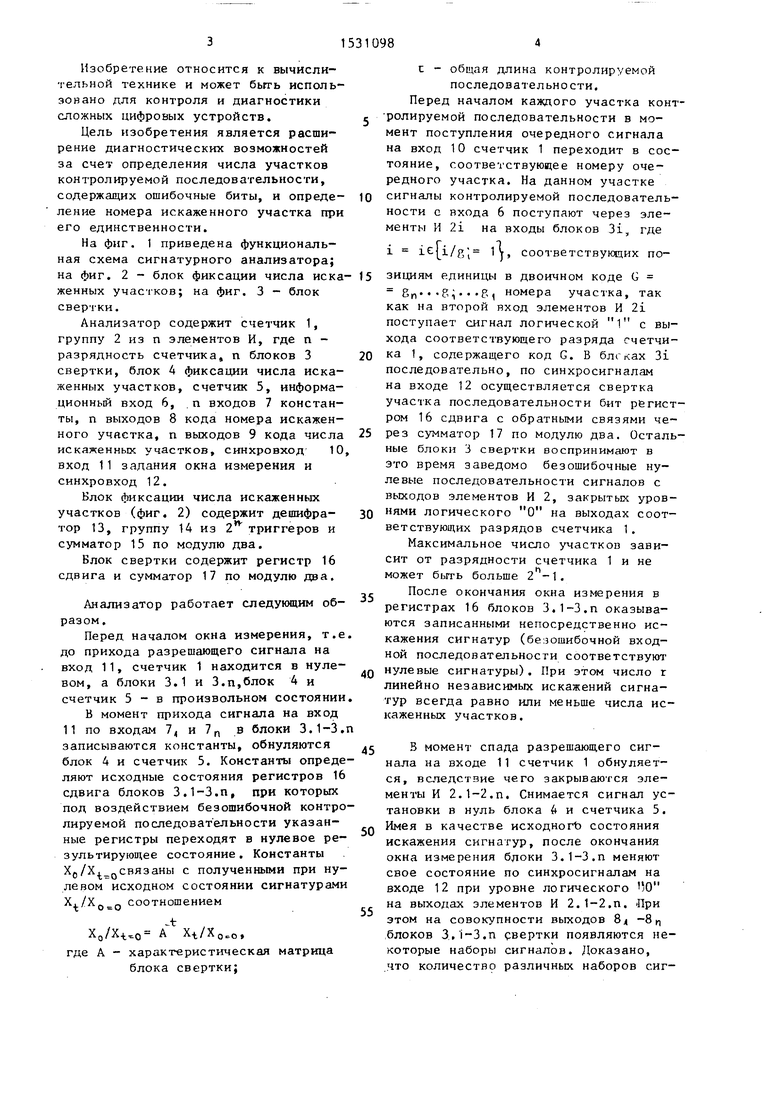

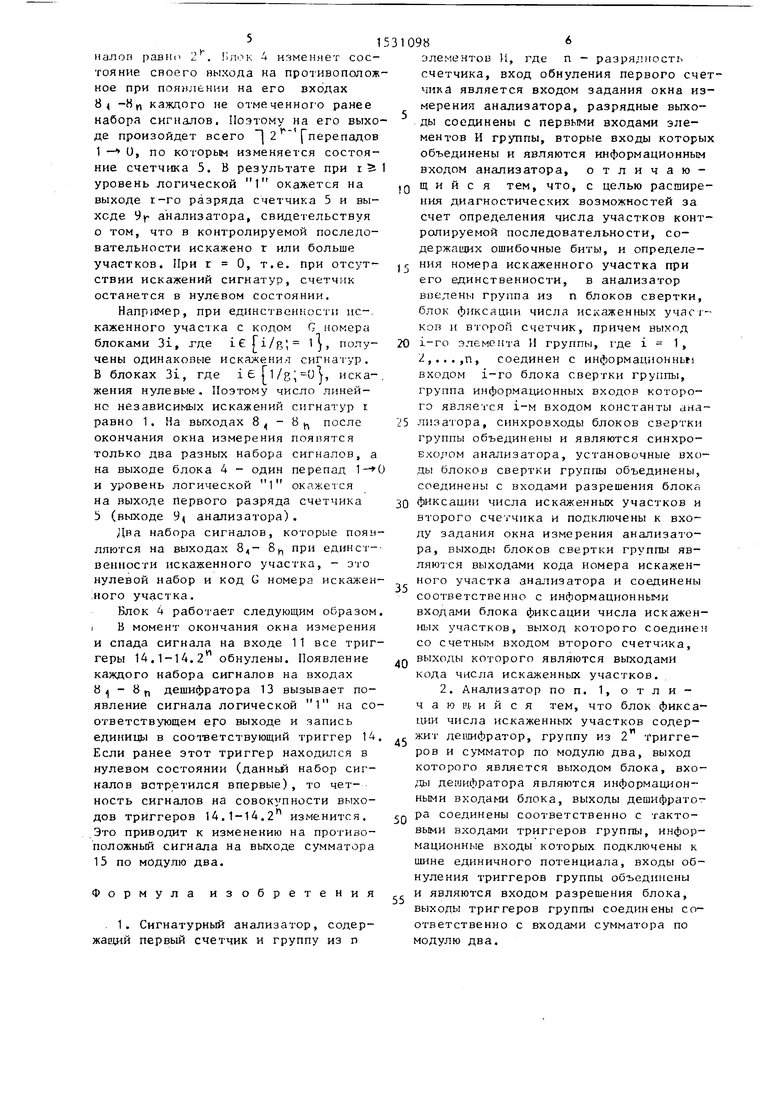

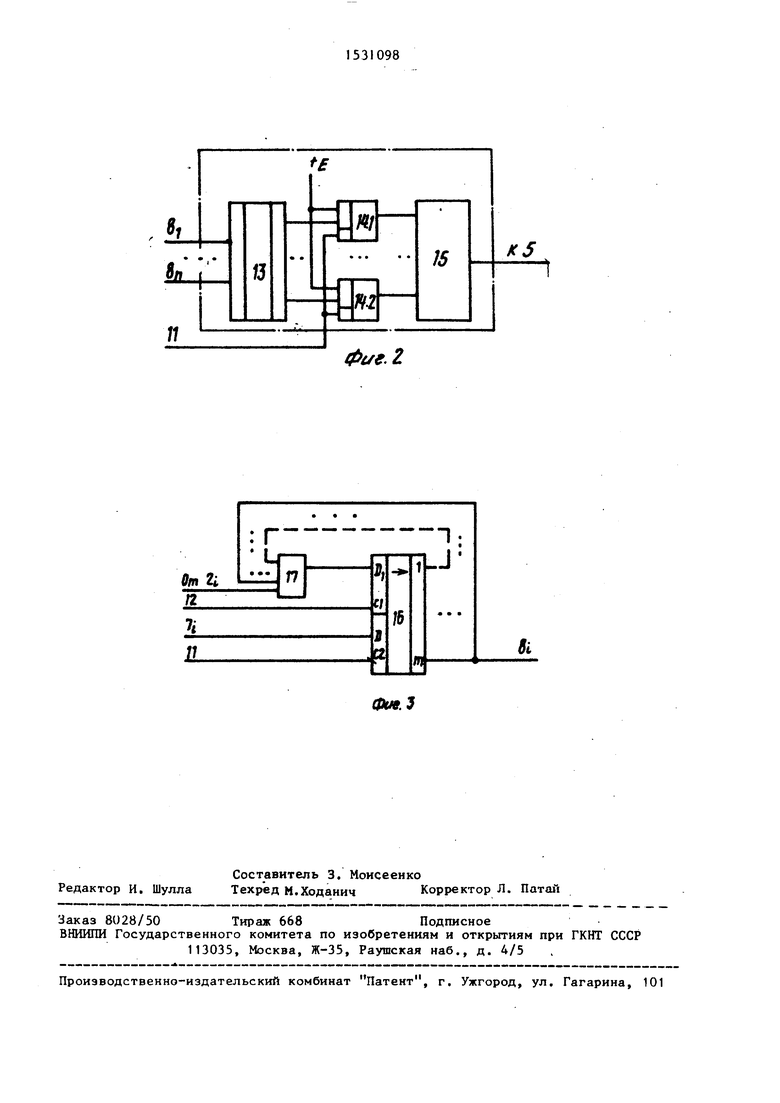

На фиг. 1 приведена функциональная схема сигнатурного анализатора; на фиг. 2 - блок фиксации числа иска- женных участков; на фиг. 3 - блок свертки.

Анализатор содержит счетчик 1, группу 2 из п элементов И, где п - разрядность счетчика, п блоков 3 свертки, блок 4 фиксации числа искаженных участков, счетчик 5, информационный вход 6, п входов 7 константы, п выходов 8 кода номера искаженного участка, п выходов 9 кода числа искаженных участков, синхровход 10 вход 11 задания окна измерения и синхровход 12.

Блок фиксации числа искаженньк участков (фиг. 2) содержит дешифра- тор 13, группу 14 из 2 триггеров и сумматор 15 по модулю два.

Блок свертки содержит регистр 16 сдвига и сумматор 17 по модулю два.

Анализатор работает следующим образом.

Перед началом окна измерения, т.е до прихода разрешающего сигнала на вход 11, счетчик 1 находится в нуле- вом, а блоки 3.1 и З.п,блок 4 и счетчик 5 - в произвольном состоянии

В момент прихода сигнала на вход 11 по входам 7 и 7f, в блоки 3.1-З. записываются константы, обнуляются блок 4 и счетчик 5. Константы определяют исходные состояния регистров 16 сдвига блоков 3.1-З.п, при которых под воздействием безошибочной контролируемой последовательности указан- ные регистры переходят в нулевое результирующее состояние. Константы XO/X,Qсвязаны с полученными при нулевом исходном состоянии сигнатурами

соотношением

А Xt/Xo.o, где А - характеристическая матрица блока свертки;

5

0 5

0

5

с - общая длина контролируемой

последовательности. Перед началом каждого участка контролируемой последовательности в момент поступления очередного сигнала на вход 10 счетчик 1 переходит в состояние, соответствующее номеру очередного участка. На данном участке сигналы контролируемой последовательности G входа 6 поступают через элементы И 2i на входы блоков 31, где

i 1 f, соответствующих позициям единицы в двоичном коде G Sn- -Si - Si номера участка, так как на второй вход элементов И 21 поступает сигнал логической 1 с выхода соответствующего разряда счетчика 1, содержащего код G. В блгках 3i последовательно, по синхросигналам на входе 12 осуществляется свертка участка последовательности бит регистром 16 сдвига с обратными связями через сумматор 17 по модулю два. Остальные блоки 3 свертки воспринимают в это время заведомо безошибочные нулевые последовательности сигналов с выходов элементов И 2, закрытых уровнями логического О на выходах соответствующих разрядов счетчика 1.

Максимальное число участков зависит от разрядности счетчика 1 и не может быть больше 2 -1.

После окончания окна измерения в регистрах 16 блоков 3.1-З.п оказываются записанными непосредственно искажения сигнатур (безошибочной входной последовательности соответствуют нулевые сигнатуры). При этом число г линейно независимых искажений сигнатур всегда равно или меньше числа искаженных участков.

В момент спада разрешающего сигнала на входе 11 счетчик 1 обнуляется, вследствие чего закрываются элементы И 2.1-2.п. Снимается сигнал установки в нуль блока 4 и счетчика 5. Имея в качестве исходногЪ состояния искажения сигнатур, после окончания окна измерения блоки 3.1-З.п меняют свое состояние по синхросигналам на входе 12 при уровне логического 50 на выходах элементов И 2.1-2.п. При этом на совокупности выходов 8д -8п .блоков 3, i-3.n свертки появляются некоторые наборы сигналов. Доказано, что количество различных наборов сиг5

налов равии 2. Ьгчлк 4 изменяет состояние своего выхода на противоположное при появлении на его входах 84 -8 п каждого не отмеченног о ранее набора сигналов. Поэтому на его выходе произойдет всего | 2 (перепадов 1 - и, по которым изменяется состояние счетчика 5. В результате при г 5i уровень логической 1 окажется на выходе г-го разряда счетчика 5 и выходе 9 анализатора, свидетельствуя

0том, что в контролируемой последовательности искажено г или больше участков. При г О, т.е. при отсутствии искажений сигнатур, счетчик останется в нулевом состоянии.

Например, при единственности не-, каженного учас1ка с кодом G номера блоками 3i, где 1, получены одинаковые искажения сигнатур. В блоках 31, где , искаженин нулевые. Поэтому число линейно независимых искажений сигнатур г равно 1. На выходах 8 - 8 после окончания окна измерения появятся только два разных набора сигналов, а на выходе блока 4 - один перепад 1и уровень логической 1 окажется на выходе первого разряда счетчика Ь (выходе 9 анализатора).

Два набора сигналов, которые появляются на выходах 8 при единственности искаженного участка, - это нулевой набор и код G номера искаженного участка.

Блок 4 работает следующим образом

1В момент окончания окна измерения и спада сигнала на входе 11 все триггеры 14.1-14.2 обнулены. Появление каждого набора сигналов на входах дешифратора 13 вызывает появление сигнала логической 1 на соответствующем его выходе и запись единицы в соответствующий триггер 14 Если ранее этот триггер находился в нулевом состоянии (данньй набор сигналов встретился впервые), то четность сигналов на совокупности выходов триггеров 14.1-14.2 изменится. Это приводит к изменению на противоположный сигнала на выходе сумматора 15 по модулю два.

Формула изобретения

. 1. Сигнатурный анализатор, содер- жашлй первый счетчик и группу из п

1098

элементов И, где п - разрялност счетчика, вход обнуления первого счетчика является входом задания окна измерения анализатора, разрядные выходы соединены с первыми входами элементов И группы, вторые входы которых объединены и являются информационным входом анализатора, отличаю Q щ и и с я тем, что, с целью расширения диагностических возможностей за счет определения числа участков контролируемой последовательности, содержащих ошибочные биты, и определеj НИЛ номера искаженного участка при его единственности, в анализатор введены группа из п блоков свертки, блок фиксации числа искаженных учас г- ков и второй счетчик, причем выход

20 i-ro элемента И группы, где , 2,...,п, соединен с информационнь входом 1-го блока свертки группы, группа информационных входов которого является 1-м входом константы ана5 лизатора, синхровходы блоков свертки группы объединены и являются синхро- Бхо;юм анализатора, установочные входы блоков свертки группы объединены, соединень с входами разрешения блока

0 фиксации числа искаженных участков и второго счетчика и подключены к входу задания окна измерения анализатора, выходы блоков свертки группы являются выходами кода номера искаженного участка анализатора и соединены соответственно с информационными входами блока фиксации числа искаженных участков, выход которого соединен со счетным входом второго счетчика,

.Q выходы которого являются выходами кода числа искаженных участков.

2. Анализатор по п. 1, о т л и - ч а ю щ. и и с я тем, что блок фиксации числа искаженных участков содер- , жит дешифратор, группу из 2 триггеров и сумматор по модулю два, выход которого является выходом блока, входы дешифратора являются информацион- ньми входами блока, выходы дешифратоп ра соединены соответственно с тактои

выми входами триггеров группы, информационные входы которых подключены к шине единичного потенциала, входы обнуления триггеров группы объединены и являются входом разрешения блока, выходы триггеров группы соединены соответственно с входами сумматора по модулю два.

5

Фе/e.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Сигнатурный анализатор | 1986 |

|

SU1453407A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики сложных цифровых устройств. Цель изобретения - расширение диагностических возможностей за счет определения числа участков контролируемой последовательности, содержащих ошибочные биты, и определение номера искаженного участка при его единственности. Анализатор содержит счетчик 1, группу 2 из N элементов И, где N - разрядность счетчика, N блоков 3 свертки, блок 4 фиксации числа искаженных участков, счетчик 5. 1 з.п.ф-лы, 3 ил.

(SM. i

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Сигнатурный анализатор | 1981 |

|

SU962962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-23—Публикация

1987-04-19—Подача