СП

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Вычислительный модуль и способ обработки с использованием такого модуля | 2018 |

|

RU2689433C1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| МНОГОПРОЦЕССОРНАЯ ВЕКТОРНАЯ ЭВМ | 1995 |

|

RU2113010C1 |

| ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ | 1996 |

|

RU2089936C1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

Изобретение относится к автоматике, вычислительной и информационно-измерительной технике и может быть использовано в системах цифровой обработки изображений. Целью изобретения является расширение функциональных возможностей за счет обеспечения параллельного обмена данными между блоком памяти изображений и процессорными элементами, между самими процессорными элементами, что увеличивает эффективность вычислений для широкого класса алгоритмов, и за счет выполнения в каждом процессорном элементе арифметических операций по модулям 211 -1, 213 -1, 217 - 1, 219 -1. В процессоре осуществляется параллельный обмен данными между четырьмя процессорными элементами и блоком памяти изображений, между процессорными элементами благодаря введению блока обмена, и функционального запоминающего устройства, причем процессор обработки изображений работает под управлением ЭВМ. Устройство предназначено для работы с системой "Спектр-ДК". 2 з.п. ф-лы, 3 ил.

Изобретение относится к автоматике, вычислительной и информационно- измерительной технике и может быть использовано в системах цифровой обработки изображений.

Цель изобретения - расширение функциональных возможностей за счет обеспечения параллельного обмена данными между памятью изображений и процессорными элементами, между самими процессорньгми элементами, что увеличивает эффективность вычислений для широкого класса алгоритмов, и обеспечения выполнения в каждом

процессорном элементе арифметических операций по модулям 2 -1, 21 -1,

217-1, 2й-1.

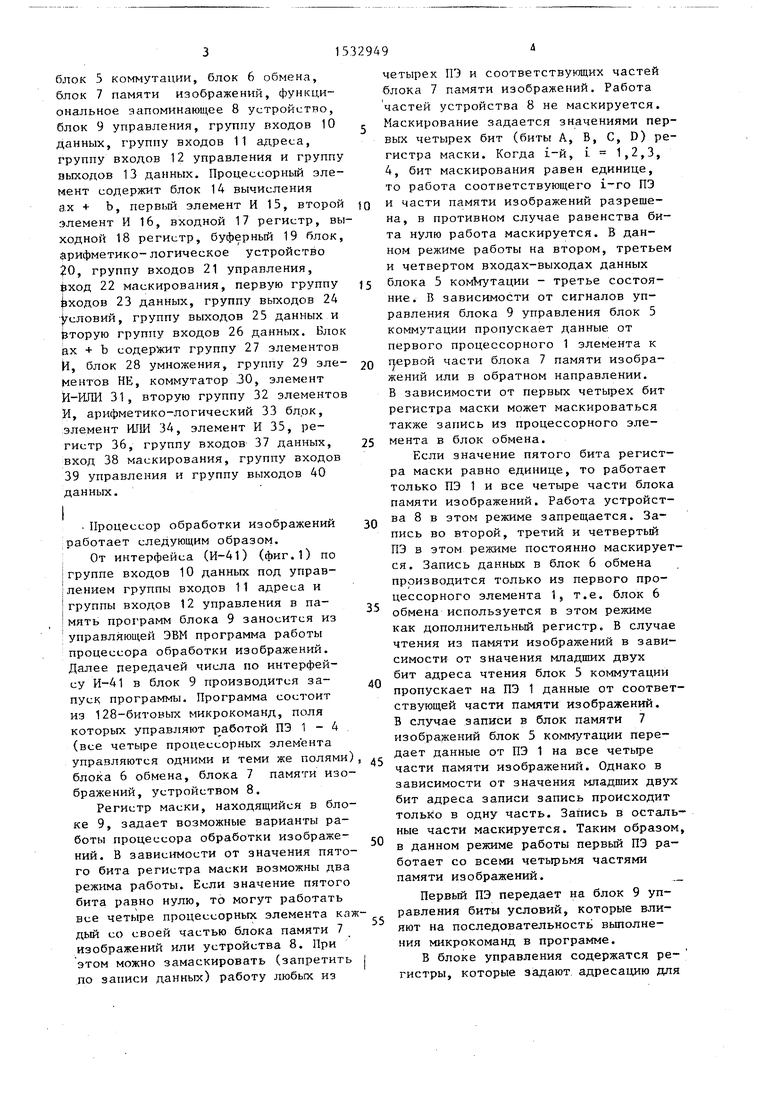

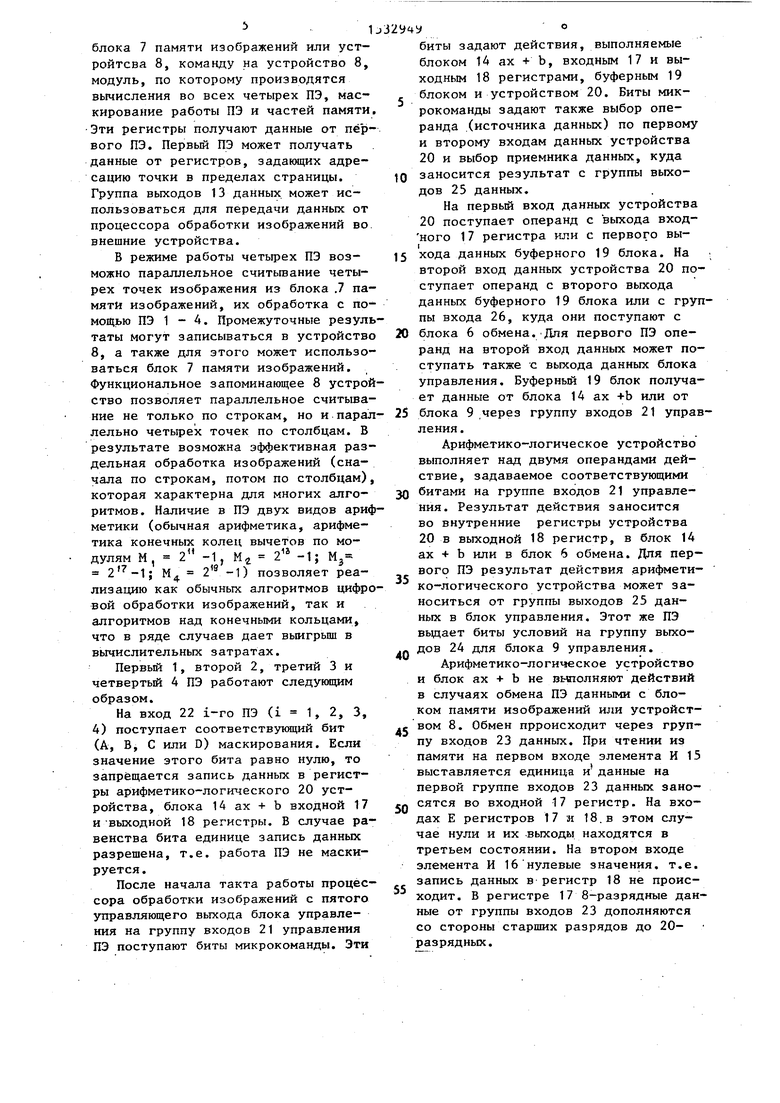

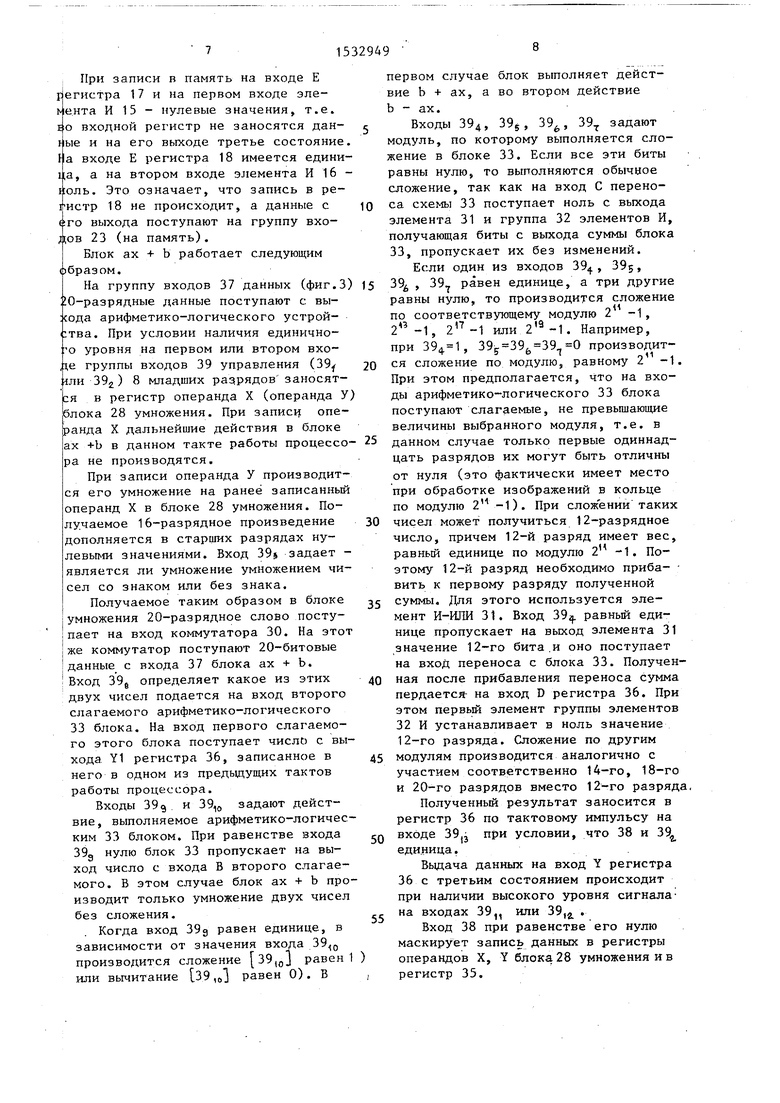

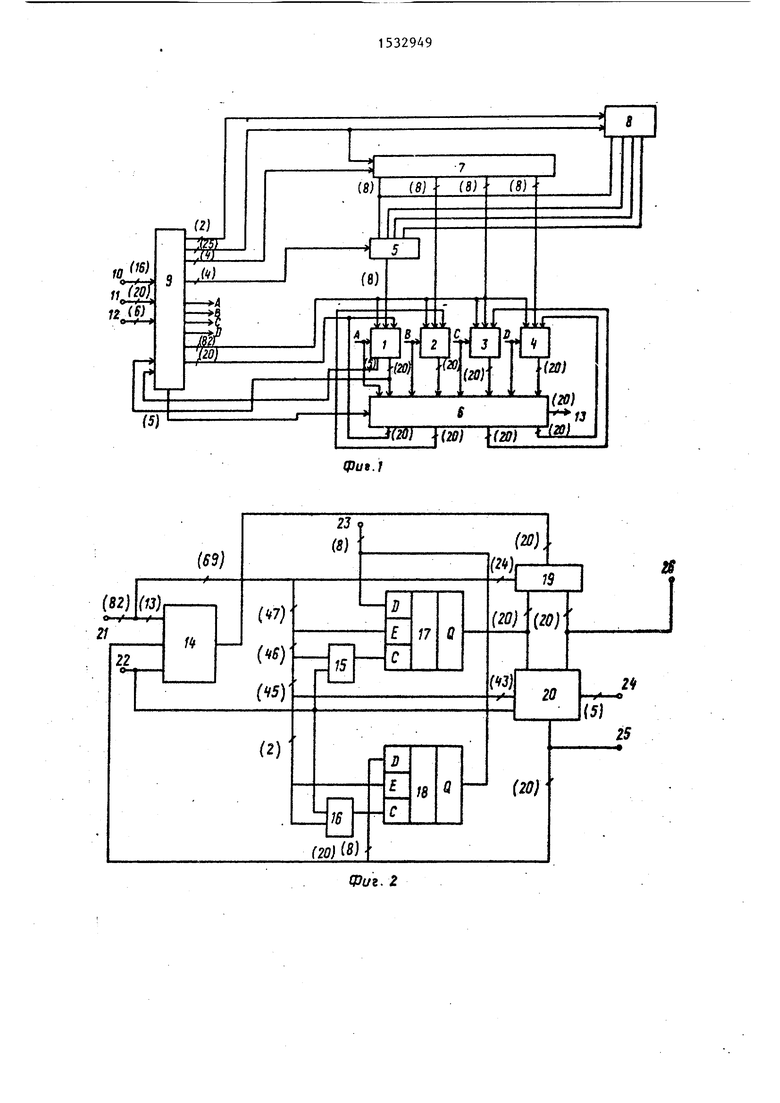

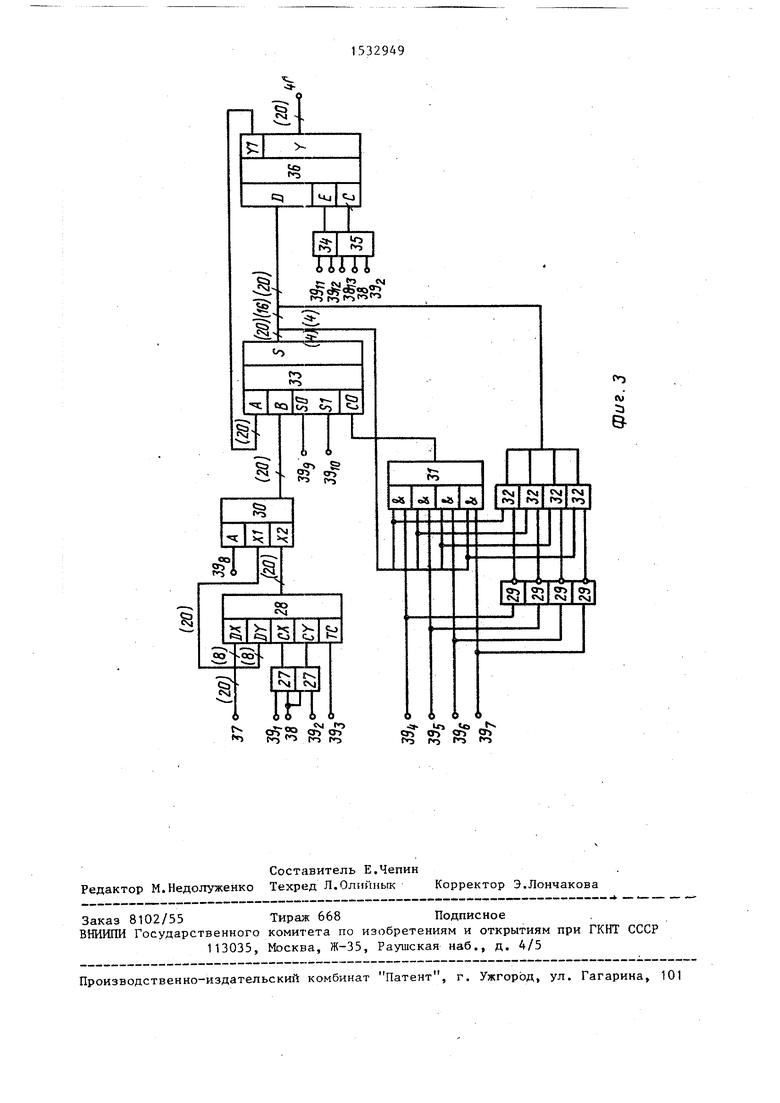

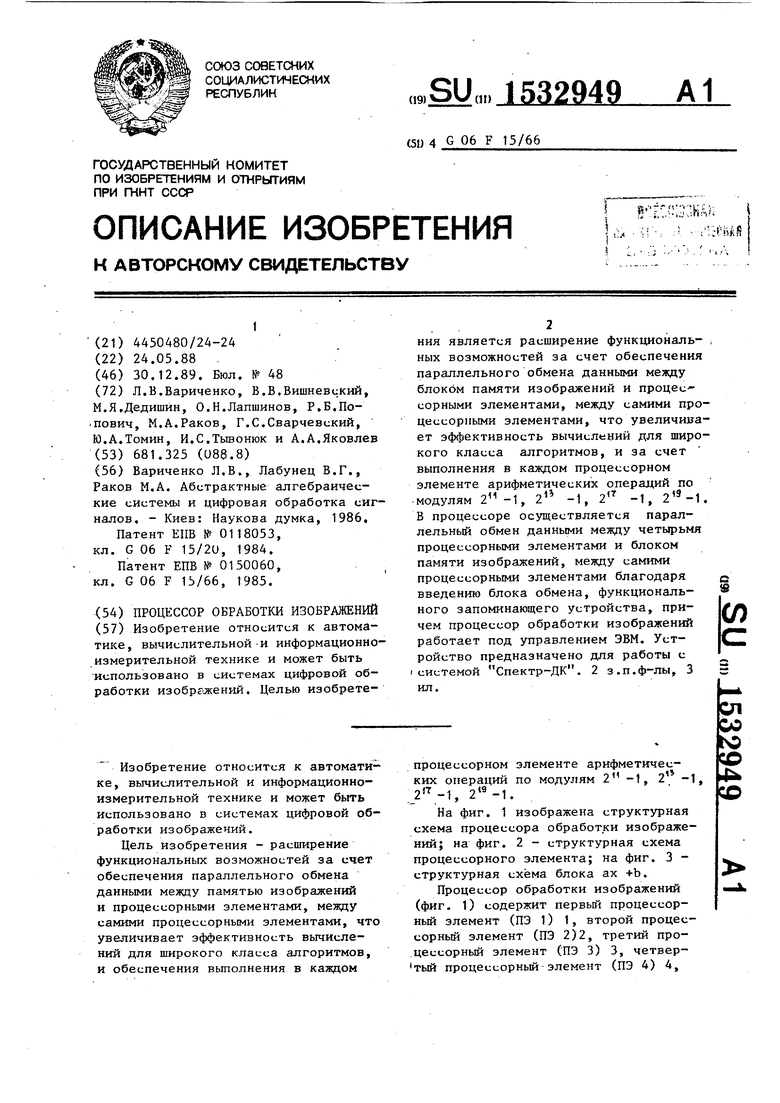

На фиг. 1 изображена структурная схема процессора обработки изображений; на фиг. 2 - структурная схема процессорного элемента; на фиг. 3 - структурная схема блока ах +Ь.

Процессор обработки изображений (фиг. 1) содержит первый процессорный элемент (ПЭ 1) 1, второй процессорный элемент (ПЭ 2)2, третий процессорный элемент (ПЭ 3) 3, четвер тый процессорный элемент (ПЭ 4) 4,

блок 5 коммутации, блок 6 обмена, блок 7 памяти изображений, функциональное запоминающее 8 устройство, блок 9 управления, группу входов 10 данных, группу входов 11 адреса, группу входов 12 управления и группу ныходов 13 данных. Процессорный элемент содержит блок 14 вычисления + b, первый элемент И 15, второй элемент И 16, входной 17 регистр, выходной 18 регистр, буферный 19 блок, арифметике- логическое устройство 0, группу входов 21 управления, Йход 22 маскирования, первую группу Јходов 23 данных, группу выходов 24 условий, группу выходов 25 данных и бторую группу входов 26 данных. Блок ах + Ъ содержит группу 27 элементов И, блок 28 умножения, группу 29 эле- Ментов НЕ, коммутатор 30, элемент И-ШШ 31, вторую группу 32 элементов И, арифметико-логический 33 блок, элемент ИЛИ 34, элемент И 35, регистр 36, группу входов 37 данных, вход 38 маскирования, группу входов 39 управления и группу выходов 40 данных.

I

Процессор обработки изображений

работает следующим образом.

От интерфейса (И-41) (фиг.1) по группе входов 10 данных под управ- лением группы входов 11 адреса и группы входов 12 управления в па- 1 мять программ блока 9 заносится из управляющей ЭВМ программа работы процессора обработки изображений. Далее передачей числа по интерфейсу И-41 в блок 9 производится запуск программы. Программа состоит из 128-битовых микрокоманд, поля которых управляют работой ПЭ 1 - 4 (все четыре процессорных элемента управляются одними и теми же полями) блока 6 обмена, блока 7 памяти изображений, устройством 8.

Регистр маски, находящийся в блоке 9, задает возможные варианты работы процессора обработки изображений. В зависимости от значения пятого бита регистра маски возможны два режима работы. Если значение пятого бита равно нулю, то могут работать все четыре процессорных элемента каждый со своей частью блока памяти 7 изображений или устройства 8. При этом можно замаскировать (запретить по записи данных) работу любых из

5 0 5

0

5

0

0

5

четырех ПЭ и соответствующих частей блока 7 памяти изображений. Работа частей устройства 8 не маскируется. Маскирование задается значениями первых четырех бит (биты А, В, С, D) регистра маски. Когда i-й, i 1,2,3, 4, бит маскирования равен единице, то работа соответствующего 1-го ПЭ и части памяти изображений разрешена, в противном случае равенства бита нулю работа маскируется. В данном режиме работы на втором, третьем и четвертом входах-выходах данных блока 5 коммутации - третье состояние. В зависимости от сигналов управления блока 9 управления блок 5 коммутации пропускает данные от первого процессорного 1 элемента к первой части блока 7 памяти изображений или в обратном направлении. В зависимости от первых четырех бит регистра маски может маскироваться также запись из процессорного элемента в блок обмена.

Если значение пятого бита регистра маски равно единице, то работает только ПЭ 1 и все четыре части блока памяти изображений. Работа устройства 8 в этом режиме запрещается. Запись во второй, третий и четвертый ПЭ в этом режиме постоянно маскируется. Запись данных в блок 6 обмена производится только из первого процессорного элемента 1, т.е. блок 6 обмена используется в этом режиме как дополнительный регистр. В случае чтения из памяти изображений в зависимости от значения младших двух бит адреса чтения блок 5 коммутации пропускает на ПЭ 1 данные от соответствующей части памяти изображений. В случае записи в блок памяти 7 изображений блок 5 коммутации передает данные от ПЭ 1 на все четыре части памяти изображений. Однако в зависимости от значения младших двух бит адреса записи запись происходит только в одну часть. Запись в остальные части маскируется. Таким образом, в данном режиме работы первый ПЭ работает со всеми четырьмя частями памяти изображений.

Первый ПЭ передает на блок 9 управления биты условий, которые влияют на последовательность выполнения микрокоманд в программе.

В блоке управления содержатся регистры, которые задают адресацию для

блока 7 памяти изображений или уст- ройтсва 8, команду на устройство 8, модуль, по которому производятся вычисления во всех четырех ПЭ, маскирование работы ПЭ и частей памяти. Эти регистры получают данные от первого ПЭ. Первый ПЭ может получать данные от регистров, задающих адресацию точки в пределах страницы. Группа выходов 13 данных может использоваться для передачи данных от процессора обработки изображений во внешние устройства.

В режиме работы четырех ПЭ возможно параллельное считывание четырех точек изображения из блока .7 памяти изображений, их обработка с помощью ПЭ 1 -4. Промежуточные результаты могут записываться в устройство 8, а также для этого может использоваться блок 7 памяти изображений. Функциональное запоминающее 8 устройство позволяет параллельное считывание не только по строкам, но и параллельно четырех точек по столбцам. В результате возможна эффективная раздельная обработка изображений (сначала по строкам, потом по столбцам), которая характерна для многих алгоритмов. Наличие в ПЭ двух видов арифметики (обычная арифметика, арифметика конечных колец вычетов по модулям М. 2й -1, М4 21i -I; M., 2 7-1: М, 2 -1)

1; М4 2 -1) позволяет реализацию как обычных алгоритмов цифровой обработки изображений, так и алгоритмов над конечными кольцами, что в ряде случаев дает выигрыш в вычислительных затратах.

Первый 1, второй 2, третий 3 и четвертый 4 ПЭ работают следующим образом.

На вход 22 1-го ПЭ (i 1, 2, 3, 4) поступает соответствующий бит (А, В, С или D) маскирования. Если значение этого бита равно нулю, то запрещается запись данных в регистры арифметико-логического 20 устройства, блока 14 ах + b входной 17 и выходной 18 регистры. В случае равенства бита единице запись данных разрешена, т.е. работа ПЭ не маскируется .

После начала такта работы процессора обработки изображений с пятого управляющего выхода блока управления на группу входов 21 управления ПЭ поступают биты микрокоманды. Эти

0

5

0

5

биты задают действия, выполняемые блоком 14 ах + Ь, входным 17 и выходным 18 регистрами, буферным 19 блоком и устройством 20. Биты микрокоманды задают также выбор операнда (источника данных) по первому и второму входам данных устройства 20 и выбор приемника данных, куда заносится результат с группы выходов 25 данных.

На первый вход данных устройства 20 поступает операнд с выхода вход- ного 17 регистра или с первого выхода данных буферного 19 блока. На второй вход данных устройства 20 поступает операнд с второго выхода данных буферного 19 блока или с группы входа 26, куда они поступают с блока 6 обмена. Для первого ПЭ операнд на второй вход данных может поступать также с выхода данных блока управления. Буферный 19 блок получает данные от блока 14 ах +Ь или от блока 9 через группу входов 21 управления.

Арифметико-логическое устройство выполняет над двумя операндами действие, задаваемое соответствующими битами на группе входов 21 управления. Результат действия заносится во внутренние регистры устройства 20 в выходной 18 регистр, в блок 14 ах + b или в блок 6 обмена. Для первого ПЭ результат действия арифметико-логического устройства может заноситься от группы выходов 25 данных в блок управления. Этот же ПЭ выдает биты условий на группу выходов 24 для блока 9 управления.

Арифметико-логическое устройство и блок ах + b не выполняют действий в случаях обмена ПЭ данными с блоком памяти изображений или устройст- , вом 8. Обмен прроисходит через группу входов 23 данных. При чтении из памяти на первом входе элемента И 15 выставляется единица и1 данные на первой группе входов 23 данных заносятся во входной 17 регистр. На входах Е регистров 17 я 18.в этом случае нули и их выходы находятся в третьем состоянии. На втором входе элемента И 16 нулевые значения, т.е. запись данных в регистр 18 не происходит. В регистре 17 8-разрядные данные от группы входов 23 дополняются со стороны старших разрядов до 20- разрядных.

0

5

0

0

5

При записи в память на входе Е регистра 17 и на первом входе элемента И 15 - нулевые значения, т.е. ЕО входной регистр не заносятся данные и на его выходе третье состояние. На входе Е регистра 18 имеется единица, а на втором входе элемента И 16 - ноль. Это означает, что запись в регистр 18 не происходит, а данные с (го выхода поступают на группу входов 23 (на память).

Блок ах + b работает следующим (Ьбразом.

На группу входов 37 данных (фиг.З) : 0-разрядные данные поступают с выхода арифметико-логического устройства. При условии наличия единично- о уровня на первом или втором входе группы входов 39 управления (39 :1ли 392) 8 младших разрядов заносят- |ся в регистр операнда X (операнда У блока 28 умножения. При записи операнда X дальнейшие действия в блоке ах +Ь в данном такте работы процессе- ра не производятся.

При записи операнда У производится его умножение на ранее записанный операнд X в блоке 28 умножения. Получаемое 16-разрядное произведение дополняется в старших разрядах нулевыми значениями. Вход 39 задает - является ли умножение умножением чисел со знаком или без знака.

Получаемое таким образом в блоке умножения 20-разрядное слово посту- 1пает на вход коммутатора 30. На этот же коммутатор поступают 20-битовые данные с входа 37 блока ах + Ь. Вход 39в определяет какое из этих двух чисел подается на вход второго слагаемого арифметико-логического 33 блока. На вход первого слагаемого этого блока поступает число с выхода Y1 регистра 36, записанное в него в одном из предыдущих тактов работы процессора.

Входы 39 g и 3910 задают действие, выполняемое арифметико-логическим 33 блоком. При равенстве входа 393 нулю блок 33 пропускает на выход число с входа В второго слагаемого. В этом случае блок ах + b производит только умножение двух чисел без сложения.

Когда вход 39g равен единице, в зависимости от значения входа производится сложение 39(0J равен I или вычитание 39,0 равен 0). В

5 0 5

0

5 0 5

0

5

первом случае блок выполняет действие b + ах, а во втором действие b - ах.

Входы 394, 395, 396, 39Т задают модуль, по которому выполняется сложение в блоке 33. Если все эти биты равны нулю, то выполняются обычное сложение, так как на вход С переноса схемы 33 поступает ноль с выхода элемента 31 и группа 32 элементов И, получающая биты с выхода суммы блока 33, пропускает их без изменений.

Если один из входов 39,,., 39s, 39Й , 39 равен единице, а три другие равны нулю, то производится сложение по соответствующему модулю 2 -1, 2м -1, 217-1 или 2(9-1. Например, при , 0 производится сложение по модулю, равному 2 -1. При этом предполагается, что на входы арифметико-логического 33 блока поступают слагаемые, не превышающие величины выбранного модуля, т.е. в данном случае только первые одиннадцать разрядов их могут быть отличны от нуля (это фактически имеет место при обработке изображений в кольце по модулю 2й -1). При сложении таких чисел может получиться 12-разрядное число, причем 12-й разряд имеет вес, равный единице по модулю 2й -1. Поэтому 12-й разряд необходимо прибавить к первому разряду полученной суммы. Для этого используется элемент И-ИЛИ 31. Вход 39. равный единице пропускает на выход элемента 31 значение 12-го бита и оно поступает на вход переноса с блока 33. Полученная после прибавления переноса сумма пердается- на вход D регистра 36. При этом первый элемент группы элементов 32 И устанавливает в ноль значение 12-го разряда. Сложение по другим модулям производится аналогично с участием соответственно 14-го, 18-го и 20-го разрядов вместо 12-го разряда.

Полученный результат заносится в регистр 36 по тактовому импульсу на входе 39)3 при условии, что 38 и 39 единица.

Выдача данных на вход Y регистра 36 с третьим состоянием происходит при наличии высокого уровня сигнала- на входах 39,, или 39,г .

Вход 38 при равенстве его нулю маскирует запись данных в регистры операндов X, Y блока 28 умножения и в регистр 35.

ормула

9 изо

15

бретения

1532949

10

блока обмена, второй вход данных первого процессорного элемента соединен с первым входом-выходом данных блока коммутации, первые входы данных второго, третьего и четвертого процессорных элементов соединены соответственно с вторым, третьим и четвертым входами-выходами блока

коммутации, а также с соответствующими вторым, третьим и четвертым входами-выходами блока памяти изображений и с соответствующими вторым, третьим и четверым входами-выходами

5 Функционального запоминающего устройства, пятый вход-выход блока коммутации соединен с первым входом-выходом памяти изображений и с первым входом-выходом функционального запо0 минающего устройства, выходы данных второго, третьего и четвертого процессорных элементов соединены соответственно с вторым, третьим и четвертым входами данных блока обмена,

5 второй, третий и четвертый выходы данных которого соединены с вторыми входами данных соответственно второго, третьего и четвертого процессорных элементов, шестой управ0 ляющий выход блока управления соединен с входом управления блока обмена, пятый выход данных которого является выходом данных устройства.

0 устройство, причем группа входов управления процессорного элемента соединена с входами управления блока вычисления ах +Ь, буферного бло5

ка, арифметико-логического устройства, входами разрешения входного и выходного регистров, первым входом первого элемента И и вторым входом второго элемента И, вход маскирования соединен с входами маскирования блока вычисления ах +Ь, арифметико- логического устройства, вторым входом первого элемента И и первым входом второго элемента И, первая группа входов данных процессорного элемента соединена с входом данных входного регистра и с выходом данных выходного регистра, вторая группа вхо-, дов данных процессорного элемента соединена с вторым выходом данных

буферного блока и с вторым входом даНных арифметико-логического уст- родства, выход данных которого соединен с входами данных выходного регистра, группа входов данных блока вычисления ах +Ь и является группой вьЬсодов данных процессорного элемента, выход данных блока вычисления ау, + Ъ соединен с входом данных буферного блока, выход второго элемента И соединен с тактовым входом выходного регистра, выход первого элемента И соединен с тактовым входом входного регистра, выход данных ко- тфрого соединен с первым выходом данных буферного блока и первым входом данных арифметико-логического

УСТрОЙСТВа, ВЫХОД УСЛОВИЯ КОТОРОГО

ярляется выходом условия процессор- нЬго элемента.

регистр, причем группа входов данкых блока вычисления ах +Ъ соединена ( входами первого и второго сомножи- геля блока умножения и с первым вхо- фом коммутатора, первый разряд группы входов управления блока вычисления ах +Ь соединен с первым входом первого элемента первой группы эле- Нентов И, второй разряд - с вторым уходом второго элемента И этой же группы и с третьим входом трехвходо- вого элемента И, третий разряд - с входом задания режима блока умножения, четвертый разряд - с вторым входом элемента И-ИЛИ и с входом первого элемента группы элементов НЕ, Пятый разряд - с четвертым входом элемента И-ИЛИ и с входом второго элемента группы элементов НЕ, шестой разряд - с шестым входом элемента И-ИЛИ и с входом третьего элемента группы элементов НЕ, седьмой разряд - с восьмым входом элемента И-ИЛИ и с входом четвертого элемента группы элементов НЕ, восьмой разряд - с входом выбора коммутатора, девятый и десятый разряды- соответственно с первым и вторым входами задания действия арифметико-лог

0

5

0

5

0

5

0

5

0

5

ческого блока, одиннадцатый и двенадцатый разряды - соответственно с первым и вторым входом элемента ИЛИ, тринадцатый разряд - с первым входом трехвходового элемента И, вход мае- , кирования соединен с первым входом второго и вторым входом первого элементов первой группы элементов И и с вторым входом трехвходового элемента И, выходы первого и второго элементов первой группы элементов И соединены соответственно с первым и вторым тактовыми входами блока умножения, выход данных которого соединен с вторым входом коммутатора, выход которого соединен с вторым входом данных арифметико-логического блока, первый -вход данных которого соединен с первым выходом данных регистра, выход элемента И-ИЛИ соединен с входом переноса арифметико- логической схемы с первого по одиннадцатый, а также тринадцатый, шестнадцатый, семнадцатый и девятнадцатый разряды выхода которого соединены с соответствующими разрядами входа данных регистра,, двенадцатый разряд - с первым входом элемента И-ИЛИ и с первым входом первого элемента второй группы элементов И, четырнадцатый разряд - с третьим входом элемента И-ИЛИ и с первым входом второго блока элемента второй группы элементов И, восемнадцатый разряд - с пятым входом элемента И-ИЛИ и с первым входом третьего элемента второй группы элементов И, двадцатый разряд - с седьмым входом элемента И-ИЛИ и с первым входом четвертого элемента второй группы элементов И, выходы первого,, второго, третьего и четвертого элементов НЕ соединены с вторыми входами соответствующих элементов второй группы элементов И, выход первого элемента второй группы элементов И соединен с двенадцатым разрядом входа данных регистра, выход второго элемента - с четырнадцатым разрядом, выход третьего элемента - с восемнадцатым разрядом, выход четвертого элемента - с двадцатым разрядом, выходы элемента ИЛИ и элемента И соединены соответственно с входом разрешения и тактовым входом регистра, второй выход данных которого является группой выходов данных блока вычисления ах+b .

Фиг. Z

J

тшт

го гое-)1

Cv

f«

rfrgo «

t 5 ro m

Л)

S

О sf sf Ј

| Вариченко Л.В., Лабунец В.Г., Раков М.А | |||

| Абстрактные алгебраические системы и цифровая обработка сигналов | |||

| - Киев: Наукова думка, 1986 | |||

| Нелинейный функциональный преобразователь | 1953 |

|

SU118053A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для правки баланса часов по плоскости | 1961 |

|

SU150060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-24—Подача