Изобретение относится к электротехнике, а именно к преобразовательной технике, и может быть использовано для управления трехфазным статическим преобразователем частоты.

Целью изобретения является повышение быстродействия устройства.

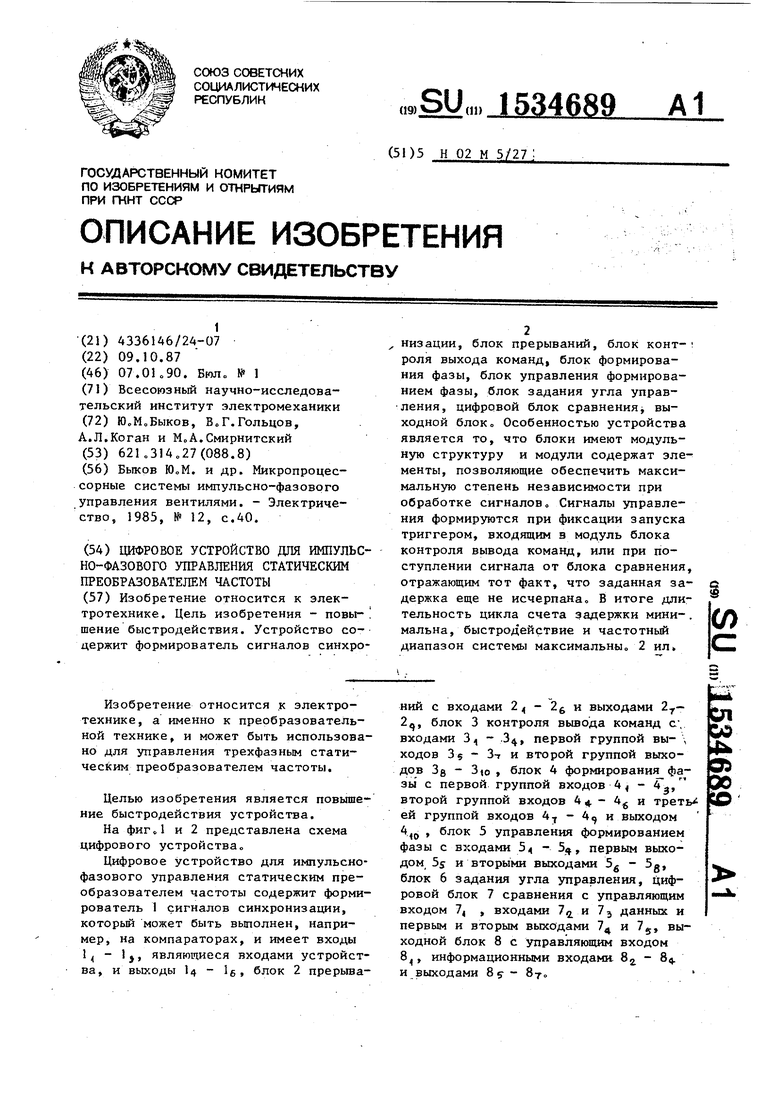

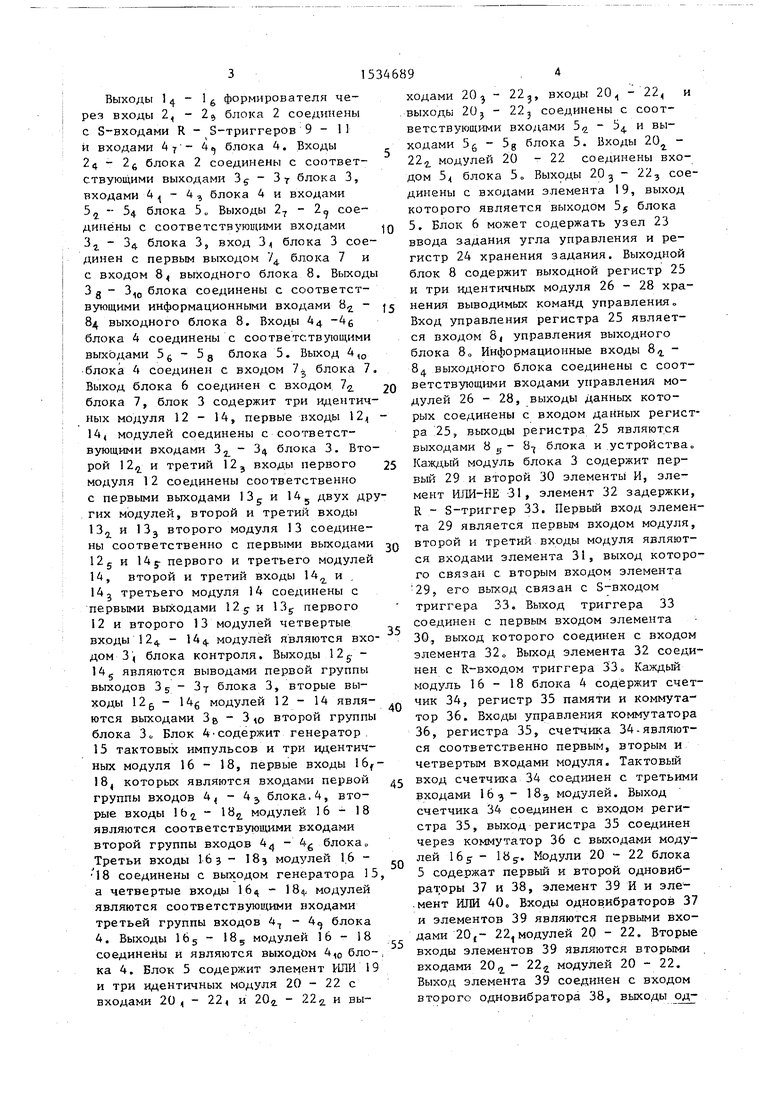

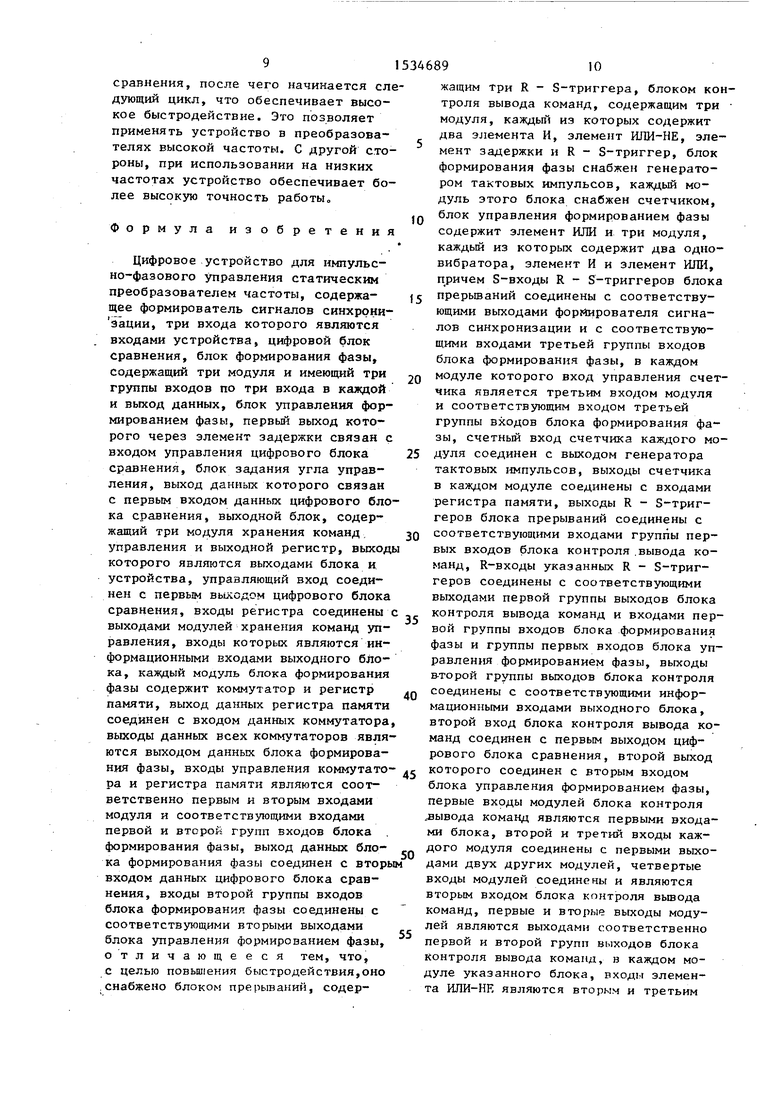

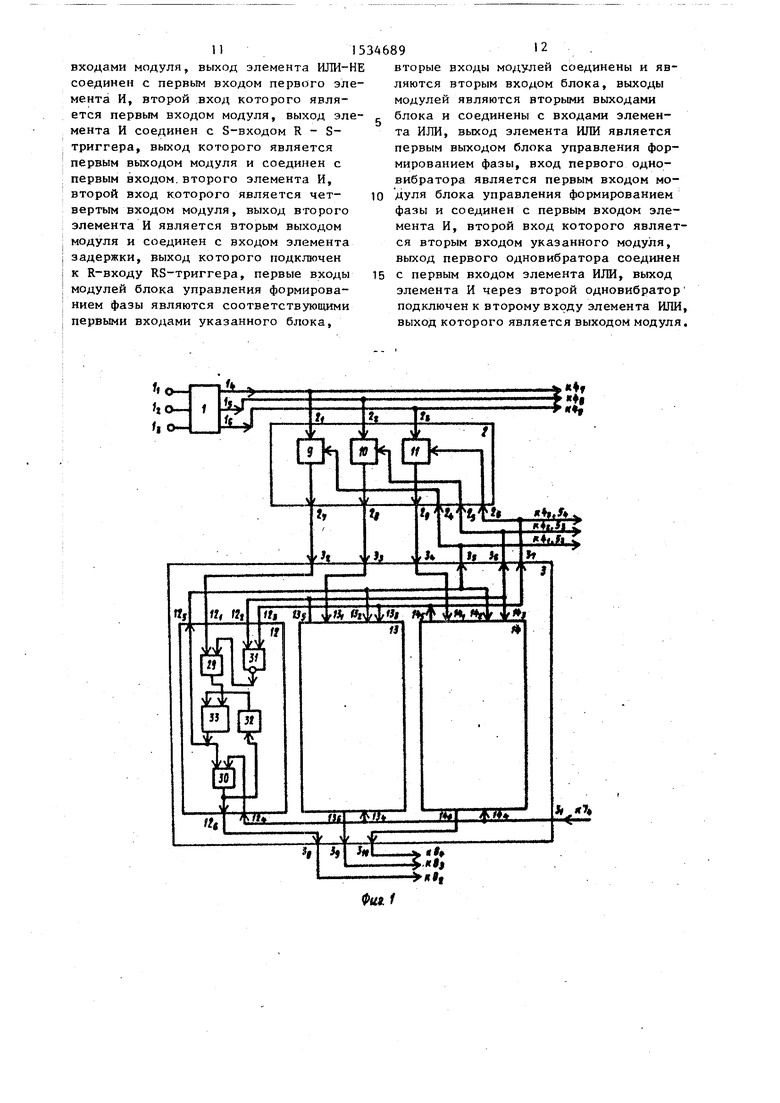

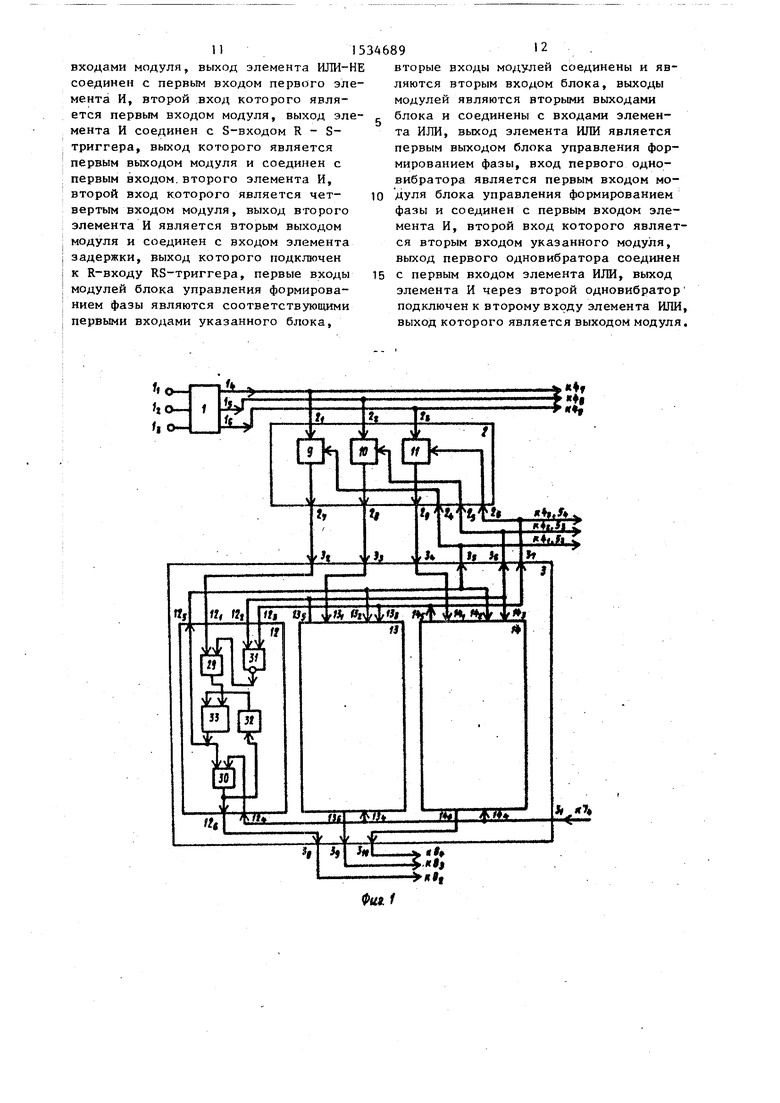

На фиг Л и 2 представлена схема цифрового устройства,,

Цифровое устройство для импульсно- фазового управления статическим преобразователем частоты содержит формирователь 1 сигналов синхронизации, который может быть выполнен, например, на компараторах, и имеет входы 1,, - 1 э, являющиеся входами устройства, и выходы Ц Ut блок 2 прерываний с входами 24 - 26 и выходами 2Г- 2Ч, блок 3 контроля вывода команд с- входами 3,, - 34, первой группой вы- , ходов 3 Зт и второй группой выходов За , блок 4 формирования фазы с первой группой входов 4 - 43, второй группой входов 4 «. 46 и треть ей группой входов 47 - и выходом 410 , блок 5 управления формированием фазы с входами 5 - 5$, первым выходом 5s и вторыми выходами 56 - 5g, блок 6 задания угла управления, цифровой блок 7 сравнения с управляющим входом 7, , входами 7й и 73 данных и первым и вторым выходами 74 и 7$, выходной блок 8 с управляющим входом 8, информационными входами 82 - 8$. и выходами 8 $ - 87„

л

W

Јь ЭЭ Х

о

Выходы 14 б формирователя через входы 2, - 25 блока 2 соединены с S-входами R - S-триггеров 9-11 и входами 4 -j - 4 блока 4. Входы 2 - 26 блока 2 соединены с соответствующими выходами 3 - 3 f блока 3, входами 4 - 4 э блока 4 и входами 5„ -- ЗА блока 5

2 - ЗА блока 5„ Выходы 27 - 2а соединены с соответствующими входами Зг - 34 блока 3, вход 34 блока 3 соединен с первым выходом 74 блока 7 и с входом 8 выходного блока 8. Выход 3g - 310 блока соединены с соответствующими информационными входами 82 - 84. выходного блока 8. Входы 44 -4g блока 4 соединены с соответствующими выходами 56 - 5д блока 5. Выход 4,0 блока 4 соединен с входом /3 блока 7 Выход блока 6 соединен с входом 1$ блока 7, блок 3 содержит три идентичных модуля 12 - 14, первые входы 12 144модулей соединены с соответствующими входами блока 3. Второй 12 и третий 123 входы первого модуля 12 соединены соответственно

с первыми выходами 135 и 145 двух др гих модулей, второй и третий входы 13а и 133 второго модуля 13 соединены соответственно с первыми выходами 12 5 и 14 j- первого и третьего модулей 14, второй и третий входы 14 и 14j третьего модуля 14 соединены с первыми выходами 125 и 13е первого 12 и второго 13 модулей четвертые входы 12 - 14, модулей являются входом 34 блока контроля. Выходы 12$

145являются выводами первой группы выходов 35 З-j- блока 3, вторые выходы 126 - 14g модулей 12 - 14 являются выходами Зе второй группы блока 3, Блок 4 содержит генератор 15 тактовых импульсов и три идентичных модуля 16 - 18, первые входы 16f 184 которых являются входами первой группы входов 4 - 43 блока..4, вторые входы 1 fa г - 18а модулей 16 - 18 являются соответствующими входами второй группы входов 44 - 46 блока Третьи входы 16 з 18} модулей 16 соединены с выходом геш;ратора 15 а четвертые входы 16 - 18. модулей являются соответствующими входами третьей группы входов 47 - 4 блока 4. Выходы 16 5 8 5 модулей 16 - 18 соединены и являются выходом 4,0 блока 4. Блок 5 содержит элемент ИЛИ 19 и три идентичных модуля 20 - 22 с входами 20 - 22 и 20г - 222. и вы

10

20

1525

346894

ходами 20з - 22 3, входы 20 - 22 и выходы 20 з - 22 соединены с соответствующими входами 52 - b и выходами 56 - 5g блока 5. Входы 20г - 22г модулей 20 - 22 соединены входом 5,( блока 5„ Выходы 20 - 223 соединены с входами элемента 19, выход которого является выходом 5S блока 5. Блок 6 может содержать узел 23 ввода задания угла управления и регистр 24 хранения задания. Выходной блок 8 содержит выходной регистр 25 и три идентичных модуля 26 - 28 хранения выводимых команд управления„ Вход управления регистра 25 является входом 8| управления выходного блока 8о Информационные входы 8г - 84. выходного блока соединены с соответствующими входами управления модулей 26 - 28, выходы данных которых соединены с входом данных регистра 25, выходы регистра 25 являются

0

5

5

0

5

0

5

выходами

В5В7 блока и устройства. Каждый модуль блока 3 содержит первый 29 и второй 30 элементы И, элемент ИЛИ-НЕ 31, элемент 32 задержки, R - S-триггер 33. Первый вход элемента 29 является первым входом модуля, второй и третий входы модуля являются входами элемента 31, выход которого связан с вторым входом элемента

29,его выход связан с S-входом триггера 33. Выход триггера 33 соединен с первым входом элемента

30,выход которого соединен с входом элемента 32„ Выход элемента 32 соединен с R-входом триггера 33, Каждый модуль 16 - 18 блока 4 содержит счетчик 34, регистр 35 памяти и коммутатор 36. Входы управления коммутатора 36, регистра 35, счетчика 34-являются соответственно первым, вторым и четвертым входами модуля. Тактовый вход счетчика 34 соединен с третьими входами 16з 183 модулей. Выход счетчика 34 соединен с входом регистра 35, выход регистра 35 соединен через коммутатор 36 с выходами модулей 1&5 185-. Модули 20 - 22 блока

5 содержат первый и второй одновиб- раторы 37 и 38, элемент 39 И и элемент ИЛИ 40. Входы одновибраторов 37 и элементов 39 являются первыми входами 20,- 22,модулей 20 - 22. Вторые входы элементов 39 являются вторыми входами 20г - 22г модулей 20 - 22. Выхоц элемента 39 соединен с входом второго одновибратора 38, выходы одновибраторов 37 и 38 соединены с входами элемента 40. Выходы элементов

20322, мо40 являются выходами дулей 20 - 22. Выход 55 через элемент 41 задержки соединен с входом

В работе устройства возможны два режима, отличающиеся величиной угла управления

В первом режиме к моменту формирования очередного сигнала синхронизации отсчет угла управления закончен, соответствующая команда управления вентилями преобразователя выве- . дена и блоки устройства находятся в исходном состоянии, т.е. все триггеры сброшены, счетчики не работают, выходы регистров 35 в модулях блока 4 отключены коммутаторами 36 от выхода 4 «о , на всех выходах элементов 29, 30, 39 и 40 установлен уровень нуля, на выходах элементов 31 - уровень единицы. Пусть на входе 1 мгно10

15

33 в первом модуле 12 будет сброшен- в состояние О. Сигнал с выхода триггера 33 через первый выход 12S первого модуля 12 и первый выход 3 первой группой выходов блока 3 поступает также на первый вход 4 первой группы входов блока 4 и первый вход 5г первой группы входов блока 5. В результате с входа 4, блока 4 через вход 16, модуля 16 сигнал поступает на вход управления коммутатора 36 и переводит его в открытое состояние. Подготовлен канал для вывода данных из регистра 35 в виде комбинации сигналов на втором входе

7$ блока 7 о Сигнал с входа

5а блока

5 поступает на вход одновибратора 37, он вырабатывает сигнал, который

20

проходит через 20

элемент 40, поступает на выход 2(} модуля 20, на выход 56 группы выходов блока 5„ С выхода 56 блока 5 через вход 44 блока 4, вход 162 модуля 16

сигнал поступает на

венное значение напряжения соответст- 25 вход управления регистра 35 и обес- вует порогу срабатывания компаратора печивает запись кода текущего значе- формирователя 1. С выхода Ц формиро- ния фазы, отсчитанного счетчиком 34.

Полученный таким образом в регистре 35 код поступает на второй вход 7з

вателя сигнал поступает на вход / блока 2 и вход 4 7 третьей группы

5

33 в первом модуле 12 будет сброшен- в состояние О. Сигнал с выхода триггера 33 через первый выход 12S первого модуля 12 и первый выход 3 первой группой выходов блока 3 поступает также на первый вход 4 первой группы входов блока 4 и первый вход 5г первой группы входов блока 5. В результате с входа 4, блока 4 через вход 16, модуля 16 сигнал поступает на вход управления коммутатора 36 и переводит его в открытое состояние. Подготовлен канал для вывода данных из регистра 35 в виде комбинации сигналов на втором входе

7$ блока 7 о Сигнал с входа

5а блока

5 поступает на вход одновибратора 37, он вырабатывает сигнал, который

проходит через 20

элемент 40, поступает на выход 2(} модуля 20, на выход 56 группы выходов блока 5„ С выхода 56 блока 5 через вход 44 блока 4, вход 162 модуля 16

сигнал поступает на

вход управления регистра 35 и обес- печивает запись кода текущего значе- ния фазы, отсчитанного счетчиком 34.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| ЛОГИЧЕСКИЙ МУЛЬТИКОНТРОЛЛЕР С РАСПРЕДЕЛЕННЫМ ПАРАЛЛЕЛЬНО-КОНВЕЙЕРНЫМ БАРЬЕРНЫМ СИНХРОНИЗАТОРОМ | 2010 |

|

RU2450328C1 |

| Устройство для обработки графической информации | 1988 |

|

SU1674222A1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 2007 |

|

RU2336556C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

Изобретение относится к электротехнике. Цель изобретения - повышение быстродействия. Устройство содержит формирователь сигналов синхронизации, блок прерываний, блок контроля выхода команд, блок формирования фазы, блок 5 управления формированием фазы, блок задания угла управления, цифровой блок сравнения, выходной блок. Особенностью устройства является то, что блоки имеют модульную структуру и модули содержат элементы, позволяющие обеспечить максимальную степень независимости при обработке сигналов. Сигналы управления формируются при фиксации запуска триггером, входящим в модуль блока контроля вывода команд, или при поступлении сигнала от блока сравнения, отражающим тот факт, что заданная задержка еще не исчерпана. В итоге длительность цикла счета задержки минимальна, быстродействие и частотный диапазон системы максимальны. 2 ил.

входов блока 4. С входа 4 рез четвертый вход 16 модуля I6 поступает на вход управления счетчика 34, устанавливает его в исходное положение и запускает его. С входа 2.1 блока 2 сигнал поступает на вход триггера 9 и устанавливает его в состояние 1 на выходе. Время переключения триггера 33 выбирается несколько большим длительности сигнала синхронизации для исключения одновременного появления сигналов на входах триггеров блока 2. С выхода триггера 9 через выход 2Т блока 2 сигнал поступает на вход И4 блока 3, первый вход 12f первого модуля 12 и первый вход элемента 29. На втором 12г и третьем 123 входах модуля 12 в это время поддерживаются сигналы, в результате чего на выходе элемента 31 вырабатывается сигнал 1, поступающий на второй вход элемента 29. С его выхода сигнал поступает на S-вход триггера 33 и устанавливает его в состояние Выходной сигнал триггера поступает на первый выход 2ff первого модуля 12, вторые входы 132 и 14$. модулей 13 и 14, блокируя восприятие возможных следующих прерываний до того момента, когда триггер

7 сигнал че- 30 блока 7. Сигнал с выхода 203 модуля

35

20, вызвавший запись данных в регистр 35, через элемент 19 поступает на выход 55 блока 5 и через элемент 41 на вход 7 блока 7. Величина задержки элемента 41 выбирается боль шей времени установления состояния в регистре 35. По сигналу на входе 7{ блок 7 осуществляет сравнение данных поступающих через первый 72 и второй 3 входы. В результате работы блока схемы сравнения на одном из ее выходов - первом 7 4 или втором 75 - вырабатывается сигнал, причем сигнал на выходе 7$ соответствует случаю, 45 когда текущее значение фазы больше или равно заданному блоком 6 углу управления, сигнал на выходе 15 соответствует случаю, когда текущее значение фазы меньше за/данного . Пусть имеет место последний случай. Сиг40

50

нал с выхода 75 через вход 5 блока 5 поступает на вторые входы 20 2 - 22 модулей 20 - 22, но поскольку только в модуле 20 на первом входе

55

20

4 имеет место сигнал, то только

там второй одновибратор 38 вырабатывает сигнал, который через элемент 40 поступает по упомянутой ранее цепи на вход управления регистра 35 и

5

20, вызвавший запись данных в регистр 35, через элемент 19 поступает на выход 55 блока 5 и через элемент 41 на вход 7 блока 7. Величина задержки элемента 41 выбирается большей времени установления состояния в регистре 35. По сигналу на входе 7{ блок 7 осуществляет сравнение данных, поступающих через первый 72 и второй 3 входы. В результате работы блока 7 схемы сравнения на одном из ее выходов - первом 7 4 или втором 75 - вырабатывается сигнал, причем сигнал на выходе 7$ соответствует случаю, 5 когда текущее значение фазы больше или равно заданному блоком 6 углу управления, сигнал на выходе 15 соответствует случаю, когда текущее значение фазы меньше за/данного . Пусть имеет место последний случай. Сиг0

0

нал с выхода 75 через вход 5 блока 5 поступает на вторые входы 20 2 - 22 модулей 20 - 22, но поскольку только в модуле 20 на первом входе

20

4 имеет место сигнал, то только

там второй одновибратор 38 вырабатывает сигнал, который через элемент 40 поступает по упомянутой ранее цепи на вход управления регистра 35 и

организует запись нового значения фазы, которое, как и предыдущее, сравнивается с помощью блока 7 сравнения с заданием блока 60 Когда в очередном цикле сравнения вырабатывается сигнал на выходе 7,он поступит на вход 3 блока 3 и на четвертые входы 124 модулей 12 - 14, а в модулях - на вторые входы вторых элементов 30, но только в первом модуле 12 на втором входе элемента 30 поддерживается сигнал, обеспечивающий вывод через этот элемент сигнала на выход 126 и далее через выход 3g блока 3, на вход 8 блока 8, в результате чего формируется команда управления путем подключения одного из модулей 26, 27 или 28 блока 8 к входу регистра 25„ Вывод команды осуществляется регистром 25 в соответствии с сигналом на его управляющем входе 8,. Сигнал с выхода элемента 30 модуля 12 поступает через элемент 32 задержки на R-вход триггера 33, в ре зультате чего он переходит в исходное состояние и устройство готово к обработке очередного сигнала синхронизации. При формировании сигнало синхронизации на втором или третьем выходах 1у или 16 блока 1 работа происходит аналогично, только активные сигналы вырабатывают соответственно второй или третий триггеры 10 или 11 блока 2, вторые или третьи модули в блоках 3, 4, 5и8.

Во втором режиме работы к моменту формирования очередного сигнала синхронизации - пусть это будет сигнал

на выходе 1,. блока

фаза, отсчитанная счетчиком 34 и записанная в очередном цикле в регистры 35 меньше заданного в блоке 6 угла управления. Команда, соответствующая сигналу синхронизации с выхода 14 блока 1, еще не выведена, триггер 33 установлен в 1 на выходе. Сигнал синсостояние

хронизации с выхода 1 через вход 4р блока 4 и вход 17 модуля 17 поступает на вход управления счетчика 34, устанавливает его в исходное положение и тапускает его, Начинается отсчет фазы во втором канале. Сигнал синхронизации с выхода 1 через вход 2„ блока 2 поступает также на S-вход триггера 10. Он переходит в состояние 1 на выходе. Этот ситная с выхода 2 - блока 2 через вход 35 блока 3 и вход 13 модупя 13 поступает на

5

0

0

5

0

5

0

5

один из входов элемента 29. На входе 13,j модуля 13 в это время поддерживается сигнал 1, поступающий с выхода 12s модуля 12. На выходе элемента 31 этому сигналу -соответствует сигнал О, который поступает на второй вход элемента 29, что препятствует дальнейшему прохождению сигнала, поступившего на первый вход Между тем продолжаются циклы считывания текущих значений счетчика 34 в регистр 35, вывод их через коммутатор 36 на второй вход блока 7 и сравнение их с заданием, поступающим на первый вход этого блока Очередной цикл начинается сразу же по окончании предыдущего вывода сигнала на выход 75 блока 7„ Этот сигнал поступает на вход 5, блока 5 и далее вызывает активные действия только в модуле 20, так как только у него на первом входе поддерживается сигнал 1. Последовательность действий аналогична описанной выше для первого случая. После того, как текущее значение фазы достигнет заданной величины, будет выведен сигнал на выход 7 блока 7, аналогично описанному ранее будет выведена команда на выход устройства и триггер 33 в модуле 12 переведен в состояние 0, В результате сигнал на входе 13 модуля 13 принимает значение О, снимает запрет на прохождение сигнала с входа 13( через элемент 29 на установку триггера 33 в модуле 13. Дапее работа осуществляется аналогично описанному, но в ней участвуют триггер 10, модули 13, 17, 21 и 27.

Таким образом, работа устройства для импульсно-фазового управления преобразователем основана на вертикальном принципе. Отсчет фазового угла в каналах устройства ведется независимо параллельно Общие элементы устройства используются только для периодического сравнения текущего и заданного значений фазы и угла управления и принятия решений о моменте формирования сигналов управлений Длительность цикла измерения текущего значения фазы и сравнения его с заданным не связана с тактовой частотой измерения фазы и определяется только временем, непосредственно необходимым для ввода сравниваемых значений, выполнения операции сравнения и принятия решения по результатам

сравнения, после чего начинается следующий цикл, что обеспечивает высокое быстродействие. Это позволяет применять устройство в преобразователях высокой частоты. С другой стороны, при использовании на низких частотах устройство обеспечивает более высокую точность работы

Формула изобретения

Цифровое устройство для нмпульс- но-фазового управления статическим преобразователем частоты, содержащее формирователь сигналов синхрони- эации, три входа которого являются входами устройства, цифровой блок сравнения, блок формирования фазы, содержащий три модуля и имеющий три группы входов по три входа в каждой и выход данных, блок управления формированием фазы, первый выход которого через элемент задержки связан с входом управления цифрового блока сравнения, блок задания угла управления, выход данных которого связан с первым входом данных цифрового блока сравнения, выходной блок, содержащий три модуля хранения команд управления и выходной регистр, выходы которого являются выходами блока и устройства, управляющий вход соединен с первым выходом цифрового блока сравнения, входы регистра соединены выходами модулей хранения команд управления, входы которых являются информационными входами выходного блока, каждый модуль блока формирования фазы содержит коммутатор и регистр памяти, выход данных регистра памяти соединен с входом данных коммутатора выходы данных всех коммутаторов являются выходом данных блока формирования фазы, входы управления коммутато- ,с которого соединен с вторым входом

блока управления формированием фаз первые входы модулей блока контрол вывода команд являются первыми вхо ми блока, второй и третий входы ка дого модуля соединены с первыми вы дами двух других модулей, четверты входы модулей соединены и являются вторым входом блока контроля вывод команд, первые и вторые выходы мод лей являются выходами соответствен первой и второй групп выходов блок контроля вывода команд, в каждом м дуле указанного блока, входы элеме та ИЛИ-НЕ являются вторым и третьим

ра и регистра памяти являются соответственно первым и вторым входами модуля и соответствующими входами первой и втсроь групп входов блока формирования фазы, выход данных блока формирования фазы соединен с втор входом данных цифрового блока сравнения, входы второй группы входов блока формирования фазы соединены с соответствующими вторыми выходами блока управления формированием фазы, отличающееся тем, что, с целью повышения быстродействия,оно снабжено блоком прерываний, содер0

5

0

5

0

5

0

жащим три R - S-триггера, блоком контроля вывода команд, содержащим три модуля, каждый из которых содержит два элемента И, элемент Ш1И-НЕ, элемент задержки и R - S-триггер, блок формирования фазы снабжен генератором тактовых импульсов, каждый модуль этого блока снабжен счетчиком, блок управления формированием фазы содержит элемент ИЛИ и три модуля, каждый из которых содержит два одно- вибратора, элемент И и элемент ИЛИ, причем S-входы R - S-триггеров блока прерываний соединены с соответствующими выходами формирователя сигналов синхронизации и с соответствующими входами третьей группы входов блока формирования фазы, в каждом модуле которого вход управления счетчика является третьим входом модуля и соответствующим входом третьей группы входов блока формирования фазы, счетный вход счетчика каждого модуля соединен с выходом генератора тактовых импульсов, выходы счетчика в каждом модуле соединены с входами регистра памяти, выходы R - S-триггеров блока прерываний соединены с соответствующими входами группы первых входов блока контроля вывода команд, R-входы указанных R - S-триггеров соединены с соответствующими выходами первой группы выходов блока контроля вывода команд и входами первой группы входов блока формирования фазы и группы первых входов блока управления формированием фазы, выходы второй группы выходов блока контроля соединены с соответствующими информационными входами выходного блока, второй вход блока контроля вывода команд соединен с первым выходом цифрового блока сравнения, второй выход

0

5

блока управления формированием фазы, первые входы модулей блока контроля вывода команд являются первыми входами блока, второй и третий входы каждого модуля соединены с первыми выходами двух других модулей, четвертые входы модулей соединены и являются вторым входом блока контроля вывода команд, первые и вторые выходы модулей являются выходами соответственно первой и второй групп выходов блока контроля вывода команд, в каждом модуле указанного блока, входы элемента ИЛИ-НЕ являются вторым и третьим

входами модуля, выход элемента ИЛИ-НЕ соединен с первым входом первого элемента И, второй вход которого является первым входом модуля, выход элемента И соединен с S-входом R - S- триггера, выход которого является первым выходом модуля и соединен с первым входом второго элемента И, второй вход которого является четвертым входом модуля, выход второго элемента И является вторым выходом модуля и соединен с входом элемента задержки, выход которого подключен к R-входу RS-триггера, первые входы модулей блока управления формированием фазы являются соответствующими первыми входами указанного блока,

ff t l

вторые входы модулей соединены и являются вторым входом блока, выходы модулей являются вторыми выходами блока и соединены с входами элемента ИЛИ, выход элемента ИЛИ является первым выходом блока управления формированием фазы, вход первого одно- вибратора является первым входом моДУЛЯ блока управления формированием фазы и соединен с первым входом элемента И, второй вход которого является вторым входом указанного модуля, выход первого одновибратора соединен

5 с первым входом элемента ИЛИ, выход элемента И через второй одновибратор подключен к второму входу элемента ИЛИ, выход которого является выходом модуля.

Г

От регулятора

| Быков Ю.М | |||

| и др | |||

| Микропроцессорные системы импульсно-фазового управления вентилями | |||

| - Электричество, 1985, № 12, с.40. |

Авторы

Даты

1990-01-07—Публикация

1987-10-09—Подача