Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, может быть использовано в регистрирующей электронной аппаратуре для измерения аналоговых сигналов.

Цель изобретения - уменьшение аппаратных средств.

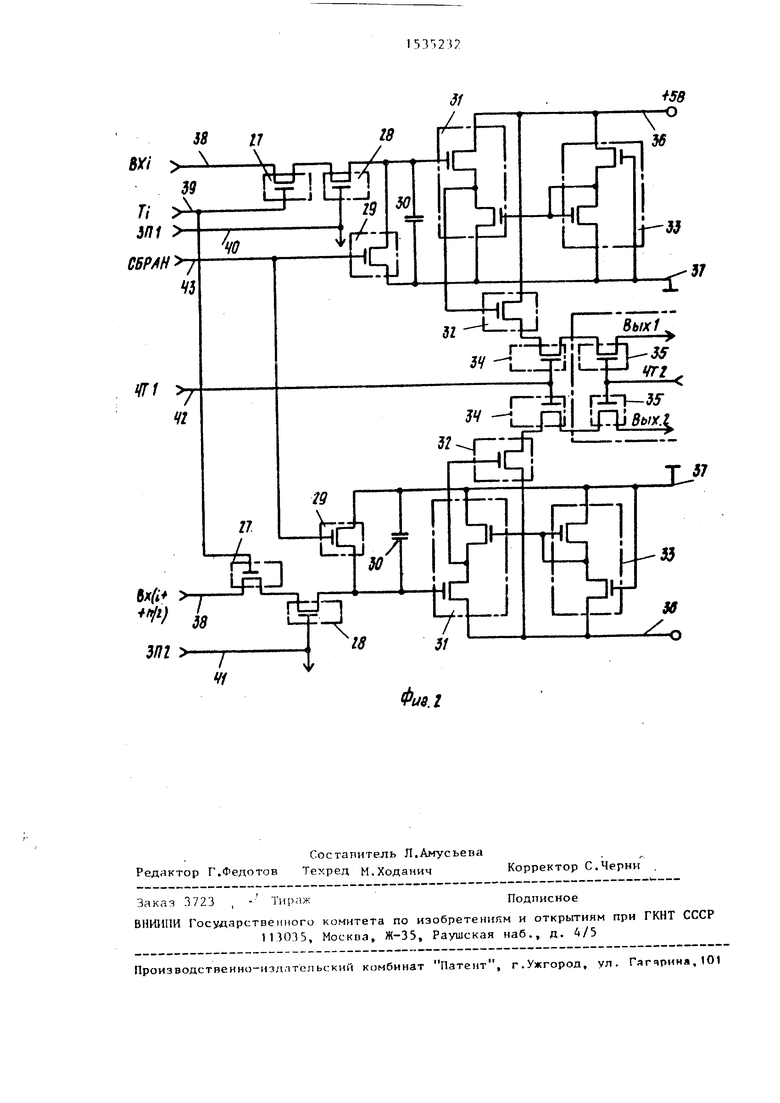

На фнг.1 изображена функциональная -хема предложенного устройства; на фиг.2 - электрическая схема ячейки ансгпогопой памяти с двойной блокировкой информации на входе и двойной выборкой на шгходе.

Устройство содержит матричный накопители 1 , рачдепенныи на под- матрицм 2-5, сдвиговые регистры 6-8, элементы И 9-13, триггер 14 управления чтением, преобразователь 15 уровня сигналов, генератор 16 тактовых

импульсов, делитель 17 частоты, триггеры 18 и 19 управления записью, триггер 20 чет-нечет, формирователь 21 сигналов, мультиплексоры 22 и 23, вход 24 сброса накопителя 1, входы 25 и 26 сброса устройства.

Ячейка аналоговой памяти ( на фиг,2 приведены две ячейки аналоговой памяти ) накопителя 1 содержит входные ключи 27 и 28, ключ 29 сброса, накопительный элемент на конденсаторе 30, истоковые повторители 31 и 32, генератор 33 тока, выходные ключи 34 и-35, пины 36 и 37 питания, информационный вход 38 и тактирующий вход

39ячейки аналоговой памяти, входы

40и 4 управпення записью, вход 42 управления чтением, вход 43 сброса

НЯКОПИТРПЯ.

ел

со ел

N9

00 N9

Устройство работает следующим образом. Перед началом работы подают сигнал сброса с пходя 25 ня триггеры 18 и 19 и сдвиговые регистры 6-8, чтобы принести их л исходное состояние, ч выполняют аналоговый сброс ячек памяти матричного накопителя 1 через параллельные ключи 29 (фиг.2). В режиме записи входные аналоговые сигналы положительной полярности поступают на n-входы. По сигналу записи включается триггер 18 (ЗП1), который разблокирует л п/2 затворов транзисторов ключей 28 (строк) и разрешает сдвиговое регистру 6 через преобразователь 15 стробиро- вать значение п входных аналоговых сигналов. В момент первого такта в п ячеек первой строки, открывая клю чи 27 временного с;гробирования двух соседних ячеек столбцов, записывают первые значения п аналоговых сигналов. Процесс записи продолжается таким образом на п/2 тактов, заломи- пая п п/2 значений аналоговых сигналов. По заднему фронту п/2 такта включается триггер 19 (ЗП2) и происходит дальнейшее стробирование элементов строк с n/2+l до п. В нако- питсль 1 записываются п п значени аналоговых сигналов. После и-го такта включаются триггеры 18 и 19, и устройство переходит в режим хранения. этом все ключи накопителя 1 км рыты, Режим чтения аналоговой информации происходит только по окончании режимов записи и.хранения. В э-гом режиме включают триггер 14 и

подают сигнал старт на входы первых триггеров регистров 7 и 8 с формрователя 21. Поделенная тактовая частота с делителя 17 устанавливает первые триггеры в состояния 1 регистров 7 и 8. При этом считывают первые две аналоговые ячейки памяти, принадлежащие первой строке и первым двум соседним столбцам (1 и 2) и подматрицам 2, 3 и 4, 5. Под действием тактовой частоты сдвиговый регистр 7 стробирует последую щие строки двух соседних столбцов (1 н 2), с. которых аналоговая информация-поступает на выходы (вых.1 и вых.2) соответственно. Сдвиговый регистр 7 стробирует п строк двух соседних столбцов за п тактов. По заднему «Ьронту n-го тактового импульса сдвиговый регистр 8 пере„-

15

.« 25 ,- 35

40

45

55

50

ключаптсп на следующую пару двух соседних столбцов. Таким образом, полное считывание аналоговой информации с матричного накопителя 1 происходит за п п/2 тактов, а сдвиговый регистр 8 содержит в два раза меньшее число элементов. По окончании режима чтения устройство снова приходит в режим хранения, из которого можно опять начать запись яна- логовой информации или ее чтение.

Введение новых элементов, разделение накопителя на подматрицы, реализация устройства на ячейках с двойной блокировкой по входу и двойной выборкой по выходу и виод дополнительных элементов позволяет сократить число элементов в функциональных узлах управления, что, в свою очередь, упрощает узлы управления, совершенствует топологию матричного накопителя на кристалле, уменьшает размеры кристалла и повьпиает скорость считывания аналоговых сигналов. Использование описанного устройства в многоканальных системах пропорциональных и дрейфовых камер позволяет получить следующие преимущества: низкую стоимость канала изме рений аналоговых сигналов, высокую плотность компоновки блоков измерений, сокращение аналого-цифровых преобразователей при тех же разрешающей способности и динамическом диапазоне измерений значений амплитуд аналоговых сигналов в цифре.

Формула изобретения

1. Аналоговое запоминающее устройство, содержащее матричный накопитель, информационные входы столбцов которого являются информационными входами устройства, преобразователь уровня сигналов, выходы которого соединены с тактирующими входами матричного накопителя, первый сдвиговый регистр, первый выход которого соединен с входом преобразователя уровня сигналов, первый н второй элементы И, первые входы которых соединены с выходом генератора тактовых импульсов, третий элемент И, входы которого соединены с выходами первого н второго элементов И, выход третьего элемента И соединен с тактирующим входом первого сдвигового регистра, второй сдвиговый регистр,

4г.

iinjl l II- ОД KOrnpniO ОГМЦПК И Г

np.i плтющпми входами пергото и второ- i с к ш- П1Пле1гсорор, чегпергыч элемент И, выход которого соединен г информационным входом второго сдвигового регистра, делитель члгтпты, пыход которого соединен с первым входом четвертого элемента И. информационные входы мультиплексоров соединены г выходами матричного ьмкспитепя, тпешй сдвиговый рпистр, информационный пход которого соединен с вторым пнходом второго сдвигового рогигтр-т, РХОДЫ оброс--) сдвиговых регистров оРъ Лнггни и нвпиются пеп - тити входом сбро( n устройства, выходы мультиплексоров чтпчютсч выходами

УСГроЙСТПЛ, Третьего сдвигового регистра т г в одамн строк МЧТРИЧНОГО НЛКОПЧТРЧП, ч,п:од гс-не рлторт так юрых пгчгчц (-.-г) гопиир с- ичгнюм допнтот чягтотм, пход горосп 1:оторс то яч- г Т(Ч входим сброса накопнтепн, отличающееся ТРИ, что, с ЦРГТЬЮ упрощения, п него пврнртн ДРЯ триггера управления тяпигью, триггер управления чтением, пятый -мтрмеш И, трш- гер опрлдепенчя чег-нр- ет и форми- рорчтсп). гипппо 1, т г: д которого «О ДИНРН с тг:од-ь т установки единшда

MODOT O И Tpf P,O Г(Г Ы1 ОГЧ-Ь-С РРГНСТpoij, пход форм м, rr-jtfi игпчлон сое- ;ч1Нгн с Т(годом i пи ч on управлении чтс)1чс и и пто..ым руодог- четт рртого элемента И, гходм угтагюпкн нуля трпт ггра nnieiriif и второго

ТРТ ГГРРП У1Ч19НПГ11ШЯ Т . COPIUlMPHhl

с входом гброгп первою слчигопого рггигтра, второй выход которого сое- ДИНР г яифопмлпиоплькт входами первого трш геря унравлрния тяпнсью и триггрр-з оппрделенчя чгт-нечет и с пррпмч входом пчтого элемента И, пыход 1 спорого ГОРДИНРН г информационным входом припру упр.-пшенич чтением, второй ихоа пятого элемента И соединен г верным гыхсн ом и информационным xo Jo l Tpi геря оппеирленип чет-исчс--1, т i -ч ход которого соединен г входом второго трип ера Mpai ni inisi ттцг-ьт, тякти- руигдце входы грит i мюг правления

I UlHi b n ii i ВЫ/OJ UM т-рнррэ -

торл i di т ir тьг пп, п пд установки нули погано г чч r jpa мфавпе нн я чапио IT ip/i входом сброса /гт| i n i, п Ч ьход п°рS;M л

ротч) ТПРПРНТа И оедпНРП Г ТТРрВЫМ

входом унр.Ч ченнп записью матричногч накопи ГР.ЧЯ и выходом первого триггера управления ч.шигыо, второй вход

5

второго элемента И соединен с вторым входом управпрния записью матричного накопителя и выходом второго триггера упрау-мтя т.мшсыо , выход

0 третьего сдвигового регистра соединен с входом vrтапопки нуля триггера управления чтением.

2.Устройство по п,1, о т л и - ч а го щ е е с я тем, что матричный

5 накопитель выпопнен на ячейках аналоговой памяти с двойной блокировкой информации по входу и двойной выборкой по выходу и разделен а две подматрШ ы, в первой нз кото 0 ых расположено п/2 ячеек аналоговой памяти, а во второй - п ячеек аналоговой памяти.

3.Устройство по п.1, о т л и 5 чающееся тем, что ячейка

аналоговой памяти с двойной блокировкой информации на входе и двойной выборкой на выходе содержит входные ключи, ключ сброса, накопио тельный элемент на конденсаторе,

истоковые повторители, выходные ключи и генрратор тока, выход ко.торого соединен с первым входом питания первого исто ового повторителя, входы пнтанцч енрраюра тока и второй и третий входы питания первого исто- кового повторителя соединены с тинами питания ячейки аналоговой памяти, информационный вход первого входного

Q ключа является информационным входом ячейки аналоговой памяти, вход управления первого ключа является такти- ругацим входом ячейки аналоговой памяти, выход первого входного ключа

с соединен с информационным входом второго, управляющий вход которого является первым входом управления записью ячейки аналоговой памяти, выход второго входного ключа соеднQ ней с входом истокового повторителя и одной нз обкладок конденсатора, другая обкладка которого соединена с одной из ганн питания, выход первого истокового повторителя соединен

g с входом второго, выход которого соединен с информационными входами первого и второго выходных ключей, управляющие входы которых являются входами управления чтением ячейки

5

диалоговой памяти, выход лторого выходного ключа является пнходом ячейки аналогоной памяти, упрянляю- щий вход ключа сброса пгляется входом разрешения обращения ячейки аналоговой памяти, выход второго входо1 ri I ri 7 V}

ИОГО КТЧОМа СОРДНЧГН {- ННфорМ.Щ.

пхпдом ключа cfipor;i, пыхпп рои1;- 1 соединен с другом обкллдк П торя, пход интячнч второго меток пого попторитопи СОРДИПРИ г одним ич пхопов питания пррного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для контроля интегральных блоков памяти | 1980 |

|

SU877622A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в регистрирующей электронной аппаратуре для измерения аналоговых сигналов. Цель изобретения - уменьшение аппаратт-ix средств. Поставпенная цель достигается введением первого и второго триггеров управления записью, триггера управления чтением, элемента И, триггера определения чет-нечет и формирователя сигналов, а также тем, что матричный накопитель выполнен на ячейках аналоговой памяти с двойной блокировкой информации по входу и двойной выборкой по выходу и разделен на две подматрицы, причем ячейка аналоговой памяти содержит входные ключи, ключ сброса, накопительный элемент на конденсаторе, ттоко- вые повторители, выходные ключи и генератор тока, 2 э.п. ф-лы, 2 ил. (Л

Фие.Г

И /7

BY/

to(i+ - fi) I

т

ня

LgS

| Application Notes, AN 201 Parallel Ane los Memory, Analutek LTD, May, 1986, California | |||

| Авторское свидетельство СССР № 1196957, кл | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1991-09-07—Публикация

1988-04-04—Подача