сл tc

о 4; со со

одновибратор 14, элемент И 16, Сущность изобретения состоит в том, что расширение области применения устройства для имитации .неисправностей достигается путем расширения множества имитируемых неисправностей неисправностями константа О и Дребезг.

увеличения мощности множества тактов вьтолнения команды, на которых имитируются неисправности заданного типа, имитирования неисправностей на множестве детермиронанных или случайных тактов выполнения команд, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для программного управления | 1988 |

|

SU1520480A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Устройство для имитации неисправностей | 1989 |

|

SU1755283A1 |

| Устройство для сопряжения эвм с каналами связи | 1984 |

|

SU1229766A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах отладки для оценки поведения цифровых вычислительных машин при определенных неисправностях или сериях неисправностей. Целью изобретения является расширение области применения устройства путем увеличения размерности множества имитируемых неисправностей и их формирования в заданные такты выполнения команды. Она достигается путем введения триггеров типа тактов 5, типа константы 6, типа неисправности 7, генераторов 8,9 случайных двоичных последовательностей, мультиплексоров 11,12, коммутатора 13, второго одновибратора 15. Устройство для имитации неисправностей также содержит регистр 1 адреса, регистр 2 маски, счетчик 3 тактов, триггер 4 режима, схему 10 сравнения, одновибратор 14, элемент И 16. Сущность изобретения состоит в том, что расширение области применения устройства для имитации неисправностей достигается путем расширения множества имитируемых неисправностей неисправностями константа "О" и "дребезг", увеличения мощности множества тактов выполнения команды, на которых имитируются неисправности заданного типа, имитирования неисправностей на множестве детермированных или случайных тактов выполнения команд. 4 ил.

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах отладки для оценки поведения цифровых вычислитель ных машин при определенных неисправностях или сериях неисправностей, что необходимо при отработке оборудования и программ, выполняющих контроль и диагностирование ЦВМо

Цель изобретения - расширение об ласти применения устройства путем расширения множества имитируемых неис- правностей и их формирования в заданные такты вьтолнения команды.

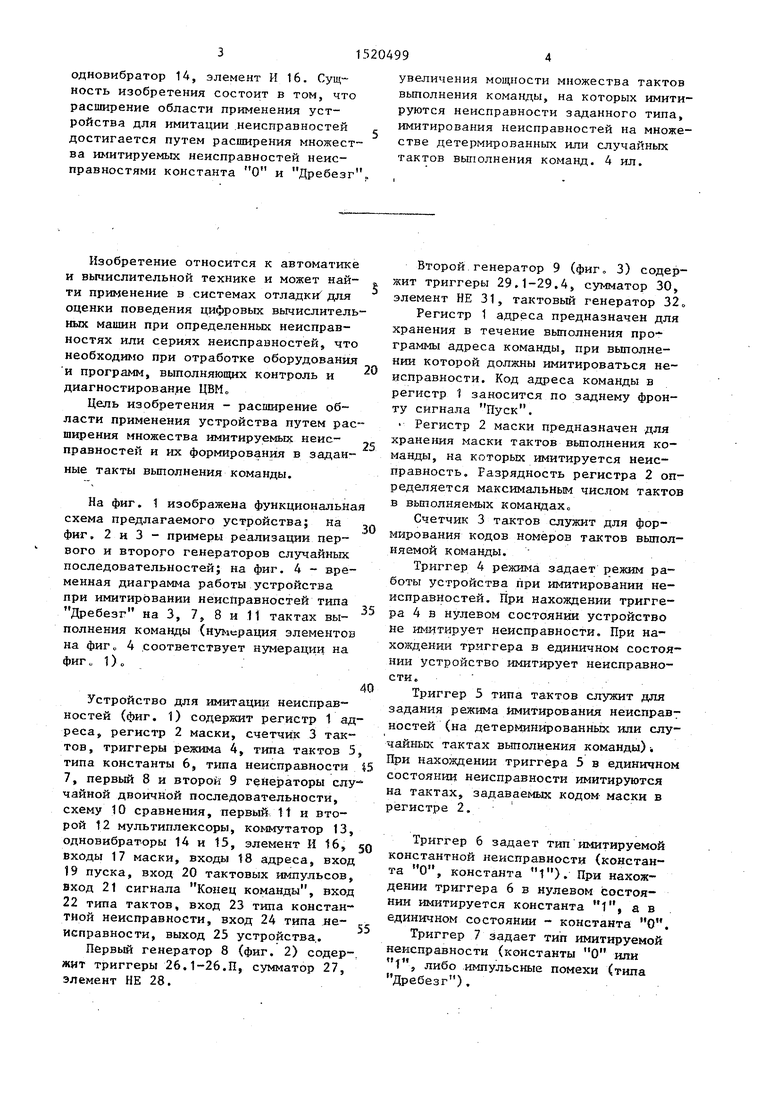

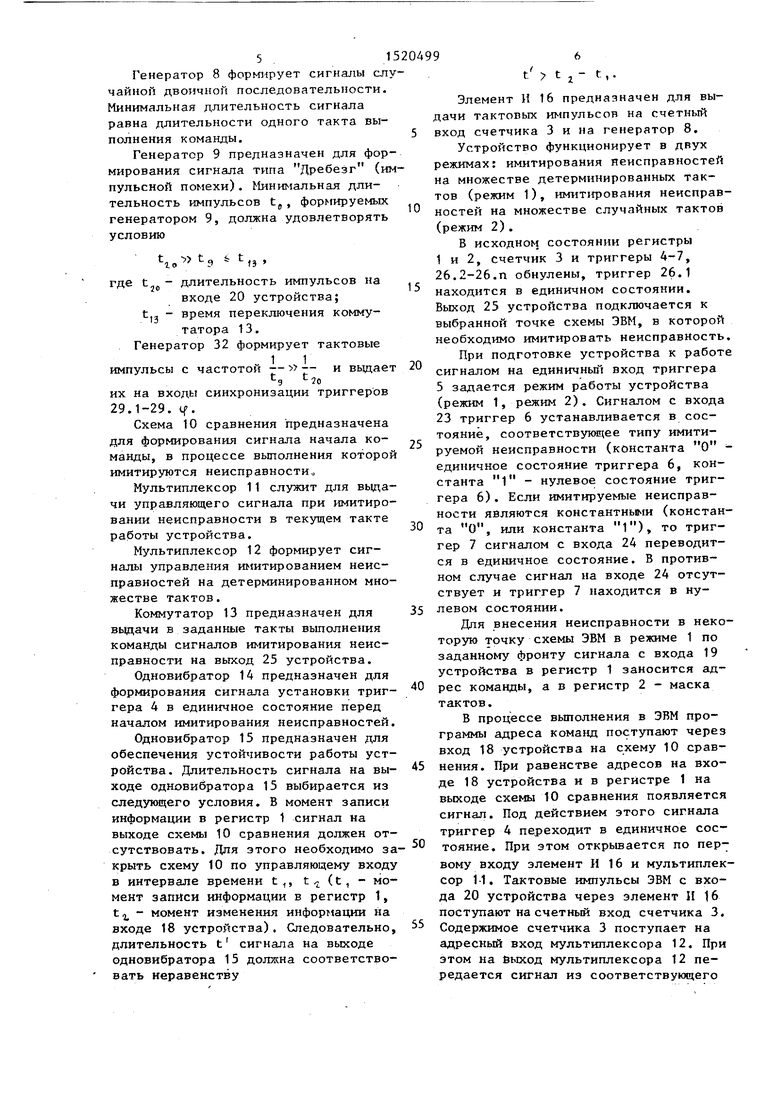

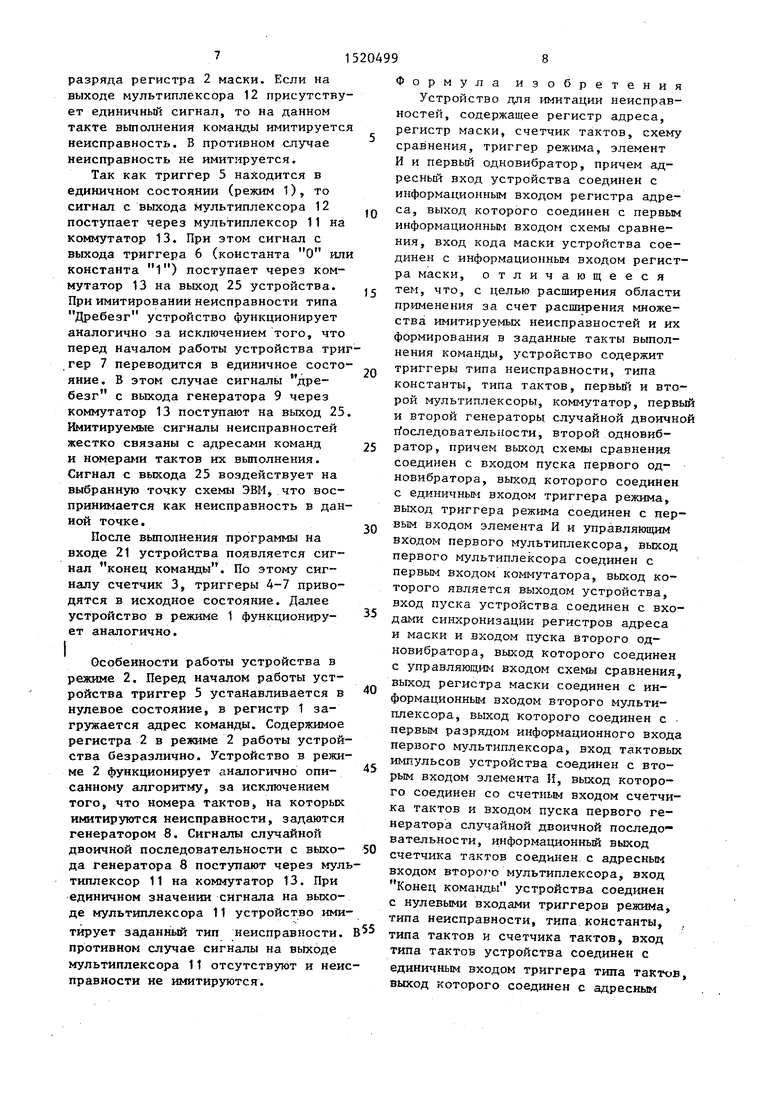

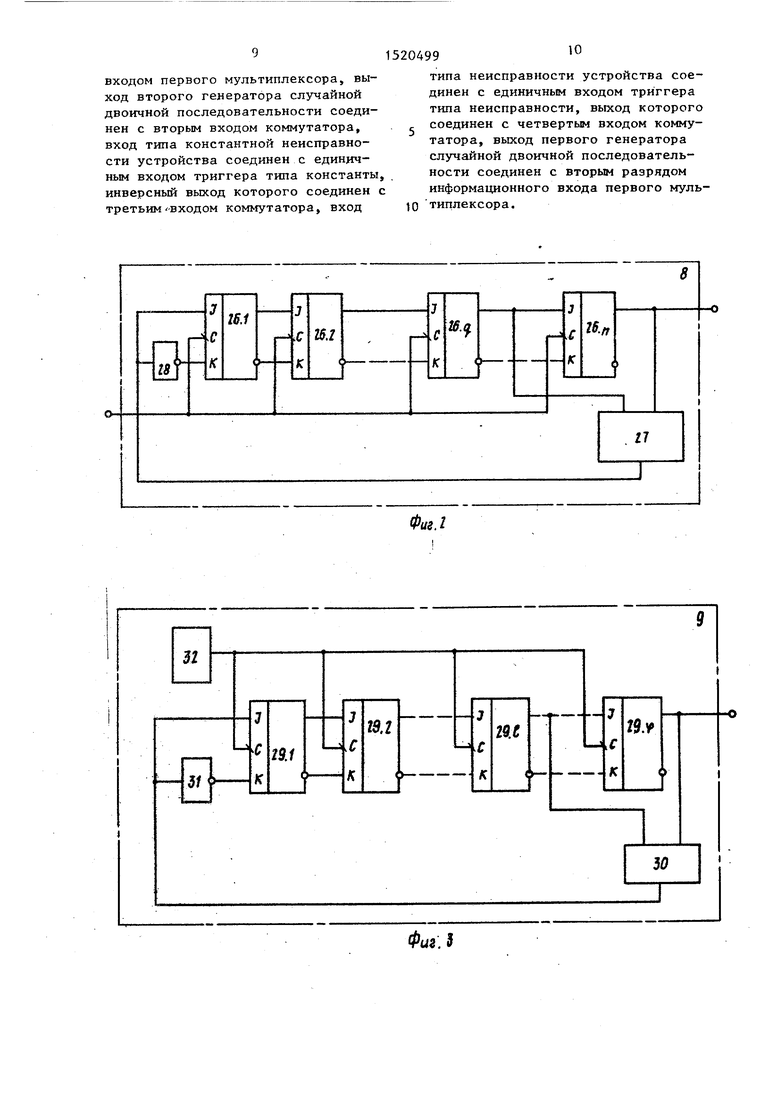

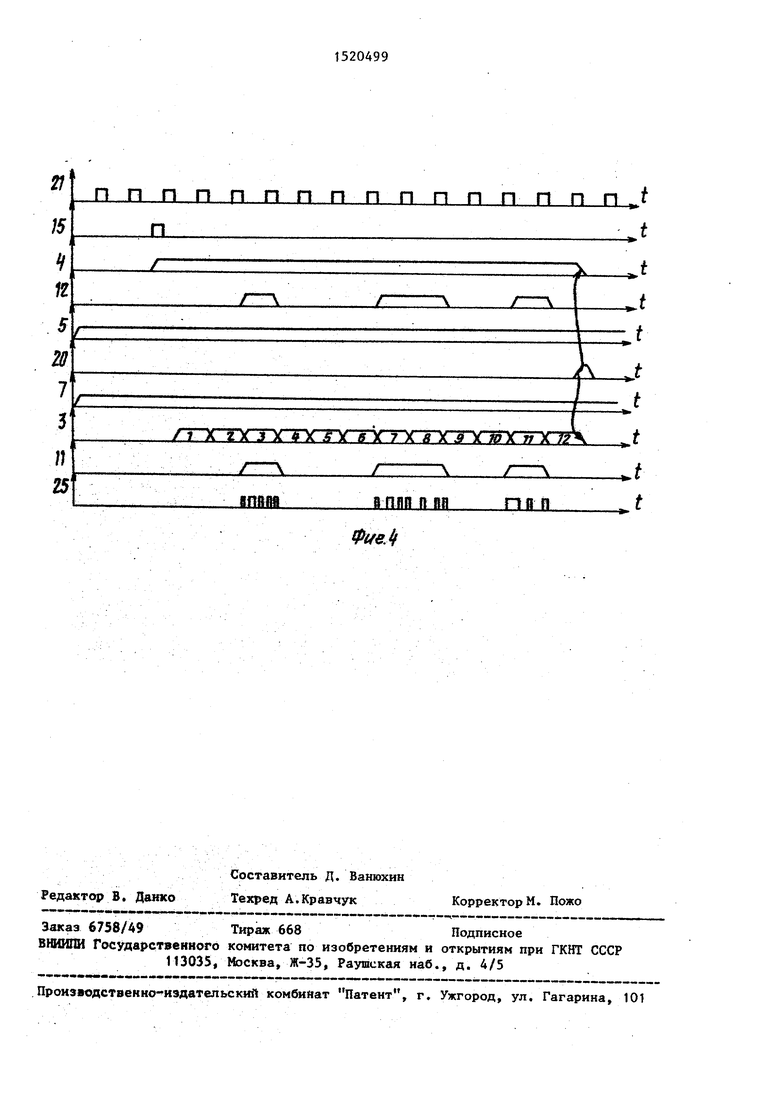

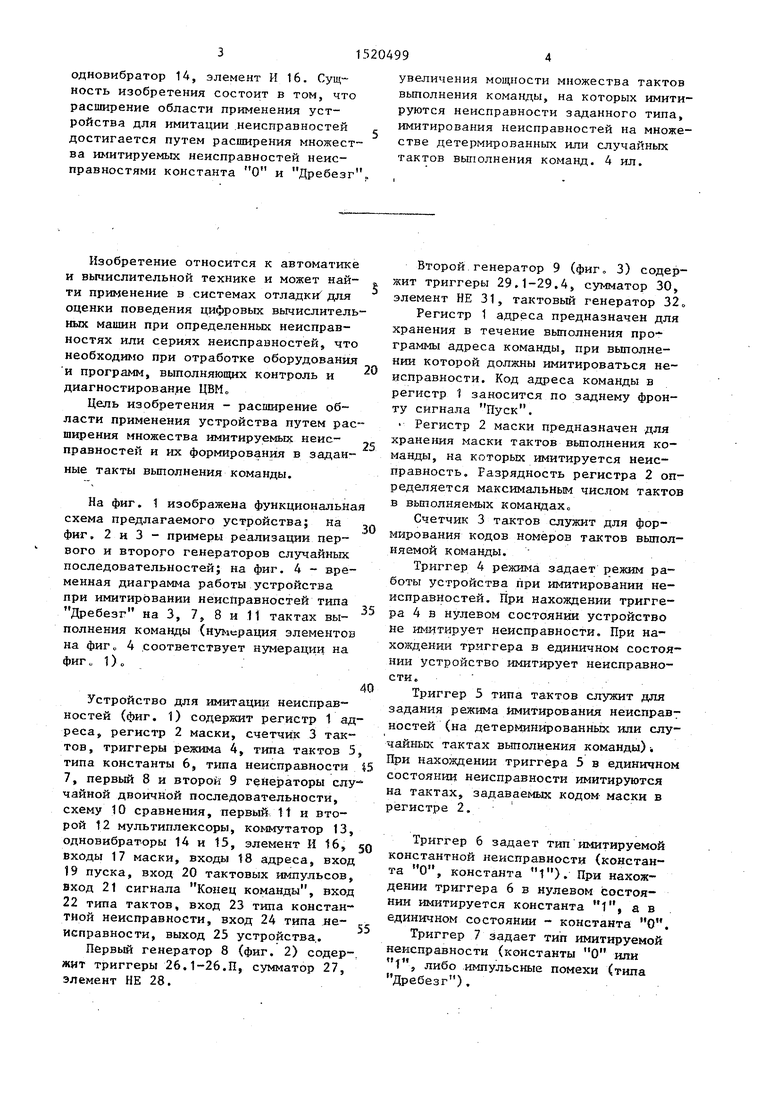

На фиг. 1 изображена функциональная схема предлагаемого устройства; на ,,, фиг, 2 и 3 - примеры реализации первого и второго генераторов слзгчайных последовательностей; на фиг. 4 - временная диаграмма работы устройства при имитировании неисправностей типа дребезг на 3, 7, 8 и 11 тактах выполнения команды (ну 1ерация элементов на фиг„ 4 соответствует нумерации на Фиг„ 1)о

35

40

Устройство для имитации неисправностей (фиг. 1) содержит регистр 1 адреса, регистр 2 маски, счетчик 3 тактов, триггеры режима 4, типа тактов 5, типа константы 6, типа неисправности 15 7, первый 8 и второй 9 гене раторы слу чайной двоичной последовательности, схему 10 сравнения, первый 11 и второй 12 мультиплексоры, коммутатор 13, одновибраторы 14 и 15, элемент И 16, jg входы 17 маски, входы 18 адреса, вход 19 пуска, вход 20 тактовых импульсов, вход 21 сигнала Конец команды, вход 22 типа тактов, вход 23 типа константной неисправности, вход 24 типа не- исправности, выход 25 устройства..

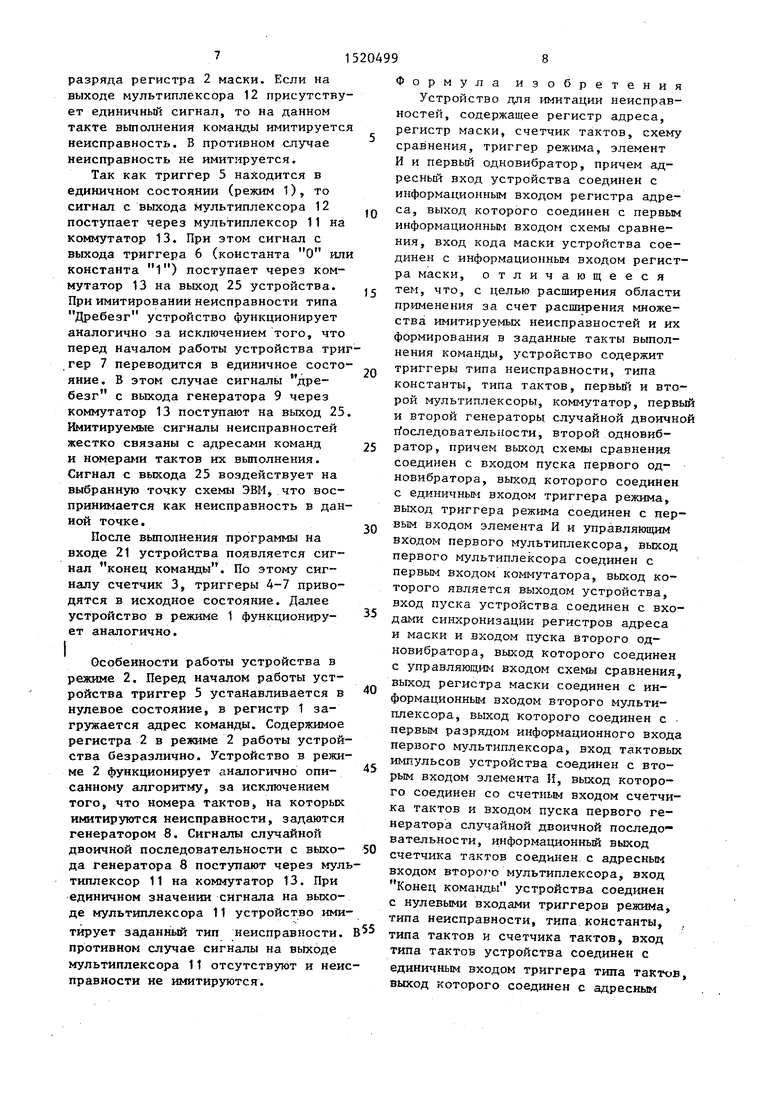

Первый генератор 8 (фиг. 2) содер-, жнт триггеры 26.1-26.П, сумматор 27, элемент НЕ 28.

S

0

,,

5

0

5 g

Второй генератор 9 (фиг 3) содержит триггеры 29.1-29.4, сумматор 30, элемент НЕ 31, тактовый генератор 32„

Регистр 1 адреса предназначен для хранения в течение вьтолнения граммы адреса команды, при вьтолне- нии которой должны имитироваться неисправности. Код адреса команды в регистр 1 заносится по заднему фронту сигнала Пуск, Регистр 2 маски предназначен для хранения маски тактов выполнения команды, на которых имитируется неисправность. Разрядность регистра 2 определяется максимальным числом тактов в вьшолняемых командах

Счетчик 3 тактов служит для формирования кодов номеров тактов выполняемой команды. .

Триггер 4 режима задает режим работы устройства при имитировании неисправностей. При нахождении триггера 4 в нулевом состоянии устройство не имитирует неисправности. При нахождении триггера в единичном состоянии устройство имитирует неисправности. .

Триггер 5 типа тактов служит для задания режима имитирования неисправностей (на детерминированных или случайных тактах выполнения команды) . При нахождении триггера 5 в единичном состоянии неисправности имитируются на тактах, задаваемых кодом маски в регистре 2.

Триггер 6 задает тип имитируемой константной неисправности (константа О, константа l). При нахождении триггера 6 в нулевом состоянии имитируется константа 1, а в единичном состоянии константа О.

Триггер 7 задает тип имитируемой неисправности (константы О или либо импульсные помехи (типа Дребезг).

Генератор 8 сигналы случайной двоичной последовательности. Минимальная длительность сигнала равна длительности одного такта выполнения команды.

Генератор 9 предназначен для формирования сигнала типа Дребезг (импульсной помехи). Минимальная длительность импульсов tj, формируемых генератором 9, должна удовлетворять условию

t t

f3

где t - длительность импульсов на

входе 20 устройства; t,j - время переключения коммутатора 13. Генератор 32 формирует тактовые

импульсы с частотой - - и вьздае

9 0

их на входы синхронизации триггеров 29.1-29. tf.

Схема 10 сравнения предназначена для формирования сигнала начала команды, в процессе вьтолнения которо имитируются неисправностио

Мультиплексор 11 служит для вьща чи управляющего сигнала при имитировании неисправности в текущем такте работы устройства.

Мультиплексор 12 формирует си1- налы управления имитированием неисправностей на детерминированном множестве тактов.

Коммутатор 13 предназначен для вьщачи в заданные такты выполнения команды сигналов имитирования неисправности на выход 25 устройства.

Одновибратор 14 предназначен для формирования сигнала установки триггера 4 в единичное состояние перед началом имитирования неисправностей

Одновибратор 15 предназначен для обеспечения устойчивости работы устройства. Длительность сигнала на выходе Одновибратора 15 выбирается из следующего условия. В момент записи информации в регистр 1 сигнал на выходе схемы 10 сравнения должен отсутствовать. Для этого необходимо закрыть схему 10 по управляющему входу в интервале времени t,, t (t, - момент записи информации в регистр 1, t - момент изменения информации на входе 18 устройства). Следовательно, длительность t сигнала на выходе одновибратора 15 должна соответствовать неравенству

Г. t , t,

0

5

0

5

0

5

0

5

0

5

Элемент И 16 предназначен для выдачи тактовых импульсов на счетный вход счетчика 3 и на генератор 8.

Устройство функционирует в двух режимах: имитирования неисправностей на множестве детерминированных тактов (режим 1), имит1фования неисправностей на множестве случайных тактов (режим 2).

В исходном состоянии регистры 1 и 2, счетчик 3 и триггеры 4-7, 26.2-26.п обнулены, триггер 26.1 находится в единичном состоянии. Выход 25 устройства подключается к выбранной точке схемы ЭВМ, в которой необходимо имитировать неисправность.

При подготовке устройства к работе сигналом на единичньш вход триггера 5 задается режим работы устройства (режим 1, режим 2). Сигналом с входа 23 триггер 6 устанавливается в состояние, соответствукнцее типу имитируемой неисправности (константа О - единичное состояние триггера 6, константа 1 - нулевое состояние триггера 6). Если имитируемые неисправности являются константньВ Ш (константа О, или константа 1), то триггер 7 сигналом с входа 24 переводится в единичное состояние. В противном случае сигнал на входе 24 отсутствует и триггер 7 находится в нулевом состоянии.

Дпя внесения неисправности в некоторую точку схемы ЭВМ в режиме 1 по заданному фронту сигнала с входа 19 устройства в регистр 1 заносится адрес команды, а в регистр 2 - маска тактов.

В процессе вьтолнения в ЭВМ программы адреса кома1Щ поступают через вход 18 устройства на схему 10 сравнения. При равенстве адресов на входе 18 устройства и в регистре 1 на выходе схемы 10 сравнения появляется сигнал. Под действием этого сигнала триггер 4 переходит в единичное состояние. При этом открьшается по первому входу элемент И 16 и мультиплексор 1-1. Тактовые импульсы ЭВМ с входа 20 устройства через элемент И 16 поступают на счетный вход счетчика 3. Содержимое счетчика 3 поступает на адресный вход мультиплексора 12. При этом на йыход мультиплексора 12 передается сигнал из соответствующего

разряда регистра 2 маски. Если на выходе мультиплексора 12 присутствует единичный сигнал, то на данном такте вьшолнения команды имитируется неисправность. В противном случае неисправность не имитируется.

Так как триггер 5 находится в единичном состоянии (режим 1), то сигнал с выхода мультиплексора 12 поступает через мультиплексор 11 на коммутатор 13. При этом сигнал с выхода триггера 6 (константа О или константа 1) поступает через коммутатор 13 на выход 25 устройства. При имитировании неисправности типа Дребезг устройство функционирует аналогично за исключением того, что перед началом работы устройства триг гер 7 переводится в единичное состояние, В этом случае сигналы дребезг с выхода генератора 9 через коммутатор 13 поступают на выход 25. Имитируемые сигналы неисправностей жестко связаны с адресами команд и номерами тактов их вьтолнения. Сигнал с выхода 25 воздействует на выбранную точку схемы ЭВМ, что воспринимается как неисправность в данной точке.

После вьтолнения программы на входе 21 устройства появляется сигнал конец команды. По этому сигналу счетчик 3, триггеры 4-7 приводятся в исходное состояние. Далее устройство в режиме 1 функционирует аналогично.

Особенности работы устройства в режиме 2. Перед началом работы устройства триггер 5 устанавливается в нулевое состояние, в регистр 1 загружается адрес команды. Содержимое регистра 2 в режиме 2 работы устройства безразлично. Устройство в режиме 2 функционирует аналогично опи- санному алгоритму, за исключением того, что номера тактов, на которых имитируются неисправности, задаются генератором 8. Сигналы случайной двоичной последовательности с выхо- да генератора 8 поступают через мультиплексор 11 на коммутатор 13. При единичном значении сигнала на выходе мультиплексора 11 устройство имитирует заданный тип неисправности. противном случав сигналы на выходе мультиплексора 11 отсутств5пот и неисправности не имитируются.

0

5

0

5

0

5

0 5 0 S

Формула изобретения Устройство для имитации неисправностей, содержащее регистр адреса, регистр маски, счетчик тактов, схему сравнения, триггер режима, элемент И и первый одновибратор, причем ад- ресньй вход устройства соединен с информадиоиным входом регистра адреса, выход которого соединен с первым информационным входом схемы сравнения, вход кода маски устройства соединен с информационным входом регистра маски, отличающееся тем, что, с целью расширения области применения за счет расширения множества имитируемых неисправностей и их формирования в заданные такты выполнения команды, устройство содержит триггеры типа неисправности, типа константы, типа тактов, первьп и второй мультиплексоры, коммутатор, первый и второй генераторы случайной двоичной последовательности, второй одновибратор , причем вькод схемы сравнения соединен с входом пуска первого од- новибратора, выход которого соединен с единичньш входом триггера режима, выход триггера режима соединен с первым входом элемента И и управляющим входом первого мультиплексора, выход первого мультиплексора соединен с первым входом коммутатора, выход которого является выходом устройства, вход пуска устройства соединен с входами синхронизации регистров адреса и маски и входом пуска второго одновибратор а, выход которого соединен с управляющим входом схемы сравнения, выход регистра маски соединен с ин- формационньм входом второго мультиплексора, выход которого соединен с первым разрядом информационного входа первого мультиплексора, вход тактовьш импульсов устройства соединен с вторым входом элемента Н, выход которого соединен со счетным входом счетчика тактов и входом пуска первого генератора случайной двоичной последовательности, информационный выход счетчика тактов соединен с адресным входом второго мультиплексора, вход Конец команды устройства соединен с нулевыми входами триггеров режима, типа неисправности, типа константы, типа тактов и счетчика тактов, вход типа тактов устройства соединен с единичным входом триггера типа тактов, выход которого соединен с адресным

входом первого мультиплексора, выход второго генератора случайной двоичной последовательности соединен с вторым входом коммутатора, вход типа константной неисправности устройства соединен с единичным входом триггера типа константы, инверсньй выход которого соединен с третьим ВХОДОМ коммутатора, вход

520499

типа неисправности устройства соединен с единичным входом триггера типа неисправности, выход которого соединен с четвертым входом коммутатора, выход первого генератора случайной двоичной последовательности соединен с вторым разрядом информационного входа первого муль- 0 типлексора.

2f /5

П П П П П П П П П П П П П П П П i

3

/7 л г)ГТУТУ ТУ ЖТ Т)

П 25

t

anflfM a пни it тn я n .

i

t

ф1/еЛ

| Патент США 4156132, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Устройство для имитации неисправностей цифровой вычислительной машины | 1982 |

|

SU1016787A1 |

Авторы

Даты

1989-11-07—Публикация

1987-09-04—Подача